Please Log In for full access to the web site.

Note that this link will take you to an external site (https://shimmer.mit.edu) to authenticate, and then you will be redirected back to this page.

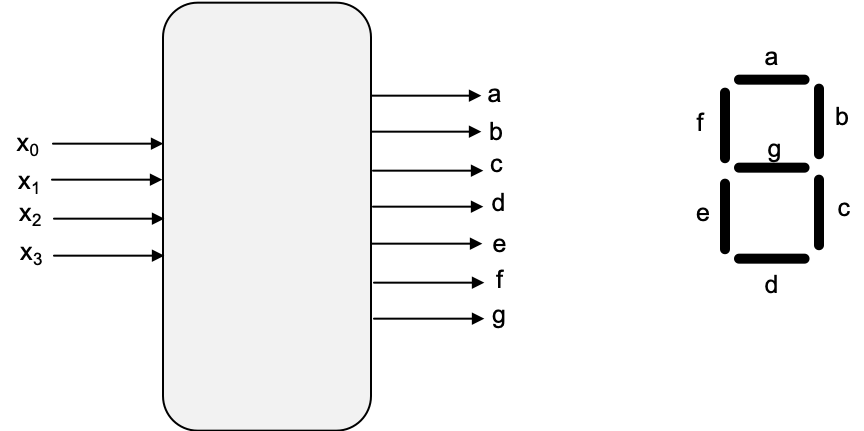

A 4-bit binary-to-seven-segment decoder takes a 4-bit binary number x_3 x_2 x_1 x_0 as input and produces seven outputs, one for each “segment” in a standard seven-LED display. The input will be wrapped into the value [3:0] x_in.

Given the appropriate binary input (where the input represents a number 0 through 15, inclusive), this decoder produces outputs that light up the display in the following manner:

One could actually derive a circuit for this functionality using standard logic gates. But that’s missing the whole point of a Hardware Description Language (HDL) like Verilog, and isn't really even what would happen on an FPGA anyways. One cleaner approach is to first define a variable for each of the 16 numbers (0 through F)...

// array of bits that are "one hot" with numbers 0 through 15

logic [15:0] num;

// true when x_in is 4'b0000

assign num[0] = ~x_in[3] && ~x_in[2] && ~x_in[1] && ~x_in[0];

// true when x_in i 4'b0001

assign num[1] = ~x_in[3] && ~x_in[2] && ~x_in[1] && x_in[0];

// a different way. 4'd2 is 4'b0010;

assign num[2] = x_in == 4'd2;

// this is equivalent to ~x_in[3]&&~x_in[2]&&x_in[1]&&~x_in[0];

// ...

assign num[15] = x_in == 4'd15;

With these values at our disposal, we then use a "sum of products" to control each of the seven segments. Complete the lines of Verilog below to make the system work properly.

When we say "sum of products" what we mean is specify the value on each individual output bit as a "sum" (the logical ||) of individual logic checks (the "products"). If one were use this with an example of specifying days when we have lecture for 6.205 we'd say:

//assuming sunday - saturday are one-bit values that go high on their specific day

assign lecture_day = tuesday || thursday; //lecture_day is high on a day we have lecture

Pay attention to the size of your sum! For "sparse" truth tables with only a few logical high outputs, a regular sum of products is fine. For "dense" truth tables with only a few logical low outputs, we can use negative logic to write less! Expanding on the example above, if I were to code a value that is high for days I sleep too little I could do:

always_comb begin

too_little_sleep = sunday || monday || tuesday || wednesday || thursday;

end

Or I could do:

always_comb begin

too_little_sleep = ~(friday || saturday);

end

The sum of products friday || saturday is not what we want, and that's fine. It is NOT what we want. so let's just use the NOT of it. Now that is what we want.

The module above is a little annoying, since chances are the outputs sa through sg will almost always be used together. We might as well merge them into one unified bus such that s_out = [sg, sf, se, sd, sc, sb, sa];. Update bto7s so that there is only one 7-bit output bus called s_out.