# Piano Man FPGA Piano-Playing Robot

Brendan Ashworth, Max Hardy, & Anthony Nardomarino 12/11/2019

# **Table of Contents**

| 1 Abstract                                                     | 3  |

|----------------------------------------------------------------|----|

| 2 Design                                                       | 3  |

| 2.0 Block Diagram                                              | 3  |

| Figure 2.0.a: Piano-Playing Robot FPGA Block Diagram           | 3  |

| 2.1 Signal Processing Logic (Max)                              |    |

| Figure 2.1.a: Generated Spectrogram Example                    | 5  |

| Figure 2.1.b: Onset Peak Detection Example                     | 6  |

| Figure 2.1.c: Frequency Prominence Thresholding                | 7  |

| 2.2 Fast Fourier Transform (Max & Anthony)                     | 7  |

| 2.3 Spectrogram (Brendan & Max)                                | 8  |

| Figure 2.3.a: Implemented VGA Frequency Amplitude Map          | 8  |

| 2.4 Start-End Detector (Brendan)                               | 9  |

| 2.5 Music Storage (Brendan)                                    | 9  |

| 2.6 Music FSM (Brendan)                                        | 9  |

| 2.7 Synchronization & Timing (Anthony)                         | 10 |

| Figure 2.6.a: Bit Mapping of Key Values in the Chromatic Scale | 11 |

| 2.8 Serial Communications (Anthony)                            | 11 |

| 2.9 Motor Controls (Max & Anthony)                             | 12 |

| Figure 2.8.a: Mechanical Configuration of Motor Mount Hands    | 14 |

| 3 Implementation                                               | 14 |

| 4 Review & Future Development                                  | 15 |

| 5 Parts/Hardware                                               | 16 |

| 5.1 Nexys 4 DDR FPGA                                           | 16 |

| 5.2 ESP32                                                      | 17 |

| 5.3 Sennheiser e935 Condenser Microphone                       | 17 |

| 5.4 MG90S Tower Pro Servo Motors                               | 18 |

| 5.5 Input Amplification Circuit (Max & Anthony)                | 18 |

| Figure 5.5.a: Input Analog Amplification Circuit               | 18 |

| 5.6 3D Printed PLA Motor Mount "Hand"                          | 19 |

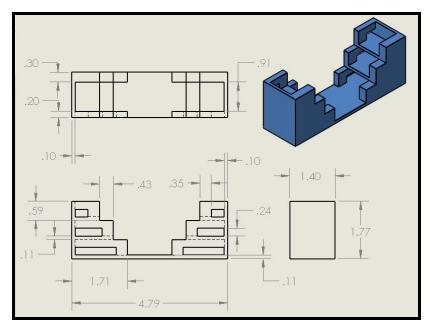

| 5.6.1 Motor Mount                                              | 19 |

| Figure 5.6.1.a: Motor Mount Hand Dimensions (in.)              | 19 |

| 5.6.2 Acrylic Fingers                                          | 19 |

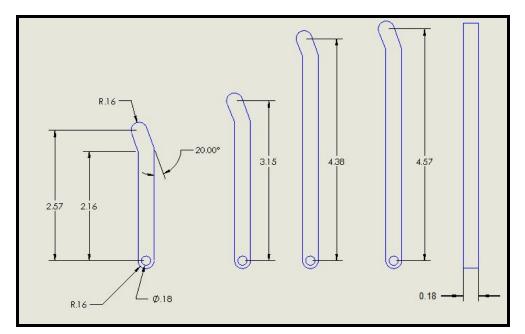

| Figure 5.6.2: Acrylic Laser-Cut Finger Dimensions (in.)        | 20 |

| 6 Appendix                                                     | 21 |

| 6.1 Associated FPGA SystemVerilog                        | 21 |

|----------------------------------------------------------|----|

| 6.1.1 fft.sv (Max, Anthony, Brendan)                     | 21 |

| 6.1.2 fft_spectrogram.sv (Brendan)                       | 27 |

| 6.1.3 freqKeyMap.sv (Anthony)                            | 30 |

| 6.1.4 mega_clk_div.sv (Brendan)                          | 31 |

| 6.1.5 music_storage.sv (Brendan)                         | 31 |

| 6.1.6 serial_tx.sv (Anthony)                             | 33 |

| 6.1.7 serialToKey.sv (Anthony)                           | 34 |

| 6.1.8 start_end_detector.sv (Brendan)                    | 36 |

| 6.1.9 fsm.sv (Brendan)                                   | 38 |

| 6.1.10 onset_detector.sv (Max)                           | 41 |

| 6.1.11 peak_detector.sv (Max)                            | 41 |

| 6.2 Associated ESP32 C++                                 | 42 |

| 6.3 Associated Signal Processing Simulation Python (Max) |    |

## **1 Abstract**

A good piano partner is often hard to come by, and with the help of a Nexys 4 DDR FPGA board, we can show the reigns of the keyboard to a robotic companion. Our goal was to build a sound processing system as well as a robotic mechanism, able to be actuated to reproduce the processed sounds on a keyboard. The keyboard is in an anchored location to eliminate the need for vision capabilities, while emphasizing the robot's ability to reproduce operator-played chords and melodies on the same keyboard as an operator. This project will showcase the ability to create a state machine with listening and playing capabilities, involving analyzing playable frequencies and creating a strategy for playing reproducible chords and melodies using controlled motorized fingers.

## 2 Design

## 2.0 Block Diagram

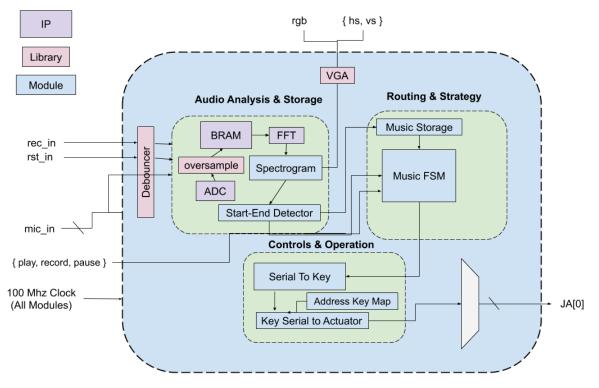

Figure 2.0.a: Piano-Playing Robot FPGA Block Diagram

As seen in Figure 2.0.a, the FPGA Piano-Playing Robot operates under the cooperation of several different modules responsible for different aspects of the system's logic. Debouncing mechanical inputs such as push-buttons is vital for the clean operation of the FSM (2.5) given what they represent.

As soon as the record button is pressed and held, a new state of operation is entered in which the feed from the microphone analog circuit is sampled and stored to BRAM, where windows of the continuous audio feed are independently sent through a Fast Fourier Transform (2.1) operation to later be stitched together in a new state (after detecting peaks with the Spectrogram (2.2)) and to be stored in Music Storage (2.4).

After this process, the Finite State Machine is able to control the release of this data into a feed that can be read according to the rhythm to which it was recorded (within the resolution of a predetermined "beat-clock") (2.5). In this state, the feed is sent on to the controls block in the form of a 12x30n bitmap, where n is the frequency of the chosen beat-clock. Each bit in the list of 12-bit values represents the activation of a specific note in the chromatic scale, to then be sent on to the controls block to readjust its current activation state.

The Synchronization & Timing block (2.6) then keeps track of the release of information by keeping its own internal clock consistent with the rate of the serial communication protocol of the ESP32, referencing each bit's relation to a specific motor address, held in the Address Key Map Lookup table, and sending that particular address if that particular motor's note was to be active in that state of operation.

Finally, the ESP32 motor driver manages the received serial information by counting a maximum of 12 bytes as input (according to the 12 possible addresses) before actuating the motors to which those address bytes correspond. During the playback state of the Finite State Machine, those notes are then sent on a loop at the positive edge of the "beat-clock" for the stored time that those notes are to be active.

## 2.1 Signal Processing Logic (Max)

The signal processing logic required for the project was extensively researched. While the fast Fourier transform was always the backbone of the approach, there were several variations on the downstream analysis of the spectral information which varied in accuracy and complexity.

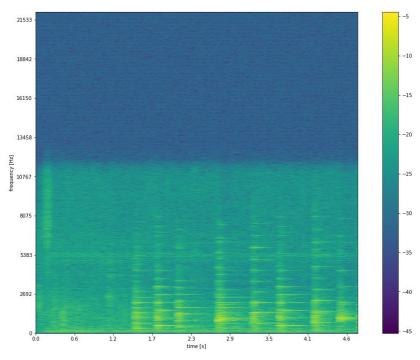

Figure 2.1.a: Generated Spectrogram Example

The figure above is a spectrogram generated during simulations performed in Python. The horizontal axis represents time, while the vertical shows frequency. It is generated by applying FFTs to 'windows' of audio input. This approach is powerful because it gains information in the frequency domain, while retaining information in the time domain - both of which are important in music. Various window sizes were tried, as increasing window size increases frequency resolution at the cost of speed.

Many strategies for note detection were attempted in Python Simulations. Initial approaches included functions which searched for power surges during note onsets, followed by various algorithms for selecting relevant notes at such onsets. Such approaches recorded all audio, performed all FFTs, found all onsets, and found all corresponding notes sequentially.

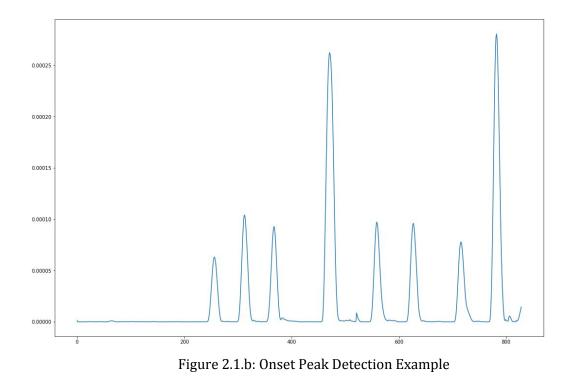

The above figure illustrates peaks which signify potential note onsets from the previous spectrogram. At such peaks, the relevant time step is recorded, then logic is needed to determine which note or notes were activated at that time step from the stored spectrogram. At this stage, several algorithms were attempted to determine relevant notes. This approach was highly accurate and capable of capturing nuances in music, but cumbersome to implement in Verilog. This approach was effective for slower processing rates and relied heavily on large storage space, which would not utilize the strengths of the FPGA - speed and not storage.

The FPGA was fast enough to produce spectral information in near real time, even with substantial window sizes. In other words, it was fast enough to process all audio as it arrived (not the case in a Python simulation), so there would be little need for large amounts of stored information to process retroactively. Because of this, a more basic approach was chosen in which a simple, customizable power threshold determined activated notes in real time. This was significantly simpler to implement in digital logic.

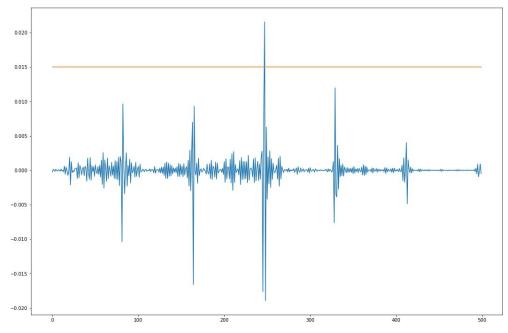

Figure 2.1.c: Frequency Prominence Thresholding

The above image is a simulation of what the FPGA would do, in which the horizontal axis represents frequency, and the vertical axis represents power. Essentially, the FPGA would take a real time FFT and search for any spectral bands that broke a power threshold (orange line). Because spectral power levels tend to oscillate over the course of a ringing note, a refractory period was built in that would prevent a note from activating many times over the course of a single ring. This approach would take advantage of the strengths of the FPGA and be relatively easy to implement.

## 2.2 Fast Fourier Transform (Max & Anthony)

The FFT was provided by the Verilog IP Core. The team integrated the core with the BRAM such that the FFT operated on audio samples stored in BRAM, and output the spectral information in a different BRAM. An FFT window size of 16384 was used for high resolution spectral information. Larger window sizes require longer computations, but provide higher resolution between notes - i.e. adjacent notes are separated by more bins in the spectral histogram. The output of the FFT was cut down substantially before being stored in the BRAM. Only the lowest 1024 bins were stored, as most of the higher frequency bins were not relevant to music or even in the range of human hearing. FFT window size and stored window size were chosen after repeated testing both in Python simulations, as well as in verilog.

## 2.3 Spectrogram (Brendan & Max)

The spectrogram displays the current Fourier Transform in the frequency domain on a VGA output monitor attached to the FPGA. The spectrogram also completes the role of fundamental frequency analysis, where it determines the activations of certain notes within in octave.

The VGA spectrogram shows the lowest 256 bins of an 8192-sample Fourier Transform, which has enough information to display the majority of frequencies present along the range of a piano (it loses the top few keys). Colored based on their power activations, with red showing many decibels and yellow showing background noise, one can dynamically see the frequency analysis of the incoming audio input on the VGA screen.

Figure 2.3.a: Implemented VGA Frequency Amplitude Map

On the screen, 12 bins are colored green. These bins are the frequencies of the fundamental notes, keys starting at A, A-sharp, B, ... ending at G and G-sharp. There are two horizontal lines that represent a configurable power threshold. When the green bin activations go above the threshold, they are categorized as ON. As long as they are above the threshold, they continue to be on. When the power goes below the threshold, they will continue to be on for a second, before turning off automatically. This allows both full, rich pianos that can generate enough power above the noise threshold to play well, while also smaller electronic keyboards that are harder to detect.

## 2.4 Start-End Detector (Brendan)

Storing all of the notes would be too logic-intensive to synthesize in look-up tables on an FPGA. To compress the notes, we take an effective discrete derivative of the note activations. When the beat clock fires, the Start-End Detector calculates the changes between the current note activations and the previous note activations. If these changes are not negligible, the Start-End Detector notes a change and clocks the delta between the current note and the previous note to the Music Storage module.

The Start-End Detector is the crucial step in compressing music before storing it on the FPGA. When it notes a change, it notes the current timer coming from the Finite State Machine and indexes the change based on that timer. This allows the Finite State Machine to find the relevant changes based on the current playback time as opposed to storing many irrelevant, non-changes in idle time.

## 2.5 Music Storage (Brendan)

The Music Storage module takes clocked input from the Start-End Detector and stores it in a lookup table based on the current count from the Music Finite State Machine. The Music Storage module can store a maximum of 1024 note changes, allowing for a maximum of about 4 minutes of playback on the double-speed FSM clock.

Upon reset (the center button), the Music Storage clears and allows one to re-record from the beginning without reprogramming the FPGA.

## 2.6 Music FSM (Brendan)

The Music Finite State Machine is the core module of the FPGA side of the Piano Playing Robot. The Music FSM implements a Mealy finite state machine that combines inputs from the buttons (center, left, right, and up) with the beat clock and various states that include PLAYING, PAUSED, RECORDING, ANALYZING, and IDLE.

From these states, it sends environment information including whether it's paused, playing, recording, analyzing, or idle, where each is a glitch-free bit window into the state value. Each state can only transition into a number of states based on the inputs, as is a requirement for Mealy FSMs.

The Finite State Machine handles the counter and length calculates for each recorded song. As the beat clock ticks, the counter increments, and when the FPGA transitions from the recording to the analyzing states, the length is set and the counter reset for playback.

Once recording is done, the FSM transitions to the paused state. Pressing the right button transitions it into the play state, while letting go of it pauses it in time. Pressing the play button again returns it to playing where you left off. When the song is done, it resets to the beginning in a loop. One cannot record over a song without resetting the FSM with the center button. Using the top button, one can fast forward through the song, through both playback and recording. This allows the user to have more fine-grained control over the beat clock frequency, allowing either longer songs to be recorded, or faster songs with better resolution.

## 2.7 Synchronization & Timing (Anthony)

As explained in Serial Communications (2.7), Synchronization & Timing is of utmost importance in the development of smooth and responsive controls from the FPGA to the ESP32 motor driver. Interfacing directly with the Finite State Machine (2.5), the serialToKey module receives its playback instructions in such a way to maintain rhythm to a resolution that is compatible with both the Nexys 4's storage and the required time for servo motor actuation.

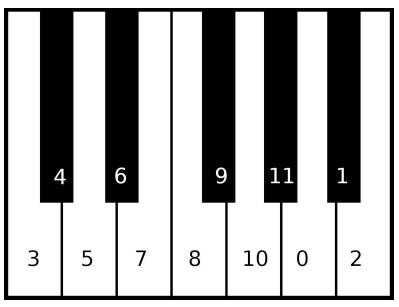

As the Fundamental Isolator (2.3) interacts with the Finite State Machine to store note changes, we compress the incoming data into a form that can capture both single note presses and chords (multiple notes being activated on the piano at the same time) with a multi-hot 12-bit value with each bit corresponding to a note on the chromatic scale (i.e. A, A#, B, C, C#, D, D#, E, F, F#, G, G#).

Figure 2.6.a: Bit Mapping of Key Values in the Chromatic Scale

From here serialToKey is able to iterate through each bit in the 12-bit state value to determine which addresses to send serially between each 115200hz cycle. This is done through an interface with the addressKeyMap lookup table that maps each note's activation state with an 8-bit motor address.

Because the serialToKey module's operations are done on a 100Mhz clock, we can take care of any processing between the receipt of the 12-bit state value and trigger of the serial\_tx send in ample time. If a bit is high, then the address can be received and sent during the next 115200 baud cycle, or else the line will simply stay high, indicating to the ESP that no new serial stream is available, while it still counts that stream as a blank instruction and thus incrementing its internal counter to figure out if the instruction set is complete and ready for actuation.

## 2.8 Serial Communications (Anthony)

Serial communications is one of the most important structures to have solidified in the FPGA Piano-Playing Robot because if the notes calculated from the FFT and signal processing blocks can't reach the motors, then there is no bridge between the FPGA processing and the physical output of the robot. This module involves a sensitive translation between the instructions coming from the Finite State Machine (2.5) and the Motor Controls (2.8), meaning that our compressed playback data needs to be dissected and translated into addresses that the ESP32 will find useful.

Because the ESP32 is capable of easily configurable UART 8N1 serial communications protocol, we could structure the serialToKey module in such a way to act as a median between a 12-bit multi-hot encoding scheme and the serial\_tx module's translation into an 8-bit address. From the Finite State Machine during playback, states of the notes are received for serial processing in the form of a 12-bit sequence given for each time division (determined according to the beat-clock). For example, if the beat-clock is running at 2hz (resolution of playback is an update every 500ms, which was used in the demo), then 30 seconds of playback would be encoded in a 60x12 array of note states, corresponding to their states every half second.

When this 12-bit binary value is sent to the serialToKey module, the timing is handled to produce a 115200 baud, in which time the 12-bit stream can be iterated over to find out which key addresses should be sent through the serial tx module. By determining the intended key state for a given value in time, a correspondence with the addressKeyMap lookup table is established to gather the address of that intended motor. Acting for ten cycles to complete the 8N1 stream, the serial tx stream is given the trigger (dependent on a parallel 115200hz clock in serialToKey) to send the motor address byte until all 12 are sent and the ESP32 can actuate. It does this by setting its input "val" address to a shift register that can then shift in bits according to its own clock compatible with the baud rate, with a default high to provide the end bits, or blank instructions in the case that that particular motor is not to be actuated. However, there may have been a discrepancy in our implementation in how serial communications would work at when taking into considerations the implication of a beat clock, and how instructions are only sent at the rising edge of this clock. This bug caused a failure in simultaneous actuation of keys as well as producing a mechanical error in false instructions, causing certain keys to oscillate between the upward and downward positions.

## 2.9 Motor Controls (Max & Anthony)

The motor controls are managed through an ESP32 microcontroller acting as both a serial receiver for FPGA motor instructions and a motor driver for the Piano Robot's servo array hands. After the Nexys FPGA generates a bitmap of note activations (the time values for which a given note should be playing in order to replicate the input),

that bitmap is sent serially to the ESP32 through a UART 8N1 protocol, controlling the operation of the motors.

On the ESP32 side, actuation of the motors in a stable domain in which chords as well as notes are possible (simultaneous actuation of multiple motors within one beat value). To ensure this, the ESP runs a loop in which it is constantly looking for Serial input, verified by the presence of a serial address being received by a Serial Read function. Because the FSM (2.5) sends a passive high signal over the serial line at 115200 baud in its "play" state, the ESP32 is able to receive these streams and indicate them as an idle stream.

Because of this protocol, the ESP32 is able to detect every 12 adjacent serial transmissions, actuating up to all 12 at the same time. The states of each finger is kept as either a 1 or a 0 (indicating activation and deactivation respectively), and after each serial stream, the old and new states are compared to determine whether a certain finger is required to change states. This ensures that a finger is only pressed when serial instructions are received to keep that finger in the downward position, otherwise it will return back to its raised position.

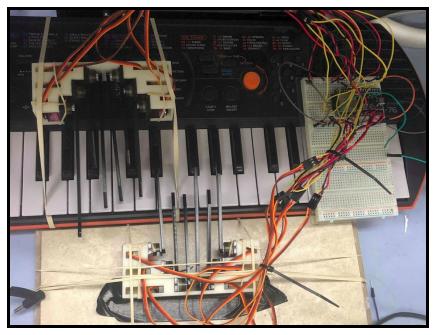

There are several instances in which the team had to test different methods of keeping finger states, different information being sent serially, and implementations of the motor mount's interface with the physical keyboard. Firstly, the physical setup is comprised of the motor mount's securing of 6 servo motors for each hand at about 11mm apart (the rough spacing between keys on the piano). This required precise calculation of angles of depression for actuated fingers as well as lengths of each finger for different key shapes (natural keys and sharps) and their optimal contact locations to reduce stress on the servo motor gears.

The process of measuring resting angles for the two states of the fingers came from trial and error of testing values to ensure that the motors would not stall and draw excess current from pressing the keys, but also sustaining a distance away from the keys in its idle position such that it can actuate within a very short period of time from when it is called to change states. The mount was then mounted to the keyboard with rubber bands to act as a failsafe to motor failure, such that slack can be produced by a sufficiently large angle of depression during the testing phase of the project.

Some of the problems in the design of this system that we would correct upon include the linear nature of servo actuation. For this project, it would be impractical

to add series current sensors to detect stall current draw to stop motors from actuating too far given the time we allotted for the mechanical side; however, an alternative method to prevent overactuation would be to use take advantage of the internal Hall outputs of the MG90S servos to determine if the correct position has been reached by gauging the rotor's permanent magnets. If this position does not match a predetermined range of action, this servo motor can promptly be deactivated or moved back to its idle position. Furthermore, the hand case design with 6 fingers was not originally intended to be mounted to the piano statically, but instead attached to a rack and pinion rail to move around the piano freely to its next location. Of course, this implementation was abandoned for the purposes of this project due to time and material constraints, and our design would have to move forward with a mounting technique in which one hand was mounted above the keys, and one was mounted below, as seen in Figure 2.8.a.

Figure 2.8.a: Mechanical Configuration of Motor Mount Hands

## **3 Implementation**

In implementing the Piano-Playing Robot, our station consists of a playable keyboard for musical input into a microphone, the Finite State Machine controllable from the FPGA's onboard buttons and switches, and the ESP32 driver connected to the servo arrays mounted onto the robot's playback keyboard. Note identification can be controlled with manual switches to set an onset-threshold and tune the identification process to the environment in which the recording is taking place.

In activating the robot, one must press and hold the record button on the FPGA to begin taking in audio data, while there is a musical stimulus to the microphone. During our demonstration, this came from an independant keyboard playing into a microphone. After the preferred recording is complete, the user releases the record button and now has that audio clip saved and processed for playback.

By holding down the playback button, the FPGA will cycle through the divisions in time that it operates under (the beat clock), which can be changed for resolution in rhythm. The notes playing back in this playback mode will be manifested by both mounted LEDs on the FPGA to distinguish notes, as well as a finger from the robot physically pressing the keys of the piano on which it's mounted.

Playback options include fast-forward, pause, and reverse to control the way the robot plays the tune that it just heard. The fingers will move to press keys corresponding to which note should be playing at what time, and release when it is time for the note to end.

## 4 Review & Future Development

In the product's end phase of testing and demonstration, our system proved its ability to detect notes, determine their activity over a period of time of recording, store their states within a single octave, and enter a playback state in which notes could be correctly sent to the motor driver with accuracy in piano-key activation and in the time domain / rhythm. However, a misconception in the process of serial communication with the controls had prevented the perfected demonstration of the Piano-Playing Robot.

A notable bug in the implementation of the robot during demonstration was that although the correct motor addresses and times of activation were received for the note that was intended to be activated, there was an issue with a finger's ability to properly change states. This problem could be recognized by short taps of the keys as well as a constant oscillation between the upward and downward state transition of keys that were intended to be held. This can be explained by a dissonance in the effective note transfer from the FPGA to the ESP32 motor driver through the beat clock. Essentially, between every beat clock, there is an idle high signal sent across the line, which had been considered to be a "nonactivity" signal, and that we could count off 12 of those signals and be ready to actuate, resetting the remaining states. However, in the time between each rising edge of the beat clock, those states reset, making it impossible to detect continuous sustains of notes or time-sensitive changes. In the future, we have learned to first seek out any discrepancies in the ways that different devices handle the same serial data, as there are many ways to get the same data across the same wire.

Furthermore, because a complex and robust mechanical structure of the project was not the primary goal, many design choices came from convenience and affordability. Most notably, this manifested in the rubber-band mount for а pseudo-proprioceptive stress on the servo motors, as well as the use of MG90S servo motors for high speed actuation. Problems that arose from these choices included fingers slipping from the keys, and small debugging errors in which the servos were trying to reach an angle far below the physical piano, drawing excess current and causing stress on its internal gears.

Although the rubber bands allowed for some stress relief in lifting the hands instead of allowing the motors to stall for too long, this is a very ineffective solution, and could be solved by implementing failsafe operations for motor actuation that would take intended and actual position into account, ensuring that the motors have safely reached their position in a feasible amount of time, otherwise overriding them and setting them to an idle state. This could be done by streaming the internal Hall feedback from the servo motors and controlling it according to that feed. However, this feed is not perfect considering the design of these servos to be cost effective.

Finally, an important consideration is the necessity of the ESP32 driver. The design choice was made due to its ease of control decisions and changes, while offering a quick method to debug possible note storage and propagation issues that would have been difficult to catch with an Internal Logic Analyzer or testbench. For this reason, the ESP32 microcontroller makes for an excellent prototyping logic device, but in the design of a more refined and final system, we would look into operating the Pulse Width Modulus states of the servo motors from the FPGA directly to decrease wiring required.

## **5 Parts/Hardware**

### 5.1 Nexys 4 DDR FPGA

The Nexys 4 DDR is the FPGA board at the heart of the 6.111 Digital Systems Lab curriculum, armed with operational tools such as an ADC, VGA capabilities, a seven-segment display, and several switches to debug and operate the Piano Man FPGA Piano-Playing Robot. It is armed with ports for serial communication, specifically used to communicate with the ESP32 as a motor driver and I2C communication device to fully operate the mechanical aspects of the project, as well as being well equipped for temporary Block RAM storage, useful not only for servo motor strategy storage, but also for digital signal processing, at the heart of which lies the Discrete Fast Fourier Transform.

### 5.2 ESP32

The ESP32 Microcontroller was the obvious choice for an external Servo Motor driver, as it has onboard 16 PWM channels, perfect for operating PWM-controlled Servo Motors. It is capable of instantiating up to 3 hardware UART channels, programmable to many different subprotocols; the Piano Man simply communicates with the ESP32 through a singular 8N1 UART Serial port.

Serial communications to the ESP32 involved an I2C-like addressing function, in which the input byte was indicative of a "change" required for a specifically addressed motor. As 8N1 is the default supported protocol for UART serial communications, 12 motors were programmed to actuate when their 8-bit address is read, and return to an idle state hovering above the keyboard if their address is not read during a 12 byte stream. This simplifies the process of programming finger movements by giving the Nexys 4 FPGA board access to the motor array completely serially.

#### 5.3 Sennheiser e935 Condenser Microphone

The Sennheiser e935 Condenser Microphone is a passive transducer manufactured for vocal and acoustic recording. It offers a clean means of recording audio in a specific direction with minimal outside noise, and provides a reliable feed up to a 24-bit depth. It is connected to the FPGA through the "hot" and ground lines from the microphone's XLR port.

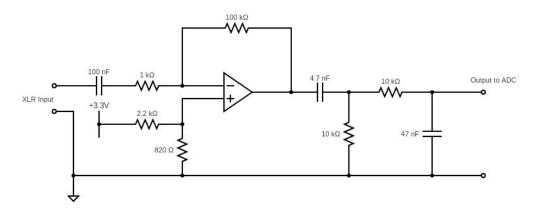

As the passive peak-to-peak voltage maximum for the purposes of this project is around 2.0mV, there was some modification to be done with the signal so that it

provided a readable output to the FPGA's onboard ADC. This is discussed further in <u>5.5 Input Amplification Circuit</u>.

### 5.4 MG90S Tower Pro Servo Motors

The MG90S Tower Pro Servo Motors are excellent prototyping motors for their high torque output for such a small size and mass. They were the perfect contenders for our Piano-Playing Robot for their affordability and versatile mounting capabilities. We used two arrays of 6 servo motors each between two 3D printed motor mount "hands" for operation of a keyboard from an ESP32 driver.

These motors operate within a 180° range by PWM signaling. Programmable within a specific range, a specific duty cycle will map the motor to move to a specific angle associated with it. This range will typically be read within an operation cycle of 50hz, where a 1-2ms duty cycle in a 20ms period will cover the entire 180° range. To decrease the time constraints of motor actuation, the ESP32 only drives each motor as a toggling function between two positions in a 90° range.

## **5.5 Input Amplification Circuit (Max & Anthony)**

Figure 5.5.a: Input Analog Amplification Circuit

To allow the Microphone we used to be readable by the Nexys 4 DDR on-board ADC, it was important that we did some analog signal processing to not only amplify the incoming hot signal, but to also center it around 0.5V so it may be digitized.

This begins with a capacitive coupler into a LT1632 operational amplifier circuit, offset on the positive port with a rough functional voltage divider to get a 0.5V offset from a 3.3V input from the FPGA. From here, the roughly 2.0mV Pk-Pk input voltage

is effectively phase shifted by 180° and amplified to get a 1.0V Pk-Pk amplitude with minimal clipping out of the op-amp. From here, the signal passes through a band-pass filter, allowing frequencies within the frequency response range of the Sennheiser e935 to pass through at full amplitude, while reducing the intensity of frequencies outside of that range. The result is passed on to the Nexys 4 DDR ADC for digitization.

### 5.6 3D Printed PLA Motor Mount "Hand"

#### 5.6.1 Motor Mount

The Motor Mount "hands" were 3D printed in PLA plastic with an 11mm separation between the servo actuators, measured to a standard MIDI keyboard. A small window behind each motor allows for ease of wiring. Printed in the Cypress Engineering Design Studio.

Figure 5.6.1.a: Motor Mount Hand Dimensions (in.)

#### **5.6.2 Acrylic Fingers**

Twelve laser-cut black acrylic fingers were used to press the piano keys in our system, attached to the servo arrays with a dowel-fit insertion, allowing them to sustain pressure without slip. Various sizes were used (ranging from 6.5cm to 12cm) in order to reach each key in an octave and reduce the total torque

requirement of its attached servo motor. Laser cut in the Cypress Engineering Design Studio.

Figure 5.6.2: Acrylic Laser-Cut Finger Dimensions (in.)

## **6** Appendix

## 6.1 Associated FPGA SystemVerilog

#### 6.1.1 fft.sv (Max, Anthony, Brendan)

```

// The main module for the Piano Playing Robot

// built on an FPGA.

// Team: Brendan Ashworth, Max Hardy, Anthony Nardomarino

// December 9 2019

module piano_playing_robot (

CLK100MHZ,

// ADC and VGA.

VGA R, VGA B, VGA G,

VGA_HS, VGA_VS,

AD3P, AD3N,

// Inputs

SW, BTNC, BTNU, BTNL, BTNR, BTND,

// 8-segment display

SEG, AN,

// Lights

LED16_B, LED16_G, LED16_R,

LED17 B, LED17 G, LED17 R,

LED,

// Outputs to microcontroller

JA

);

// inputs

input logic CLK100MHZ;

input [15:0] SW;

input logic BTNC;

input logic BTNU;

input logic BTNL;

input logic BTNR;

input logic BTND;

input logic AD3P;

input logic AD3N;

// outputs

output logic [3:0] VGA R;

output logic [3:0] VGA_B;

output logic [3:0] VGA_G;

output logic VGA HS;

output logic VGA VS;

output logic LED16 B, LED16 G, LED16 R;

output logic LED17 B, LED17 G, LED17 R;

output [15:0] LED;

output [7:0] SEG;

output [7:0] AN;

```

```

output [7:0] JA;

// Split the 100mhz clock into lower and higher frequencies.

// ADC takes 104mhz, VGA takes 65mhz.

logic clk 104mhz, clk 65mhz;

clk wiz 0 clockgen(

.clk in1(CLK100MHZ),

.clk out1(clk 104mhz),

.clk out2(clk 65mhz));

logic hsync, vsync, blank;

logic [10:0] hcount;

logic [9:0] vcount;

xvga xvgal(

.vclock(clk 65mhz),

.hcount (hcount),

.vcount (vcount),

.vsync(vsync),

.hsync(hsync),

.blank(blank));

logic BTNC clean, BTNU clean, BTND clean, BTNL clean, BTNR clean;

debounce #(.COUNT(5)) db0 (

.clk(clk 104mhz),

.reset(1'b0),

.noisy({BTNC, BTNU, BTND, BTNL, BTNR}),

.clean({BTNC clean, BTNU clean, BTND clean, BTNL clean, BTNR clean}));

// Full system reset.

logic system reset;

assign system reset = BTNC clean;

logic [15:0] adc sample;

logic eoc;

// Sample audio input from the ADC.

// Taken with inspiration from the nexys fft ddr demo.

xadc demo xadc demo (

.dclk in(clk 104mhz), // Master clock for DRP and XADC.

.di in(0),

// DRP input info (0 becuase we don't need to write)

.daddr_in(6'h13),

// The DRP register address for the third analog input register

// DRP enable line high (we want to read)

.den in(1),

.dwe in(0),

// DRP write enable low (never write)

// DRP ready signal (unused)

.drdy out(),

.do_out(adc_sample), // DRP output from register (the ADC data)

.reset in(system reset),

.vp in(0),

// dedicated/built in analog channel on bank 0

// can't use this analog channel b/c of nexys 4 setup

.vn in(0),

// The third analog auxiliary input channel

.vauxp3(AD3P),

// Choose this one b/c it's on JXADC header 1

.vauxn3(AD3N),

.channel out(),

// Not useful in sngle channel mode

.eoc out(eoc),

// Pulses high on end of ADC conversion

// Not useful

.alarm out(),

// End of sequence pulse, not useful

.eos out(),

.busy out()

// High when conversion is in progress. unused.

);

```

// Increase sampling fidelity by oversampling 16x.

```

// Taken from the FFT demo.

logic [13:0] osample16;

logic done osample16;

oversample16 osamp16 1 (

.clk(clk 104mhz),

.sample(adc sample[15:4]),

.eoc(eoc),

.oversample(osample16),

.done(done osample16));

// This BRAM stores the FFT frame that was last generated.

// This is before we process via FFT and then take the usable part of the spectrogram.

logic [13:0] frame head = 0; // Frame head - a pointer to the write point, works as

circular buffer

logic [13:0] frame addr;

// Frame address - The read address, controlled by

bram to fft

logic [15:0] frame data;

// Frame data - The read data, input into bram to fft

bram frame bram1 (

.clka(clk 104mhz),

.wea(done osample16),

.addra(frame head),

.dina({osample16, 2'b0}),

.clkb(clk 104mhz),

.addrb(frame addr),

.doutb(frame_data));

// On every sample, increase the frame head pointer.

// It'll overflow back when we take enough samples.

always @(posedge clk 104mhz) if (done osample16) frame head <= frame head + 1;

// The FFT can be taken much faster than we take it, but because we only care about

// visible and human readable frequencies, let's use one thats more reasonable.

// The VGA vsync happens about every 60hz so we can use that.

// This logic converts it to a single clock pulse.

logic vsync 104mhz, vsync 104mhz pulse;

synchronize vsync synchronize0(

.clk(clk 104mhz),

.in(vsync),

.out(vsync 104mhz));

level to pulse vsync ltp0(

.clk(clk 104mhz),

.level(~vsync 104mhz),

.pulse(vsync_104mhz_pulse));

// Read frames from the BRAM and pipe it to the FFT.

logic last missing; // All these are control lines to the FFT block design

logic [31:0] frame_tdata;

logic frame tlast, frame tready, frame tvalid;

bram to fft bram to fft 0(

.clk(clk 104mhz),

.head(frame head),

.addr(frame addr),

.data(frame data),

.start(vsync 104mhz pulse),

.last missing(last missing),

.frame tdata(frame tdata),

```

```

.frame tlast(frame tlast),

.frame_tready(frame_tready),

.frame tvalid(frame tvalid)

);

// We take an FFT with 16384 samples each of 16 bit depth. This logic

// sends it to the FFT IP to get the magnitudes of each frequency.

logic [23:0] magnitude tdata;

logic [13:0] magnitude tuser;

logic magnitude tlast, magnitude tvalid;

fft mag fft mag i(

.clk(clk 104mhz),

.event tlast missing(last missing),

.frame tdata(frame tdata),

.frame tlast(frame tlast),

.frame tready(frame tready),

.frame tvalid(frame tvalid),

// Scaling isn't necessary.

.scaling(12'b0000 0000 0000),

.magnitude tdata(magnitude tdata),

.magnitude tlast(magnitude tlast),

.magnitude tuser(magnitude tuser),

.magnitude tvalid(magnitude tvalid));

// We use a huge number of samples into our FFT (~16k), but we only care

// about the lowest of bins. This is because they contain the fundamental

// frequencies of piano notes spaced far enough apart to be distinguishable.

// This only store to BRAM when it's the lowest eighth.

logic fft is lowest chunk;

assign fft is lowest chunk = ~ |magnitude tuser[13:10];

// Store a single window of FFT in BRAM, with 1024 bins x 16 bit depth.

// log2(1024) => 10 bit address space

logic [9:0] fft bin index;

// 16 bit depth describes the magnitude of the frequency in that bin

logic [15:0] fft magnitude;

bram fft fft windows (

.clka(clk 104mhz),

.clkb(clk 104mhz),

.wea(fft is lowest chunk & magnitude tvalid),

// Writing port.

.addra(magnitude tuser[9:0]),

.dina(magnitude tdata[15:0]),

// Reading port.

.addrb(fft_bin_index),

.doutb(fft magnitude)

);

// These are the currently activated notes, updated every 60hz.

logic [11:0] notes;

// We allow for a range of thresholds for the audio analysis because

// of the wide variability in piano volume and outside noise. Take

// it from the switches.

logic [15:0] threshold;

assign threshold = SW[15:0];

// The spectrogram both shows the spectrogram on the

```

```

// VGA port and also isolates fundamental notes from it

// to pass to the finite state machine and start end detector.

fft spectrogram spectrogram(

.vclk in(clk 65mhz),

.hcount(hcount), .vcount(vcount), .blank(blank),

.hsync(hsync), .vsync(vsync),

.rgb({VGA R, VGA G, VGA B}),

.fft bin index(fft bin index),

.fft magnitude(fft magnitude),

.hsync out(VGA HS),

.vsync out(VGA VS),

.notes(notes),

.threshold(threshold)

);

// Beat clock. How quickly the notes can change.

logic music clk;

// Assign RGB LEDs

assign {LED16 R, LED16 G, LED16 B} = {2'b00, music clk};

// The number of note changes we need to uniquely identify

// to play the entirety of the song.

parameter NUM CHANGES = 1024;

logic is recording;

logic fast forward;

assign fast forward = BTNU clean;

mega clk div mega clk div0(

.fast forward(fast forward),

.clk in(clk 65mhz),

.clk out(music clk));

logic backwards;

assign backwards = BTND clean;

// interop between the start end detector

// and the music storage.

logic [11:0][1:0] note change;

logic [$clog2(NUM_CHANGES)-1:0] note_change_index;

logic note clk;

// Playback on the LEDs.

start end detector detector0(

.rst in(system reset),

.activated notes in(notes),

.note_clk_in(music_clk & is_recording),

.note change out(note change),

.note change index out (note change index),

.note change clk out(note clk)

);

// Counter is the time, seq ptr is the index.

logic [$clog2(NUM CHANGES)-1:0] counter;

logic [$clog2(NUM CHANGES)-1:0] ptr;

```

```

25

```

```

display 8hex display(

.clk(clk 65mhz),

.data({6'b0, ptr[9:0], 6'b0, counter[9:0]}),

.seg(SEG[6:0]),

.strobe(AN));

assign SEG[7] = 1;

// Assign RGB LEDs

\ensuremath{{\prime}}\xspace // Print debugging states to the LEDs.

logic is playing;

logic paused out;

assign {LED17 R, LED17 G, LED17 B} = {is recording, is_playing, paused_out};

// For displaying the current state on the FPGA.

logic [3:0] state;

fsm fsm0(

.clk in(music clk),

.rst in(system reset),

.fft_done(1'b1),

.state out(state),

.counter(counter),

.recording_in(BTNL_clean), .playing_in(BTNR_clean),

.playing_out(is_playing), .recording_out(is_recording), .paused_out(paused_out));

logic [NUM CHANGES-1:0][$clog2(NUM CHANGES)-1:0] notes indexes;

logic [NUM CHANGES-1:0][11:0] notes stored;

logic [NUM CHANGES-1:0][11:0] notes on;

logic note clk with reset;

assign note clk with reset = note clk | system reset;

music storage music storage0(

.rst in(system reset),

.notes on(notes on),

.note change in (note change),

.note change index in (note change index),

.note change clk in (note clk with reset),

.notes stored(notes stored),

.notes indexes(notes indexes));

logic [15:0] led proxy;

assign LED[11:0] = led_proxy[11:0];

assign LED[15:12] = state[3:0];

logic fft clk;

assign fft_clk = music_clk | system_reset;

always ff @(posedge fft clk) begin

if (system_reset) begin

ptr <= 0;

led proxy[11:0] <= 12'b0;</pre>

// If recording.

end else if (is recording) begin

led proxy[11:0] <= notes[11:0];</pre>

// If playing.

```

```

end else if (is playing) begin

// Play out the notes onto the LEDs.

led proxy[11:0] <= notes on[ptr];</pre>

// allow for playing backwards

if (backwards) begin

// backwards lookup

// Check the next pointer.

if ((notes indexes[ptr - 1] >= counter) & (notes indexes[ptr - 1] > 0))

ptr <= ptr - 1;

11

else if (counter < ptr)

11

ptr <= 0;

end else begin

// regular order

// Check the next pointer.

if ((notes indexes[ptr + 1] <= counter) & (notes indexes[ptr + 1] > 0))

ptr <= ptr + 1;

else if (counter < ptr)

ptr <= 0;

end

// If paused.

end else if (paused out) begin

// Keep the notes.

led proxy[11:0] <= notes_on[ptr][11:0];</pre>

end else begin

led proxy[11:0] <= 12'b0;</pre>

end

end

assign JA[7:1] = 7'b0;

logic [11:0] interest note;

11

11

assign interest note = notes stored[ptr];

logic data output pin;

assign JA[0] = ~(~data output pin & is playing);

serialToKey hands (.clk 100mhz(CLK100MHZ), .rst(system reset),

.data out(data output pin),

.beat_clk(fft_clk), .pb(is_playing), .interest_note(notes_on[ptr]));

```

endmodule

#### 6.1.2 fft\_spectrogram.sv (Brendan)

```

// Generates a visual spectrogram that contains

// VGA-generating display logic. This augments

// the audio output to provide another way to

// look at what the robot is doing.

// This also contains the fundamental note isolator/

// note recognition module. I merged the two to

// simplify note identification.

// Author: Brendan Ashworth

module fft_spectrogram(

vclk_in,

// VGA output

hcount, vcount, blank,

```

```

hsync, vsync,

rqb,

hsync out, vsync out,

// note identification

fft bin index,

fft magnitude,

notes,

threshold

);

// Fixed screen parameters.

parameter SCREEN HEIGHT = 767;

parameter SCREEN HEIGHT HALF = 383;

parameter SCREEN WIDTH = 1023;

input logic vclk in;

input [10:0] hcount;

input [9:0] vcount;

input logic blank;

input logic hsync;

input logic vsync;

output logic [11:0] rgb;

output logic hsync out;

output logic vsync out;

input logic [15:0] threshold;

output [9:0] fft bin index;

input [15:0] fft magnitude;

// old

logic [9:0] hheight;

logic [9:0] vheight;

logic [1:0] intensity;

parameter [27:0] NOTE ACTIVATION = 28'd33 500 000;

// COLORS is the color spectrum that we use to generate the spectrogram.

// This makes it visually pleasing but not computationally or space

// intensive.

parameter [11:0] COLOR RED = 12'hD11;

parameter [11:0] COLOR ORANGE = 12'hF84;

parameter [11:0] COLOR YELLOW = 12'hFD0;

parameter [11:0] COLOR_BLACK = 12'h000;

logic [27:0] A = 0;

logic [27:0] As = 0;

logic [27:0] B = 0;

logic [27:0] C = 0;

logic [27:0] Cs = 0;

logic [27:0] D = 0;

logic [27:0] Ds = 0;

logic [27:0] = 0;

logic [27:0] F = 0;

logic [27:0] Fs = 0;

logic [27:0] G = 0;

logic [27:0] Gs = 0;

output logic [11:0] notes;

assign notes = {A > 0, As > 0, B > 0, C > 0, Cs > 0, D > 0, Ds > 0, E > 0, F > 0, Fs >

0, G > 0, Gs > 0;

```

```

// cooldown of 9.75*10^7

always ff @(posedge vclk in) begin

// We pipeline to allow for some computation, so

// delay all logics equally.

hheight <= fft magnitude >> 7;

vheight <= SCREEN HEIGHT - vcount;</pre>

// Intensity depends on the FFT magnitude.

intensity <= {hheight > 210, hheight > 20};

{hsync out, vsync out} <= {hsync, vsync};

rgb <= blank ? COLOR BLACK :</pre>

(vheight == SCREEN HEIGHT HALF + threshold) ? 12'hFFF :

(vheight == SCREEN HEIGHT HALF - threshold) ? 12'hFFF :

// First, filter out what shouldn't be colored.

// Center the spectrogram on half screen height.

(vheight > (SCREEN_HEIGHT_HALF + hheight)) ? COLOR_BLACK :

(vheight < (SCREEN HEIGHT HALF - hheight)) ? COLOR BLACK :

// Now do it based on intensity.

// Color our fundamental frequencies specially.

((fft bin index == 210) | (fft bin index == 187) | (fft bin index == 166) |

(fft_bin_index == 147) | (fft_bin_index == 131) | (fft_bin_index == 117)) ? 12'hOFO :

((fft_bin_index == 222) | (fft_bin_index == 197) | (fft_bin_index == 175) |

(fft bin index == 155) | (fft bin index == 139) | (fft bin index == 125)) ? 12'hOFO :

// Otherwise, just color according to how strong it is.

(intensity[1]) ? COLOR RED :

(intensity[0]) ? COLOR ORANGE :

COLOR YELLOW;

// If a note is on, we "empty the bucket" progressively,

// until the note turns off.

if (A > 0)

A <= A - 1;

if (As > 0)

As <= As - 1;

if (B > 0)

B <= B - 1;

if (C > 0)

C <= C - 1;

if (Cs > 0)

Cs <= Cs - 1;

if (D > 0)

D <= D - 1;

if (Ds > 0)

Ds <= Ds - 1;

if (E > 0)

E <= E - 1;

if (F > 0)

F <= F - 1;

if (Fs > 0)

Fs <= Fs - 1;

if (G > 0)

G <= G - 1;

if (Gs > 0)

Gs \leq Gs - 1;

// If a note is above our threshold, we reset

// its activation, "filling the bucket".

if (fft bin index == 117 \& A == 0)

A <= (hheight > threshold) ? NOTE ACTIVATION : 0;

if (fft_bin_index == 125 \& As == 0)

As <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 131 & B == 0)

B <= hheight > threshold ? NOTE_ACTIVATION : 0;

```

```

if (fft bin index == 139 & C == 0)

```

```

C <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 147 & Cs == 0)

Cs <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 155 & D == 0)

D <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 166 & Ds == 0)

Ds <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 175 \& E == 0)

E <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft_bin_index == 187 \& F == 0)

F <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 197 & Fs == 0)

Fs <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 210 & G == 0)

G <= hheight > threshold ? NOTE ACTIVATION : 0;

if (fft bin index == 222 & Gs == 0)

Gs <= hheight > threshold ? NOTE ACTIVATION : 0;

end

// We fit 256 bins on the screen. This makes each bin

// wide enough to see, but small enough that we can fit

// our octave of interest on the screen.

assign fft_bin_index = hcount[9:0] >> 2;

```

endmodule

#### 6.1.3 freqKeyMap.sv (Anthony)

```

11

// freqKeyMap.sv

// Anthony Nardomarino

// FPGA Piano Playing Robot

// MIT 6.111 Digital Systems Lab

// 11-15-2019

11

module addressKeyMap(

countIn, addrOut

);

```

```

input logic [3:0] countIn;

output logic [7:0] addrOut;

11

i2c Address Key:

11

// 0100_0000 - A

0101 0000 - C# 0100 1000 - F

0011_0000 - D 0010_1000 - F#

0111_0000 - D# 0110_1000 - G

// 0010 0000 - A#

// 0110 0000 - B

// 0001 0000 - C

0000 1000 - E 0001 1000 - G#

always comb begin

case(countIn)

4'd0:

addrOut = 8'b0100 0000;

addrOut = 8'b0010 0000;

4'd1:

4'd2:

addrOut = 8'b0110 0000;

addrOut = 8'b0001 0000;

4'd3:

```

| 4'd4:    | addrOut = 8'b0101_0000; |

|----------|-------------------------|

| 4'd5:    | addrOut = 8'b0011_0000; |

| 4'd6:    | addrOut = 8'b0111_0000; |

| 4'd7:    | addrOut = 8'b0000_1000; |

| 4'd8:    | addrOut = 8'b0100_1000; |

| 4'd9:    | addrOut = 8'b0010_1000; |

| 4'd10:   | addrOut = 8'b0110_1000; |

| 4'd11:   | addrOut = 8'b0001_1000; |

| default: | addrOut = 8'b1111_1111; |

| endcase  |                         |

| end      |                         |

endmodule // freqKeyMap

#### 6.1.4 mega\_clk\_div.sv (Brendan)

```

// The beat clock generator.

// Allows for fast-forward with the fast forward

// input, taken from button up.

// Author: Brendan Ashworth

module mega clk div(

fast forward,

clk_in,

clk_out);

logic [23:0] mid = 0;

input logic fast_forward;

input logic clk in;

output logic clk out;

// mid[22] will be twice the speed

assign clk out = fast forward ? mid[22] : mid[23];

always ff @(posedge clk in) begin

mid <= mid + 1;

```

#### endmodule

end

#### 6.1.5 music\_storage.sv (Brendan)

```

// The music storage module stores all recorded note changes

// as a two-dimensional logic array. It's from this music storage

// module that the music FSM reads and loads notes to send

// to the controls modules.

// Author: Brendan Ashworth

module music storage(

rst in,

note_change_in,

note_change_index_in,

note_change_clk_in,

notes on,

notes stored,

notes indexes);

input logic rst in;

// Clocked in when a note change is found by the start_end_detector.

input logic note_change_clk_in;

```

```

// This is the number of fundamental notes / frequencies

// that the piano can play. This is a result of applying

// the fundamental isolator on the activated frequencies in

// the Fourier transform.

parameter NUM NOTES = 12;

// The number of note changes we need to uniquely identify

// to play the entirety of the song. Identical to:

// The number of sequences we need to uniquely identify

// to play the entirety of the song. NUM CHANGES * sample duration

// gives the maximum length of a song

parameter NUM CHANGES = 1024;

// The delta functions that represent changes in

// the activated frequencies. This also includes

// information about the current activated frequency;

// i.e., given a single note change out, you can

// start playing a song at that point.

// For some given frequency, note change out is:

// 00 = no change in activation, off

// 11 = no change, on

// 10 = note turns off

// 01 = note turns on

// note_change_out is designed such that

// note_change_out[0] ^ note_change_out[1]

// signifies that the motors must be actuated in some

// direction specified by note change out[0].

input logic [11:0][1:0] note change in;

// Starting at 0, this is the index for a note change.

// It will increment with every clock and can be used

// to uniquely identify the activated frequencies in

// a song at any point in time.

input logic [$clog2(NUM CHANGES)-1:0] note change index in;

// The actual storage array. We need to store information

// about the notes that change at what time periods.

// This necessitates two logical 2d arrays: one for notes,

// one to index the time periods.

// Activations for each note at a certain time index.

// This is effectively the LSB of note change in across the notes.

output logic [NUM CHANGES-1:0] [11:0] notes stored;

output logic [NUM CHANGES-1:0][11:0] notes on;

// Time indexes for each stored note. For each entry in notes_stored[i], there

// is an equivalent entry in notes indexes[i] that describes the time period at

// which this note change occurs.

output logic [NUM CHANGES-1:0] [$clog2 (NUM CHANGES) -1:0] notes indexes;

// index pointer contains a time index that indicates at which notes location

// we should store the next note. Storing this prevents traversing the logic

// until the notes index[j] == 0, which is conceptually the same.

logic [$clog2(NUM CHANGES)-1:0] index pointer;

```

```

32

```

```

always ff @(posedge note change clk in) begin

integer i;

if (rst in) begin

notes stored <= '{default:'0};</pre>

notes on <= '{default:'0};</pre>

notes indexes <= '{default:'0};</pre>

// Begin writing at t=1.

index pointer <= 1'b1;</pre>

end else begin

// Store the new note.

notes indexes[index pointer] <= note change index in;</pre>

// Store each note activation individually because it comes

// in as a [1:0] but we only care about the LSB.

for (i=0; i < 12; i++) begin

notes stored[index pointer][i] <= note change in[i][0] ^ note change in[i][1];</pre>

notes on[index pointer][i] <= note change in[i][1];</pre>

end

// Increment the pointer.

index pointer <= index pointer + 1'b1;</pre>

end

end

```

#### endmodule

#### 6.1.6 serial\_tx.sv (Anthony)

```

`timescale 1ns / 1ps

11

// serial tx.sv

// Created by: Anthony Nardomarino

// 6.111 - Digital Systems Laboratory

// Piano Playing Robot

// 12-02-2019

11

// Based off of 6.111 Lab 2, in which Serial communications are established

// between a serial python reader and the FPGA. This module takes instructions

// sent by the serialToKey.sv module and sends them via 8N1 UART to an ESP32

// with a precalculated baud of 115200 (100Mhz clock / 868).

11

module serial tx(

clk, reset, trigger, val, data out, is sending//, counter serial

);

input logic

clk;

input logic

reset;

input logic

trigger;

input

logic [7:0] val;

output logic

data out;

output logic

is sending;

11

output logic [7:0] counter serial;

parameter DIVISOR = 868; //4. 115.2 kbps baud divisor from 100Mhz

```

```

logic [7:0] shift buffer;

logic [31:0] counter;

11

assign counter serial = counter[7:0];

logic old trigger;

always ff @(posedge clk) begin

old trigger <= trigger;</pre>

if(reset)begin

is sending <= 0;

counter <= 32'd0;</pre>

shift buffer <= 8'b11111111;</pre>

end else begin

if (trigger & ~old trigger) begin

// take the first edge of the trigger

shift buffer[7:0] <= val[7:0];</pre>

counter <= 32'd0;

is sending

<= 1;

end else if (is sending) begin

counter <= counter + 1;</pre>

case(counter[14:0])

DIVISOR*0: data out <= 1'b0;</pre>

DIVISOR*1: data out <= shift buffer[0];</pre>

DIVISOR*2: data out <= shift buffer[1];</pre>

DIVISOR*3: data_out <= shift_buffer[2];</pre>

DIVISOR*4: data out <= shift buffer[3];</pre>

DIVISOR*5: data out <= shift buffer[4];</pre>

DIVISOR*6: data out <= shift buffer[5];</pre>

DIVISOR*7: data out <= shift buffer[6];</pre>

DIVISOR*8: data out <= shift buffer[7];</pre>

DIVISOR*9: begin

data out <= 1'b1;</pre>

is sending <= 0;

end

endcase

end

end

end

```

```

endmodule

```

#### 6.1.7 serialToKey.sv (Anthony)

```

module serialToKey(

clk 100mhz, rst, data out,

beat clk, pb, interest note

11

debug, counter out, counter serial

);

parameter DIVISOR = 868;

// INPUTs

input logic

clk 100mhz;

input logic

rst;

input logic

beat clk; // slow beat clock from pb (min 2hz, max 10hz)

input logic

pb;

// playback wire

// note of interest (active note according to beat clk)

input logic [11:0] interest note;

// OUTPUTs

output logic data out;

// serial out

11

output logic [24:0] debug;

assign debug = {motor addy, key addy, motor count, trigger, is sending, sending,

11

curr beat, old beat};

output logic [9:0] counter_out;

11

// Internal logic

// 8 bit address of the motor to be actuated

logic [7:0] motor addy;

logic [7:0] key addy;

// 8 bit address of motor of interest,

// specified by value of motor count

logic [3:0] motor count;

// counter to 12 motor streams

logic

trigger;

// trigger to send serial info

logic

is sending;

// trigger from serial to indicate full

serial stream sent

logic

sending;

logic

curr beat;

logic

old beat;

logic [31:0] counter;

11

assign counter_out = counter;

11

output logic [7:0] counter serial;

serial_tx fingers (.clk(clk_100mhz), .reset(rst), .trigger(trigger),

.val(motor addy), .data out(data out), .is sending(is sending)/*,

.counter serial(counter serial)*/);

addressKeyMap motorKey (.countIn(motor count), .addrOut(key addy));

always ff @(posedge clk 100mhz) begin

curr beat <= beat clk;</pre>

<= curr beat;

old beat

if (rst) begin

```

```

trigger <= 0;

sending <= 0;</pre>

motor count <= 4'd0;</pre>

counter <= 0;

// onset of beat clock: send notes

end else if (curr beat & ~old beat & pb) begin

sending

<= 1;

motor count <= 4'd1;</pre>

counter

<= 0;

motor addy <= interest note[11] ? 8'b0100 0000 : 8'b1111 1111;</pre>

end else if (motor count == 12) begin

sending <= 0;</pre>

<= 0;

counter

end else if (sending & (counter==32'd8680)) begin

counter

<= 0;

motor count <= motor count + 1;</pre>

trigger <= 1;</pre>

11

motor count <= ~is sending ? (motor count + 1) : (motor count);</pre>

11

<= is sending;

trigger

motor_addy <= interest_note[11 - motor_count] ? key_addy : 8'b1111_1111;</pre>

end else if (sending) begin

trigger <= 0;</pre>

11

trigger

<= is sending;

counter

<= counter + 1;

end

end

```

endmodule // serialToKey

#### 6.1.8 start\_end\_detector.sv (Brendan)

```

// The start end detector effectively takes the

// derivative of an array of activated frequencies,

// giving the time indices at which they change in value

// (turn off or on). This transforms a step function in

// both directions to delta functions towards negative and

// positive infinity.

// Brendan Ashworth

module start end detector (

rst in,

activated notes in,

note clk in,

note_change_out,

note_change_index_out,

note_change_clk_out

);

\ensuremath{{\prime}}\xspace // This is the number of fundamental notes / frequencies

\ensuremath{{\prime}}\xspace // that the piano can play. This is a result of applying

// the fundamental isolator on the activated frequencies in

// the Fourier transform.

parameter NUM NOTES = 12;

parameter NUM CHANGES = 1024;

input logic rst in;

```

```

// An array of activated notes - a 0 signifies

// the note is off, a 1 is on.

input [11:0] activated notes in;

// note clk in pulses when a new sequence of activated notes

// are introduced.

input logic note clk in;

// The delta functions that represent changes in

// the activated frequencies. This also includes

// information about the current activated frequency;

// i.e., given a single note change out, you can

// start playing a song at that point.

// For some given frequency, note_change_out is:

// 00 = no change in activation, off

// 11 = no change, on

// 10 = note turns off

// 01 = note turns on

// note change out is designed such that

// note_change_out[0] ^ note_change_out[1]

// signifies that the motors must be actuated in some

// direction specified by note_change_out[0].

output logic [11:0][1:0] note_change_out;

// Starting at 0, this is the index for a note change.

// It will increment with every clock and can be used

// to uniquely identify the activated frequencies in

// a song at any point in time.

output logic [$clog2(NUM CHANGES)-1:0] note change index out;

// The activated notes on the last clock pulse.

// The same value as the LSB of note change out for

// all notes.

logic [11:0] last activated notes;

// Whether or not that specific frequency has a change.

// OR ing this entire logic will provide a logical 1 if

// there is a note change detected.

logic [11:0] note has change;

// This clk pulses any time there is a new note_change_out

// available to process.

output logic note change clk out;

always_ff @(posedge note_clk_in) begin

if (rst in) begin

for (integer i = 0; i < 12; i++) begin

note change out[i] <= 2'b00;</pre>

last activated_notes[i] <= 0;</pre>

end

note change index out <= 0;</pre>

note change clk out <= 0;</pre>

end else if (note change clk out) begin

// Turn off the clock out if it was on.

// Technically speaking this disallows the start end detector

// from detecting changes that happen immediately after another

// change, but this is short-lived for the duration of one

```

```

// sample. In other words, for the real piano this doesn't

// actually matter, and if anything will improve performance

// by smoothing the outcoming notes.

note change clk out <= 0;</pre>

end else begin

// If we just clocked the pulse, unpulse.

// Go through each individual note.

for (integer i = 0; i < 12; i++) begin

// Let [1] be the last note.

// Let [0] be the current activated note.

note change out[i] <= {last activated notes[i], activated notes in[i]};</pre>

// Store the old notes so we don't reactivate on the same one.

last activated notes[i] <= activated notes in[i];</pre>

end

note change clk out <= (last activated notes[0] ^ activated notes in[0])

| (last activated notes[1] ^ activated notes in[1])

(last_activated_notes[2] ^ activated_notes_in[2])

| (last_activated_notes[3] ^ activated_notes_in[3])

| (last_activated_notes[4] ^ activated_notes_in[4])

| (last activated notes[5] ^ activated notes in[5])

(last activated notes[6] ^ activated notes in[6])

| (last_activated_notes[7] ^ activated_notes_in[7])

| (last_activated_notes[8] ^ activated_notes_in[8])

| (last_activated_notes[9] ^ activated_notes_in[9])

| (last_activated_notes[10] ^ activated_notes_in[10])

| (last activated notes[11] ^ activated notes in[11]);

// Increment the index.

note change index out <= note change index out + 1'b1;</pre>

end

end

```

endmodule

#### 6.1.9 fsm.sv (Brendan)

```

// The finite state machine. This represents the different possible

// states the piano playing robot can enter, as a superposition

// of possible environment observables.

// Author: Brendan Ashworth

module fsm(clk in, rst in,

fft done,

counter,

state out,

recording in, playing in,

playing out, recording out, paused out);

// The number of note changes we need to uniquely identify

// to play the entirety of the song.

parameter NUM CHANGES = 1024;

// System

input logic clk in;

input logic rst in;

```

```

// Signifies that the FFT is done with processing

// data.

input logic fft done;

// User inputs

// recording in is a switch

input logic recording in;

// playing in is a switch

input logic playing in;

// We output information about the state as information

// about the environment.

output logic playing out;

output logic recording out;

output logic paused out;

// State storage.

logic [3:0] state;

output logic [3:0] state_out;

assign state_out = state;

// Counter for song playback.

// Each tick (+1) in this counter represents

// a window length for the FFT.

output logic [$clog2(NUM CHANGES)-1:0] counter;

logic [$clog2(NUM CHANGES)-1:0] length;

// Each state can be broken down into environment states.

const int ENV PAUSED = 4'b0010;

assign paused_out = (state & ENV_PAUSED) == ENV PAUSED;

const int ENV PLAYING = 4'b0001;

assign playing out = (state & ENV PLAYING) == ENV PLAYING;

const int ENV RECORDING = 4'b0100;

assign recording out = (state & ENV RECORDING) == ENV RECORDING;

const int ENV_IDLE = 4'b1000;

// Represent each state as a combination of those

// environments.

const logic [3:0] STATE_PLAY = ENV_PLAYING;

const logic [3:0] STATE PAUSED = ENV PAUSED;

const logic [3:0] STATE RECORDING = ENV RECORDING;

const logic [3:0] STATE ANALYZING = 0; // analyzing represents none of the environments

const logic [3:0] STATE_IDLE = ENV_IDLE;

always ff @(posedge clk in) begin

if (rst in) begin

// If reset is high, transition to the idle state.

state <= STATE IDLE;</pre>

// Reset the counter, length.

counter <= 0;

length <= 14'b11 1111 1111 1111; // max value</pre>

end else begin

```

```

39

```

```

// Handle state transitions based on inputs.

if (state == STATE_PLAY) begin

\ensuremath{{//}} If we stop playing transition to paused.

if (!playing in)

state <= STATE PAUSED;</pre>

// The counter reaching the song length means we're done with playback.

else if (counter == length) begin

// Go back to the beginning.

counter <= 0;

state <= STATE_PAUSED;</pre>

end else begin

// We're currently playing the song,

// increment the counter.

counter <= counter + 1'b1;</pre>

end

end else if (state == STATE PAUSED) begin

// If we hit the play button continue/start.

if (playing in)

state <= STATE PLAY;</pre>

end else if (state == STATE RECORDING) begin

// Increment the counter so long as we're recording.

// This allows us to find the length of the song.

counter <= counter + 1'b1;</pre>

// If the user stops recording, transition to finish analyzing.

if (!recording in)

state <= STATE ANALYZING;</pre>

end else if (state == STATE ANALYZING) begin

// Reset the counter, set the length accordingly.

length <= counter + 1'b1;</pre>

counter <= 0;

// Analyzing continues as the FFT finishes in the pipeline.

// However long FFT takes, we wait for it to finish before allowing

// the user to continue with playback.

// FFT signifies it's done with analyzing with an input signal of

// fft done. fft done is low when it's processing real audio data.

if (fft done)

state <= STATE PAUSED;</pre>

end else if (state == STATE IDLE) begin

// Resetting the system automatically transitions us

// to the idle state, and so does a song finishing playback.

// The user can begin recording by hitting the recording switch.

if (recording in)

state <= STATE RECORDING;</pre>

end

```

endmodule

end end

#### 6.1.10 onset\_detector.sv (Max)

Note: 6.1.10 was not in synthesis on the FPGA but was adopted as we got closer to the deadline to be simpler. Merged with the spectrogram.sv.

```

// Max Hardy

module H(input reg [15:0] x,

output reg [31:0] h

);

reg [15:0] abs_x;

abs my_abs(.x(x),.abs(abs_x));

always @* begin

// rejects decreasing peaks

// allows increasing peaks to have non-zero value

h = (x+abs_x)/2;

end

```

endmodule

### 6.1.11 peak\_detector.sv (Max)

Note: 6.1.11 was not in synthesis on the FPGA but was adopted as we got closer to the deadline to be simpler. Merged with the spectrogram.sv.

```

// Max Hardy

module peak_detector( input logic clk_in,

input logic rst in,

input logic frame done,

input logic [31:0] dif,

input logic [15:0] threshold,

output logic max flag,

output logic peak

);

logic [21:0] cool off;

always_ff @(posedge clk_in) begin

if (rst in) begin

peak<=0;</pre>

cool off<=0;</pre>

end else if (frame_done & cool_off == 0) begin

if (dif > threshold) begin

peak<=1;

cool_off<=threshold[3:0] << 18;</pre>

end else begin

peak<=0;</pre>

end

end else if (frame done & cool off > 0) begin

```

```

cool_off<=cool_off-1;

peak<=0;

end

end

endmodule</pre>

```

## 6.2 Associated ESP32 C++

```

#include <ESP32Servo.h>

#include <HardwareSerial.h>

#define RXP 26

// rx pin for MySerial reading

// misc tx pin for MySerial interface

#define TXM 17

#define BAUD 115200

// Serial baud rate for FPGA interfacing

#define IDLE 0

#define PLAY 1

#define IDLE TIME 2000

// milliseconds until idle transition

#define ACT DELAY 100

// actuation delay for servos to reach desired position

#define NUM MOTORS 12

// motors cover one octave

/* pianoMan.ino

@author: Anthony Nardomarino

6.111 Digital Systems Laboratory

12-01-2019

ESP32 Interface with FPGA Piano Playing Robot Hands

*/

HardwareSerial MySerial(1);

11

Key:

11

0101 0000 - C# 0100 1000 - F

// 0100 0000 - A

0011 0000 - D 0010 1000 - F#

// 0010 0000 - A#

// 0110_0000 - B 0111_0000 - D# 0110_1000 - G

// 0001 0000 - C

0000 1000 - E 0001 1000 - G#

Servo fgA, fgAs, fgB, fgC, fgCs, fgD;

Servo fgDs, fgE, fgF, fgFs, fgG, fgGs;

Servo keys[NUM_MOTORS] = {fgA, fgAs, fgB, fgC, fgCs, fgD,

fgDs, fgE, fgF, fgFs, fgG, fgGs};

// 8 bit addresses for each motor

const byte addresses[NUM MOTORS] = {64, 32, 96, 16, 80, 48, 112, 8, 72, 40, 104, 24};

// measured resting high angles for servo fingers

const int upStrats[NUM MOTORS] = {700, 700, 650, 2200, 2250, 2150, 2200, 2300, 2200, 700,

700, 700};

// measured low angles for activated servo fingers

const int downStrats[NUM MOTORS] = {840, 820, 810, 2000, 2000, 1850, 2050, 2000, 2000, 900,

900, 900};

const byte servoPins[NUM MOTORS] = {4, 5, 12, 13, 14, 15, 16, 17, 18, 19, 21, 22};

```

```

// strategies for all motors

byte dirs[NUM_MOTORS] = {0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0};

// 0 for up, 1 for down

// old state of motors to be

compared

byte buttons[NUM MOTORS] = {0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0}; // onset control

// new state of motors

received serially

// PLAY or IDLE hands

int state;

// idle timer

int timer;

int serialIn;

// Serial input from FPGA

// counts 12 serial inputs before actuation

int counter;

byte needDel = 0;

// dynamic delay logic

void setup() {

// Setup serial channels

Serial.begin(BAUD);

MySerial.begin(BAUD, SERIAL 8N1, RXP, TXM);

// attach and program rest state servos

for (int i = 0; i < NUM_MOTORS; i ++) {</pre>

keys[i].attach(servoPins[i]);

}

for (int i = 0; i < NUM_MOTORS; i ++) {</pre>

keys[i].writeMicroseconds( upStrats[i]);

}

delay(100);

counter = 0;

// detach to prevent current flow from skipping motors

for (int i = 0; i < NUM MOTORS; i ++) {

keys[i].detach();

}

state = IDLE;

timer = millis();

}

void loop() {

// onset reads

// Read Serial and update onset control buttons

serialIn = MySerial.read();

if(serialIn != -1){

counter ++;

timer = millis();

if (state == IDLE) {

state = PLAY;

for (int i = 0; i < NUM MOTORS; i ++) {</pre>

keys[i].attach(servoPins[i]);

}

}

for (int i = 0; i < NUM MOTORS; i ++) {

if(serialIn == addresses[i]){

buttons[i] = 1;

needDel

= 1;

}

}

```

```

43

```

}

```

// Check for state change

if(millis() - timer > IDLE_TIME && state == PLAY) {

state = IDLE;

for (int i = 0; i < NUM MOTORS; i ++) {

keys[i].writeMicroseconds( upStrats[i]);

}

delay(100);

for (int i = 0; i < NUM MOTORS; i ++) {</pre>

keys[i].detach();

}

}

// Actuate activated motors

if(counter >= 12 && state == PLAY){

for (int i = 0; i < NUM MOTORS; i ++) {

// onset of play

if (dirs[i] == 0 && buttons[i] == 1) {