6.111 Final Project The Video Vitalizer - an NTSC Video System for Quadcopter Applications J. Abel, JT. McGuire - Fall 2019

# Contents

| Project Overview                                | 2  |

|-------------------------------------------------|----|

| Hardware Setup                                  | 3  |

| nplementation<br>esting and Simulation          | 4  |

|                                                 | 5  |

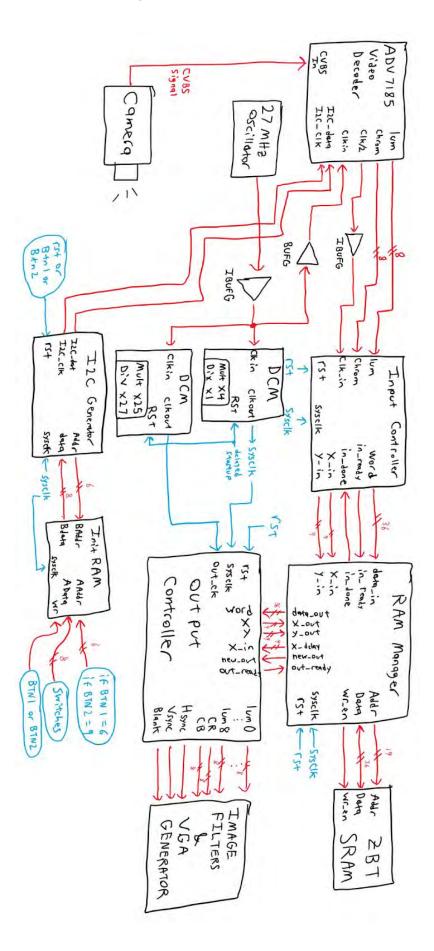

| Design Overview: Block Diagram                  | 6  |

| Memory Control & Camera Interface - JT. McGuire | 8  |

| NTSC Input Decoding                             | 8  |

| Colorbar Generator                              | 9  |

| I2C Control                                     | 9  |

| ZBT Memory Control                              | 10 |

| Output Module                                   | 11 |

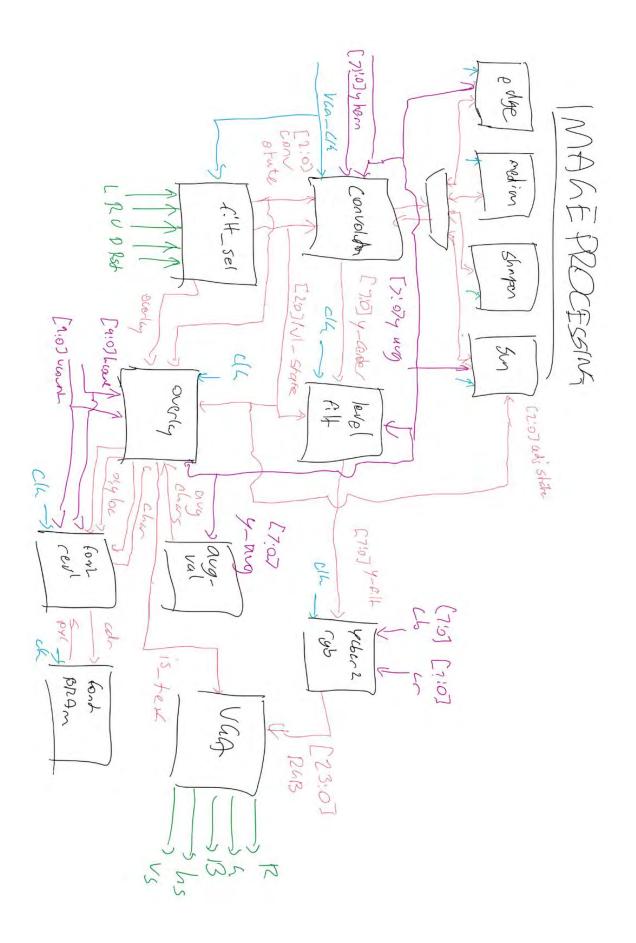

| Image Processing - J. Abel                      | 14 |

| Convolution Filtering                           | 14 |

| Edge Detection - Sobel Filtering                | 14 |

| Noise Removal - Median Filtering                | 15 |

| Sharpening - Unsharp Masking                    | 16 |

| Sun-Blocker - Threshold-Based Filtering         | 17 |

| Level Adjustment                                | 18 |

| Colorspace Conversion - YCbCr to RGB            | 19 |

| Text Overlay                                    | 20 |

| Average Brightness Level                        | 21 |

| Reflection                                      | 21 |

| Challenges/Difficulties                         | 21 |

| Advice for Future Projects                      | 22 |

| Appendix - Verilog Modules                      | 23 |

## **Project Overview**

The goal of this project is to design and implement an NTSC camera system that could be used as an FPV camera on a quadcopter. The system takes in a video feed from an NTSC camera, and displays it in real time on a VGA monitor. Additionally, filters can be applied to the image, which enhance the image quality in adverse conditions and improve the flying experience for the drone pilot. The fact that the computations needed to apply these filters must occur in real-time makes this problem ideally suited to being implemented with an FPGA.

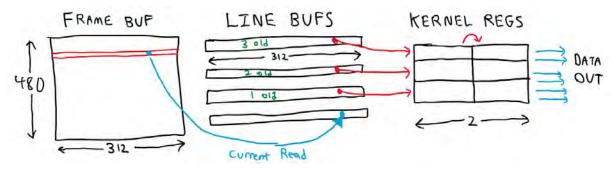

The board receives the image from the camera as an NTSC composite waveform, which is sampled by an ADV7185 NTSC video decoder. As per the NTSC standard, the received image is interlaced, and is received at a frequency of 30 Hz and a resolution of 640 TV lines per frame. The chip then encodes the video data as a 10 bit value containing luminance and chroma information in YCbCr color space. These values are extracted from this 10 bit value, and stored in a frame buffer inside a ZBT SRAM memory. The frame buffer is necessary to account for the interlaced nature of the incoming image, since the image processing filters require chunks of adjacent pixels to function. Once an entire frame has been stored, the output pixels are read into a circular buffer of four video lines, with one line being the active write buffer and the other three providing the data for the 3x3 pixel output kernel. The three read line buffers are latched into a series of shift registers on the output clock rate such that an output kernel can be generated with a height of three (each line buffer) and a width of three (three pixel-deep shift registers). This configuration means that the pixel currently being read from the frame buffer is actually two lines beneath and two pixels ahead of the pixel that is being output to the filtering modules.

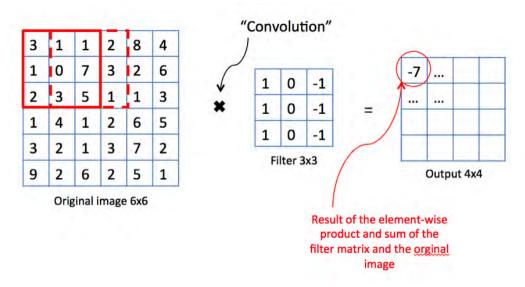

For each pixel in the image, the image processing modules receive a 3x3 kernel of luminance data from adjacent pixels, which allows convolutional filtering to be applied to the image. Four convolutional filters are available to be applied to the image, as described below:

- An edge detection filter, which uses a Sobel kernel to highlight sharp transitions in brightness

- A noise reduction filter, which uses a median filter to remove salt and pepper noise

- A sharpening filter, which uses an unsharp mask to clarify a blurry image

- A sun blocking filter, which uses thresholding to improve image clarity in direct sunlight by blocking overly bright pixels

In addition to convolutional filter, a separate filter exists that uses linear mapping to adjust the brightness levels, hence improving the readability of the image in poor lighting. This adjustment level can either be set manually or automatically based on the mean brightness of the image. The filtered pixels are then converted to RGB color space, and are displayed on a monitor using a VGA interface. A text overlay is also applied to the image at this stage to display the current filter state and overall brightness of the frame.

# Hardware Setup

The hardware setup consists of the following key components:

- An NTSC camera, which captures images in real-time and transmits them as an interlaced analog composite waveform (CVBS video signal)

- A VGA monitor, which displays the image from the camera in real time. The monitor is able to display an image with a frame rate up to 1280x1024 pixels @ 60 Hz. The final prototype had an output of 640x480 pixels @ 60 Hz.

- The 6.111 Labkit, centered around a Xilinx XC2V6000 Virtex 2 series FPGA. The Labkit contains the following periphery chips, which are used to interface the FPGA with external devices

- An ADV7185 NTSC video decoder, which digitizes the incoming NTSC signal and extracts pixel information in YCrCb space. It outputs this data in a CCIR656 4:2:2 color standard.

- A 512kx36 bit Cypress ZBT synchronous SRAMi, which is used to store the incoming frame in a frame buffer to account for the interlaced nature of NTSC video.

- A 24 bit high speed video DAC for VGA output to a monitor

The intended application of our system forced us to use some legacy hardware due to the requirement for a large, high-bandwidth memory that could be simultaneously written to and read from within a single pixel interval. The DDR RAM on the Nexys4 board requires several clock cycles in order to switch between read and write modes and therefore was insufficient for out purposes. We required a Zero Bus Turnaround [ZBT] memory in order to interlace our reads and writes to make the project possible with a single external memory. This need arises because we have to be able to save incoming pixel data while also reading outgoing pixel data within a single pixel clock cycle.

The Virtex 2 series of FPGAs has a 2002 vintage and the newest software that still supports them was released in 2008 and last updated in 2011. This need to use legacy hardware caused us a great deal of stress and strife, and we strongly recommend to all future students that the old labkit be avoided at all costs. Xilinx ISE 10.1 does not support Windows 10 and only the 32-bit version of the software was usable. However, the driver incompatibility meant that we could only use ISE on Windows for simulation. To actually interface with the hardware, we had to use Linux. Fortunately, the debian athena machines in the lab are capable of running ISE with reasonable effectiveness, though the software is still prone to crashing and strange file errors. ISE 10.1 definitely does not play nicely with the newest version of Ubuntu (we checked).

ISE 10.1 proved to be our biggest challenge in implementation. It lacked some programmable logic IP that is present in Vivado and the Nexys4 that would have been incredibly useful, most notably an internal logic analyzer and a functional clock generator. The lack of these features made timing control and debugging more difficult than it would have been on a newer board. We did not want to mess with Chipscope for obvious reasons and instead used the physical logic analyzer in the lab, which was not quite fast enough to accurately receive our 108 MHz memory interface signals reliably over its lengthy wires. Additional delays were caused by the ISE software itself, which was unstable even on the lab machines and would occasionally interpret Verilog code slightly differently to Vivado, leading to unexpected results. We found that ISE was often unable to delete configuration files from the computer RAM for IP after first creation so that one could not alter any generated modules without a full system reboot. It had many errors and really took user input more as a guideline than a rule for anything related to IP. We had major difficulty in generating digital clock modules especially, and were only able to finally produce properly configured DCMs by skipping the IP generator and giving express directives in Verilog. Timing issues were the bane of our project.

Most hobbyist FPV quadcopter camera systems send video using analog NTSC broadcast signal on a 5.8 GHz RF carrier. To maintain compatibility with this type of transmission, we needed to adhere to the NTSC video input specification. This signal is digitized by the ADV7185 video decoder IC before being received by our system. Since NTSC video signal is sent field-by-field in interlaced format, a frame must first be stored in a buffer before any convolutional processing can take place (which requires kernels of adjacent pixels).

#### Implementation

In part due to the issues described above, the project was not able to be implemented as intended in the time available. Hence, for the purposes of demonstrating the functionality of all written Verilog modules, two independent systems were built; one to demonstrate the memory control and NTSC signal conversion, and another to demonstrate the image processing and user interface.

To demonstrate the camera input and memory control modules, a system was built to display an image from an NTSC camera on a VGA monitor using the old Labikt. This system only included two 3x3 convolution filters to demonstrate how kernels of adjacent pixels are read from the ZBT memory. This module was implemented in two ways. Our first implementation included an output module that attempted to upscale the output from 640x480 to 1280x960 using averaging. This module proved to have a spotty output and was susceptible to timing issues that we were unable to track down. The system clock rate was 108 MHz, the same speed as the dot clock required by the output specification. Thus, we needed 100% throughput from our system and had to pipeline several combinational paths to meet timing spec with this design. Our second implementation was drastically simplified and included only a 3x3 output with the original 640x480 resolution. This produced a much more manageable output with fewer timing issues, no doubt helped by the pixel clock at 25 MHz, or roughly one fourth of the speed. This eased our already tight frame buffer memory bandwidth constraint because we were able to keep the system clock rate (and thus frame buffer access rate) at the same 108 MHz. This simplified 3x3 system was the same one described in the checklist and the original project outline, so it meets the project goals sufficiently. We managed to get it to full functionality, though it did still have some light ghosting and memory timing issues that caused sliding lines to appear on the displayed image. We will discuss the deficiencies of the implementation more in the reflection section of this paper.

To demonstrate the image processing features of this system, a simulated front end was built on a Nexys 4 FPGA. It was chosen to demonstrate these features on the Nexys 4 instead of the old Labkit due to its faster build time and more reliable programming interface, under the assumption that any logic written in Verilog would be portable. Due to the limited memory available on the Nexys 4, this system could only display a single image at a reduced resolution (640x480 pixels per frame, 14 bits per pixel) that was stored in a BRAM. Additionally, clock speed limitations meant a 3x3 kernel was generated for each pixel as opposed to a 5x5 kernel as originally designed, resulting in a slightly simplified implementation of some convolutional filters. Nevertheless, this system was able to demonstrate the effect of all four possible convolutional filters and the level adjustment filter on the static image. The application of these filters was controlled via the buttons on the FPGA and a text-based on screen user interface.

## **Testing and Simulation**

A critical aspect of development in our project was design verification through simulation. I (JT) was fortunate enough to get the 32-bit version of ISE 10.1 running on my Windows 10 laptop and could therefore conduct simulations outside of the 6.111 lab. Though the Xilinx simulator never worked, I managed to download ModelSim as well and used that software for simulation purposes to tweak the timing of my design. I am happy to say that because of this testing, the video input and I2C modules both worked flawlessly on the first implementation try. The frame buffer manager and output modules were not so lucky, but this was more due to timing and clocking issues resulting from poor Xilinx software and my assumptions about how the ZBT RAM would work. The simulations showed that the output would be totally functional, but simulation timing and real life timing are two very different things as we learned. For brevity's sake, we have not included the Verilog testbench code used to simulate our designs, but we have submitted it on the course website.

# Design Overview: Block Diagram

# Memory Control & Camera Interface - JT. McGuire

#### **NTSC Input Decoding**

The input CVBS video received from the camera was digitized by means of an ADV7185 video decoder IC on the labkit board. This chip latches out digital data in the CCIR656 4:2:2 standard which essentially means that color data rate is half of luminance data rate. This is acceptable because the human eye is much more sensitive to light intensity than light color. We designed our system to receive 16-bit wide output from this chip at half of the typical CCIR656 clock rate of 27 MHz. With this method, the input clock rate is 13.5 MHz and includes luminance data for consecutive pixels on 8 of the 16 bits. The other 8 bits have multiplexed color data for every other pixel such that 8 bits of red channel and 8 bits of blue channel data are sent for every two luminance values.

To control input video timing, the CCIR656 standard describes specialized codes that are sent within the data stream that indicate transitions between states for video field, horizontal blanking, and vertical blanking. The receiver module therefore required a state machine to trigger off of these codes to perform tasks such as switching vertical and horizontal indices or initiating or ending the data output to the frame buffer control module. The input module was configured with a multiple-register delay. This allowed the start and stop codes to be recognized on the oldest registers and the encoded data to be read from the one-cycle newer registers. This was a simple way of extracting the video timing for triggering the state machine.

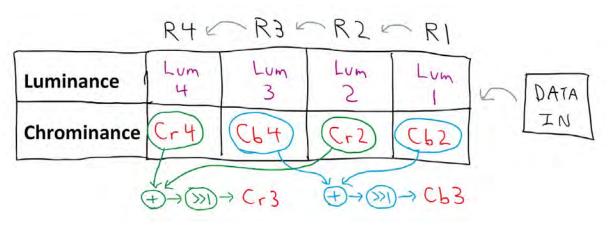

Another state machine had to be implemented for this module to upscale the color data in the image. Because the color channels were only received for every other pixel, the color information for off-pixels was computed as the average of adjacent pixels. This required a four-register delay of input information such that the red and blue channels could be received for the two adjacent pixels. If the oldest pixel is number 4 and the newest is number 1 in the registers, The full color for pixel 3 was computed using the red channels received with pixels 4 and 2 and the blue channels with pixels 3 and 1. Pixels 2 and 4 already had all color data, and pixel one would not be yet computable (Fig 1).

Figure 1 - Visualized chroma upscaling method

The input module latched the upscaled color data into output registers at the rate of reception. The data was rescaled into 36 bit words, which is the width of the frame buffer memory. Each word contained two pixels of information, with 8 bits dedicated to luminance data and 10 bits to color data (5 for each channel). A control line was triggered with each new input data to inform the frame buffer controller that a write needed to occur. The frame buffer controller also had a response line to indicate when the write was initiated. If the control line was ever triggered twice without a response, an overflow fault was indicated and the system reset. The clocking of the input module was purposefully chosen to be exactly one eighth of the system clock rate such that no syncing registers would be required. The input module also kept track of the vertical and horizontal counts for the current output pixel and latched out the nine bit X and Y position signals as appropriate to the memory module.

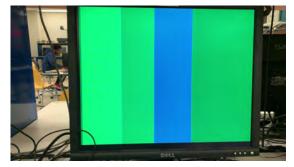

## **Colorbar Generator**

As a system testing method, it was important to create a colorbar generator module to verify that the input and output was timed properly. This enabled us to visualize skew in the output and physically see horizontal timing issues in the

implementation. The colorbar generator merely produced different pixel luminance and color values as the output progressed across the horizontal line. It also replicated the frame save signal trigger that was output by the video input module.

## **I2C Control**

To enable the output mode that we used with the ADV7185, we had to write an I2C interface module to program the configuration registers on the video encoder. This was essentially a long and complicated state machine that pushed data across the

output lines using the I2C standard. It was designed to read from a BRAM configured as a dual port PROM for easy reconfiguration of the registers. The BRAM held three 8-bit values for every register to be programmed: the slave address for the ADV7185, the subaddress for the memory register, and the actual value to program. The state machine produced a start condition, latched out the 8 bits, received the ack bit from the slave, and then sent the stop condition for each byte sent at a bitrate of 20 kHz. For proper configuration, we had to change one bit value in one register in the ADV7185 at every system startup.

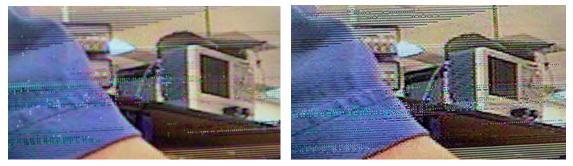

This module also included programmable video brightness and saturation via the same I2C interface with the ADV7185 module. This chip included these adjustments natively and was controlled by the setting of memory registers. Thus, we used a series of buttons and switches to write values to the PROM and to retrigger the I2C output such that new brightness and saturation levels could be set on the fly during operation (Fig 2).

*Figure 2 - Comparison of normal, high-brightness, and low saturation images from left to right (modified using I2C module for ADV7185 register control)*

## **ZBT Memory Control**

The frame buffer control module was deceptively simple in theory and incredibly complicated in practice due to timing constraints. It operated on the 108 MHz system clock rate, interlacing read and write data onto the ZBT memory data lines while computing the proper addresses. The address computation had to include a hardware multiplier to compute the proper location for the target pixel with the equation Y\*FRAME\_WIDTH+X. Because of the 108 MHz clock rate and the additions and multiplexing that had to occur for address computation from the input and the output modules, this had to be implemented in three pipeline stages. Additionally, the ZBT SRAM itself had a two stage pipeline delay from input to output, meaning that reads had a total latency of five clock cycles through the system.

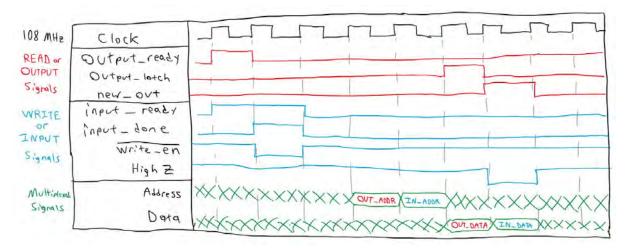

Read and write control was implemented using the synchronous write control lines on the ZBT RAM. However, because the data lines were multiplexed for both reading and writing, the FPGA had to be told when to set the ports to high impedance mode for data reception and when to set the ports to drive mode for writing. This needed to occur two clock cycles after a write was indicated. This module in essence became a massive series of shift registers for input signals and assignments to output signals such that the proper operations were conducted at the proper times for both reads and writes. Luckily, the ZBT RAM had a nifty feature wherein it was automatically configured to put its data port into high impedance mode whenever a write was indicated at the proper time, provided the output enable pin was held low. Thus, the FPGA remained in high impedance mode and the RAM in drive mode by default, with the roles switching when a write was indicated. See figure 3 for a sample timing diagram.

The interlacing method gave precedence to the output module and always prioritized reads over writes because reads happened twice as fast due to the 60 Hz output. Additionally, write data and address information was always saved into a latch that was guaranteed for eight cycles, so address and data sequencing was much less critical for writes and could be reasonably ignored. Reads, on the other hand, required shift registers for all signals to ensure proper timing. Thus, a high output ready trigger would be shifted back five times to trigger the output capture word latch for each incoming read address. Incoming X data was also shifted back five times to produce an X output that was synchronized to the output data, simplifying the output module design. If a read was not triggered on a given clock cycle and a write was, the system would raise the write-initiated line to prevent overflow and service the write by triggering the write-enable output for the ZBT RAM after three clock cycles of address computation. Then it would put the FPGA data port into drive mode two clock cycles later to write the output data to the RAM.

*Figure 3 - Sample timing diagram of typical interleaved read/write operations*

This module was a mess of timing. We know it is functional because we conclusively proved by suspending input that it was properly writing and reading to the memory. However, the output contains shifting lines when the camera is engaged that are not present with suspended input, and this leads us to conclude that there are still some subtle timing issues where writes are somehow affecting reads when they should be independent. We unfortunately did not have the time to debug the module, and the physical logic analyzer does not even have the speed to do so effectively. To find this

error, I firmly believe that we would need to switch to a completely different FPGA such that we could use an integrated logic analyzer and software that was not flaming hot garbage.

#### **Output Module**

The output module went through two design iterations. The first iteration was more ambitious and involved an image upscaling computation from 640x480 to 1280x1024 that drastically increased complexity. It will be described with less detail because it did not come to full fruition. The second iteration was the design as implemented and did achieve full functionality with a 3x3 kernel and straight 640x480 output. For all iterations, full kernels were only generated for luminance data, and chrominance data was only output for the center pixel of the kernel. This step was taken to reduce complexity, as we deemed filtering of the color data an unnecessary step due to the lack of sensitivity to it for human viewers.

The upscaling module worked through a series of five line buffers built from BRAMs that each saved a single line of video data, or 312 thirty-six-bit words in our implementation (625 pixels input became 312 words in the input module). These were written to with an index and switched in a circular style, with the index pointing to the line that was the active read buffer from the frame stored on the ZBT RAM. This circular structure had to be faked with large multiplexers, as BRAMs are not actually configured with indices that wrap around like a real circular buffer. The multiplexers connected the proper line buffer data outputs to intermediate wires for the previous four consecutive video lines that occupied the circular frame buffer. The index incremented with each new line and the multiplexers switched the intermediate wires to point to the new consecutive buffer data outputs. In this way, four consecutive lines could always be read simultaneously from four video line buffers while the fifth buffer was used to capture the next line from the external frame buffer on the ZBT SRAM. From here, the four line buffer outputs were each sent through shift registers with four cycle depth to generate a 4x4 array of registers that could be simultaneously read for output. This was fed into a vast array of multiplexers, shifters, and adders that computed pixel values "in between" the actual values for upscaling, and a state machine controlled the multiplexers to output these values alternately to generate a full 5x5 kernel of luminance data that was sent to the image processing modules. We found that this upscaled 5x5 output kernel with a 108 MHz dot clock had an impressive output data rate of 24 gigabits per second.

Figure 4 - Diagram of the output memory architecture and data flow paths

Unfortunately, we were not able to get the upscaled system to a fully functional state. We think this was the case chiefly because of timing issues. In our second system, we removed the upscaling and dropped to a 3x3 output kernel for simplicity. We think that the further timing modifications made with the simplified system may have enabled full operation of the upscaled system as well, but we were unable to test this theory due to time constraints.

The 640x480 version used a very similar structure to the upscaled 5x5 version. However, it required only four line buffers instead of five (three to read from and one to write to) and a register depth of two instead of four (two words = four pixels of depth) (Fig 4). Additionally, we were able to skip the upscaling computations and seriously simplify the state machine that controlled the multiplexers for output. The output merely had to switch between even and odd pixels to deal with the two-pixel word storage mechanism (Fig 5). In the upscaled version, the multiplexer also had to deal with properly sequencing the half-pixels between actual pixels and the half-lines between actual lines. This was also a nightmare from a timing perspective.

| OUT REGO                                                                                                        |            |

|-----------------------------------------------------------------------------------------------------------------|------------|

| Pix13 ; Pix14                                                                                                   | KERNEL ONE |

| Pix 23 ; Pix 24                                                                                                 |            |

| the second se |            |

|                                                                                                                 |            |

Figure 5 - Diagram of output kernel multiplexing for two-pixel word storage

The multiple line buffer and shift register structure that we implemented for kernel output was an effective way of reducing the data rate required from the ZBT memory. While it would have been easier to directly read the pixel values from the frame buffer, this was impossible with our system clock speed, as there is no way that we could have read the value for each of the nine pixel values needed for each output and still had time for writing. At best, we could have possibly doubled our memory read bandwidth, but even that would have pushed the limit. This method is more robust and also proved to be scalable in that we were able to quickly refactor the code to reduce the complexity while keeping the same structure. We were able to exploit the speed benefits of multiple BRAMs, the storage benefits of the ZBT external memory, and the repetitive nature of image kernels to achieve an output with a very high bitrate that could deal with interlaced input video signal with a different clock rate than the output.

# **Image Processing - J. Abel**

### **Convolution Filtering**

The majority of the image processing was performed using convolutional filters. These filters perform a mathematical operation on a square kernel of adjacent pixels, producing a single, processed pixel in the center of the array. In a strictly convolutional filter, this operation is an element-wise multiplication with another square array known as the convolutional kernel. This is the operation used for the sharpening and edge detection filters. Other implemented filters are not strictly 'convolutional' in their application, instead performing a different operation on the kernel (a median operation for the noise reduction filter, and a thresholding operation for the sun blocking filter). It is important to note that a convolutional filter is applied to an array of numbers, however a color image is an array of tuples. Hence, only one channel of the image is processed - in this case the luminance channel, which we felt to be the best representation of the overall composition of each image.

*Figure 6 - an example of a simple 3x3 convolutional filter (image source - M. Cavaioni, Medium)* To implement convolutional filtering in Verilog, a 72 bit or 200 bit register (for a 3x3 or 5x5 kernel respectively) is used to represent the incoming kernel of adjacent pixels. Generating such a kernel requires a memory read clock that is significantly faster than the clock used to drive the VGA output.

## **Edge Detection - Sobel Filtering**

The edge highlighter applies a Sobel convolution kernels to each pixel to detect and highlight sharp transitions in brightness in the image. This filter works by performing a convolution operation to each pixel, then comparing the output to a threshold value to determine the presence of a sharp transition. This filter actually requires two parallel convolution operations using convolution kernels that are 90° rotation of each other (shown below), which allows the system to detect horizontal and vertical edges.

$$G_x = \begin{bmatrix} -1 & 0 & +1 \\ -2 & 0 & +2 \\ -1 & 0 & +1 \end{bmatrix}, \ G_y = \begin{bmatrix} -1 & -2 & -1 \\ 0 & 0 & 0 \\ +1 & +2 & +1 \end{bmatrix}$$

In Verilog, this filter was implemented by applying arithmetic operations to subsets of a 72 bit value representing the input kernel. An OR statement was used to assign an edge to the output pixel based on the thresholded outputs of the two convolution filters. This is achieved by assigning either full or zero brightness to an edge pixel, the color selected based on the aggregate brightness of the frame to maximise the visibility of the edge. Since the arithmetic for the module only consists of addition and bit shifts, it can be performed using almost exclusively combinational logic (however, registers are used to provide a one cycle delay for pipelining purposes).

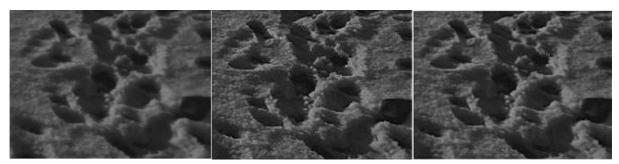

Figure 7 - Application of the Sobel filter on an image from the NTSC camera

#### Noise Removal - Median Filtering

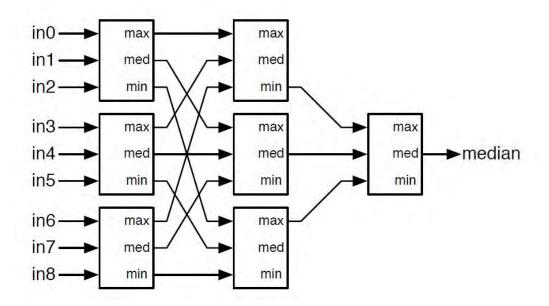

A noise removal filter is included to remove salt and pepper noise from an image, which is a common problem in NTSC video. Removing this kind of noise is best done using a median filter, which outputs the median value of a 3x3 kernel of adjacent pixels. While this filter results in some overall smoothing of the image and subsequent loss in resolution, it can remove almost all salt and pepper noise.

This filter is surprisingly difficult to implement in Verilog, since there is no simple logical operator that can be used to sort a list of values. Nevertheless, it was found that the median value could be obtained using the sorting matrix shown below. Each submodule of this matrix uses combinational logic to find the median, maximum, and minimum of a set of three values. Since each pixel needs to pass through a maximum of three subfilters to find the median, this filter introduces the most delay of the four possible convolutional filters. Hence, all other filters should be pipelined relative to this filter.

*Figure 8 - A diagram of the sorting matrix used to find the median of a nine values (image source: R. Avizienis, Berkeley)*

*Figure 9 - An image with added salt-and-pepper noise before (left) and after (right) passing through a median filter*

#### Sharpening - Unsharp Masking

A convolution filter is also available in this system to sharpen the image. Two different types of sharpening kernels were tested in this project: a simpler 3x3 sharpening kernel, and a 5x5 unsharp mask, which combines a sharpening operation with a Gaussian blur to create a clearer image. Because of its improved performance, we planned to implement a 5x5 unsharp mask on the completed system, which is designed to be able to output a kernel of 25 adjacent pixels for every cycle of the VGA clock. However, clock speed and memory limitations of our imaging processing test system meant that the simpler 3x3 sharpening filter was demonstrated instead.

$$G_s = \begin{bmatrix} 0 & \frac{-1}{2} & 0\\ \frac{-1}{2} & 3 & \frac{-1}{2}\\ 0 & \frac{-1}{2} & 0 \end{bmatrix}, \ G_u = \frac{-1}{256} \begin{bmatrix} 1 & 4 & 6 & 4 & 1\\ 4 & 16 & 24 & 16 & 4\\ 6 & 24 & -476 & 24 & 6\\ 4 & 16 & 24 & 16 & 4\\ 1 & 4 & 6 & 4 & 1 \end{bmatrix}$$

Since both of these filters require multipliers to function, this operation cannot be done without a latency of at least one clock cycle. Hence, the operations for this filter needed to be registered. In addition to performing the multiplication operations, the module performs clipping of the output to keep it within the permissible range of luminance values of a single pixel (between 16 and 235 for an 8-bit pixel).

*Figure 9 - The effect of a 3x3 sharpening filter (middle) and 5x5 unsharp mask (right) on a blurry raw image (middle)*

Figure 10 - Application of a 3x3 sharpening filter (right) on an image from the NTSC camera

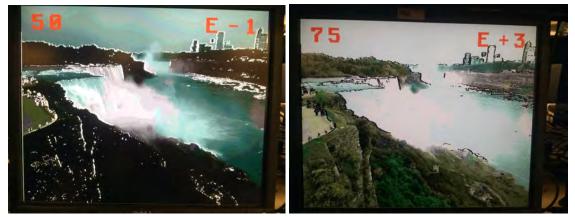

## Sun-Blocker - Threshold-Based Filtering

A common issue faced by drone-mounted FPV cameras is that their image tends to be washed out by direct sunlight. To counter this, a 'sun blocking' filter has been included, which uses thresholding to block-out pixels constituting the light source. When used in conjunction with level adjustment to darken the pixels surrounding the blacked out area, this filter can significantly improve the usability of the camera in direct sunlight. This filter assumes that a pixel that is part of a light source will have the maximum possible value of luminance. Based on this assumption, it compares the luminance value of the pixel against a high threshold, and outputs a black pixel if the threshold is exceeded.

Initially, this filter was applied on each pixel independently as part of the brightness level adjustment filter (below). However, this resulted in a noisy output. To counter this, we applied the thresholding filter to each pixel in a kernel of adjacent pixels, and output a black pixel only if at least half the pixels in the kernel exceeded the threshold. Using this method, the resultant black-out area was found to be smoother and more continuous.

*Figure 11 - The application of the sun blocking filter to an overexposed image. In this case, the system is blocking out the whitewater section of the waterfall, which is otherwise completely washed out.*

### Level Adjustment

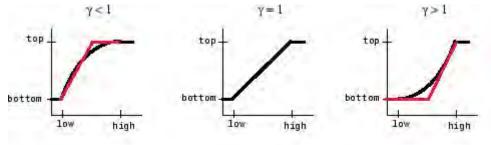

Once convolution filtering has been applied to a pixel, the single output pixel then passes through a level adjustment filter. This feature is intended to supplement the brightness correction performed by the camera, which we can control using the I2C communication module, by allowing the brightness level of pixels to be adjusted after additional processing has been performed. The filter uses linear mapping to adjust the luminance value of the pixel, making the overall image brighter or darker without reducing the brightness range of the image. To increase the brightness of an image for example, pixels with a luminance values between 0 and 50% can be remapped to values between 0 and 100%, while pixels outside of this range are assigned the maximum luminance value possible. This method is a linear approximation of gamma correction, which remaps pixels on the nonlinear power curve  $AV_{in}^{\gamma}$ .

*Figure 12 - Gamma correction curves to brighten (left) and darken (right) an image, with their linear approximations superimposed (image source - Mathworks)*

Six different adjustment levels have been programmed into this system: three which darken the image, and three which lighten it. Each adjustment level has its own linear mapping relation, which is represented as a clipped multiplication operation in Verilog. The user can either manually set the adjustment level of the filter, or set the system to automatically apply a filter based on the average brightness of the frame.

Figure 13 - The same image with a luminance level adjustment of -1 (left) and +3 (right)

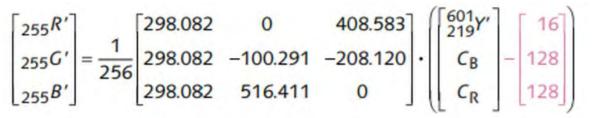

### **Colorspace Conversion - YCbCr to RGB**

NTSC camera systems send data in a YCbCr color space, which encodes luminance data on one channel and color data as a blue and red chroma on two other channels. VGA monitors, by contrast, require data to be received in an RGB color space, with three channels representing the amount of red, green, and blue in a pixel. We elected to perform all prior processing on the luminance channel in YCbCr space, which is the format output by the camera, as it best represents the overall composition of the image. Thus, the color space conversion occurs after filtering has been applied immediately before sending the data to the VGA monitor.

Pixel data can be converted between these two color spaces using the matrix multiplication below. For implementation in Verilog, the coefficients of the matrix were rounded such that no floating point arithmetic was required. Since this multiplication includes negative numbers, signed values are used to perform this operation. It is important to note that some inputs to this function will result in values of R, G, or B that are outside the permissible range for an 8 bit pixel (0 to 255). Hence, the output must be clipped.

Figure 14 - Image Source - C. Poynton, A Technical Introduction to Digital Video

### **Text Overlay**

The application of these filters was driven by an FSM, which was in turn controlled by the buttons on the FPGA. The user can see the current state of the FSM, and hence the filters that are currently applied to the image, using a text-based user interface overlayed on top of the image. Data to generate the font for this overlay is stored in a single 1 bit wide array in a BRAM. A Verilog module takes in the current pixel location on the screen, determines which character (if any) should be displayed at that location, and reads the corresponding BRAM address to determine whether the particular pixel should show the processed image or part of the font.

In addition to displaying the state of the filter selection FSM, the overlay also displays the average frame brightness as a percentage. This requires converting the average screen brightness to a binary coded decimal, in which each digit of a decimal number is represented as a 4 bit binary value. This conversion is achieved using the double-dabble algorithm, which is iteratively applied to the input value using the following steps:

- 1. Create a 4 bit register for each digit of the number

- 2. Iteratively shift the value leftwards into the registers

3. If any register is greater than 5, add 3 to it (this represents carry-over) Such an algorithm is able to make use of the parallel computing capabilities of the FPGA to be carried out in one clock cycle.

|      | Operation | Binary    | 1's  | 10's | 100's |

|------|-----------|-----------|------|------|-------|

| -162 |           | 1010 0010 |      |      |       |

|      | << #1     | 010 0010  | 1    |      |       |

|      | << #2     | 10 0010   | 10   |      |       |

|      | << #3     | 0 0010    | 101  |      |       |

|      | add 3     |           | 1000 |      |       |

|      | << #4     | 0010      | 0000 | - 1  |       |

|      | << #5     | 010       | 0000 | 10   |       |

|      | << #6     | 10        | 0000 | 100  |       |

|      | << #7     | 0         | 0001 | 1000 |       |

|      | add 3     |           |      | 1011 |       |

|      | << #8     |           | 0010 | 0110 | 1     |

*Figure 15 - Visualization of the conversion of a number to binary-coded decimal using the double-dabble algorithm (image source: N. McDonald, University of Utah)*

#### Average Brightness Level

Many of these features (e.g. the automatic level adjuster) use the average frame luminance as an input. This value can be estimated at the frame read stage of the memory controller, by storing the cumulative sum of luminance of outgoing pixels in a register and dividing it by the number of pixels in a frame. A new frame signal latches the calculated value for the previous frame to the output and resets the counter. The key challenge in this module is performing the division operation needing to calculate the average, since the FPGA cannot divide by any value apart from powers of two (which is achieved through bit shifting). A frame as output by the ZBT memory contains 307,200 pixels, which is not a power of two and is hence impossible to divide by. To mitigate this constraint, the pixels are evenly sampled so that every 64 out of 75 pixels is added to the cumulative sum. The sum hence needs to be divided by 2<sup>18</sup> to calculate the average, which is possible using bit shifts.

## Reflection

#### Challenges/Difficulties

A critical issue that we had to deal with in the implementation of our system was timing of the system output. In the original design, we were using the input frame rate to clock the output frame rate. We also had a switchable buffer to avoid writing to the same set of pixels that we were reading from as was the case in the finalized version. The essential plan was to use the video input timing from the camera to trigger the buffer switch. For every input frame of 30 Hz NTSC video, we would output two frames of 60 Hz VGA video. However, we failed to realize that the NTSC standard *actually operates at a frame rate of 29.97 Hz*. This is a vestige of historical bandwidth constraints that makes this method of operation impossible because the output rate does not equal the input rate and therefore one cannot trigger the other without producing serious timing issues (trust us; we tried). If one does try to use the input as a trigger, the VGA timing specification can never actually be met because the horizontal line timing is irregular, with alternating lines pushing sync signals at different times. VGA monitors cannot cope with this sort of drastic timing variation, and thus our hopes of using a switchable frame buffer were dashed.

To solve this issue, we had to guarantee clocking independence between the input and output modules. We accomplished this by using a single shared frame buffer where reads and writes were scheduled and clocked without regard for one another. In this method, alternate fields are written willy-nilly to the frame buffer while sequential lines are read out, and strange screen tearing can occur at the output as a result with alternate lines shifted away from each other due to the interlaced NTSC input. We also had to use synchronization registers and data latches to interface between the output

clock domain and the system clock domain for reads from the frame buffer, because the output had to operate at 25 MHz, which is not an even multiple of the system 108 MHz.

Another battery of critical problems arose with configuring digital clock managers using the flaming hot pile of trash that is also known as Xilinx ISE 10.1. As previously mentioned, this software tends to forget itself and randomly save untraceable and unchangeable configuration data somewhere in the complicated chain of software transformations that must occur to configure the FPGA. This means that one cannot configure IP using the built-in IP configurator with any degree of confidence. We had to learn how to direct verilog to use Xilinx primitives to generate DCM clock modules, and even that process still caused errors that could only be fixed by rebooting the Linux machine. This software is complete shit. Avoid at all costs. Please.

## **Advice for Future Projects**

We recommend the following advice for students wishing to pursue video/camera based projects in future iterations of 6.111:

- Simulations are incredibly useful for designing and debugging modules. It is almost always faster to write a testbench to visualize and debug a module than to try to debug a module when implemented in hardware. However, simulations make certain assumptions that make them an imperfect representation of the behavior of real physical systems. Many of these simplifications, such as assuming all combinational operations occur instantaneously or all clocks are synchronized, will cause systems to appear to work in simulation, only to fail when implemented. Hence, don't assume that a module will work first try just because it worked in simulation.

- Don't wait until just before the project deadline to begin integrating your system. While it may seem like the hardest part of writing Verilog is writing functioning modules, some of the more frustrating bugs come from issues in the interfaces between multiple modules. Additionally, it is possible that a module will behave entirely different when connected to a physical system than in the ideal world of simulations (see above). Hence, be sure to start this process early to allow time for debugging

- Use the Nexys 4 and Vivado for your product, instead of trying to work with legacy hardware and software (i.e. ISE and the old labkit). These tools will become ever more incompatible with modern computers as time goes on, making them even more frustrating to work with.

- Timing is important, especially when interfacing with external devices. If the timings of two modules are not synchronized correctly, they will likely not transfer information between themselves correctly. Creating a pipelining diagram is often a good way to resolve these errors.

- Piazza is a great way to get help, especially outside of staffed lab hours use it.

# **Appendix - Verilog Modules**

Note - The modules shown are for the system as demonstrated (i.e. with a 640x480 screen resolution and 3x3 convolution kernels). Modules were also written and tested in simulation for the intended specifications (1280x1024 screen resolution, 5x5 kernels), however these modules were not implemented into the final system. These modules are indicated with a \* in their title.

```

// Engineer: jt.mcguire (80%), j.abel (20%)

11

// Module Name: labkit

// Description: top level module

11

module labkit (beep, audio reset b, ac97 sdata out, ac97 sdata in,

ac97 synch,

ac97_bit_clock,

vga out red, vga out green, vga out blue, vga out sync b,

vga out blank b, vga out pixel clock, vga out hsync,

vga out vsync,

tv out ycrcb, tv out reset b, tv out clock, tv out i2c clock,

tv out i2c data, tv out pal ntsc, tv out hsync b,

tv out vsync b, tv out blank b, tv out subcar reset,

tv in ycrcb, tv in data valid, tv in line clock1,

tv in line clock2, tv in aef, tv in hff, tv in aff,

tv in i2c clock, tv in i2c data, tv in fifo read,

tv in fifo clock, tv in iso, tv in reset b, tv in clock,

ram0 data, ram0 address, ram0 adv ld, ram0 clk, ram0 cen b,

ram0 ce b, ram0 oe b, ram0 we b, ram0 bwe b,

ram1_data, ram1_address, ram1_adv_ld, ram1_clk, ram1_cen_b,

ram1 ce b, ram1 oe b, ram1 we b, ram1 bwe b,

clock feedback out, clock feedback in,

flash_data, flash_address, flash_ce_b, flash_oe_b, flash_we_b,

flash reset b, flash sts, flash byte b,

rs232 txd, rs232 rxd, rs232 rts, rs232 cts,

mouse clock, mouse data, keyboard clock, keyboard data,

clock 27mhz, clock1, clock2,

```

```

disp blank, disp data out, disp clock, disp rs, disp ce b,

disp reset b, disp data in,

button0, button1, button2, button3, button enter,

button right,

button left, button down, button up,

switch,

led,

user1, user2, user3, user4,

daughtercard,

systemace data, systemace address, systemace ce b,

systemace_we_b, systemace_oe_b, systemace_irq,

systemace_mpbrdy,

analyzer1 data, analyzer1 clock,

analyzer2 data, analyzer2 clock,

analyzer3 data, analyzer3 clock,

analyzer4_data, analyzer4_clock);

// Misc outputs

output beep, audio reset b, ac97 synch, ac97 sdata out;

input ac97_bit_clock, ac97_sdata_in;

// VGA output

output [7:0] vga out red, vga out green, vga out blue;

output vga out sync b, vga out blank b, vga out pixel clock,

vga_out_hsync, vga_out_vsync;

// Composite output

output [9:0] tv out ycrcb;

output tv out reset b, tv out clock, tv out i2c clock, tv out i2c data,

tv out pal ntsc, tv out hsync b, tv out vsync b, tv out blank b,

tv out subcar reset;

// Composite input

input [19:0] tv in ycrcb;

input tv in data valid, tv in line clock1, tv_in_line_clock2,

tv in, tv in hff, tv in aff;

output tv in i2c clock, tv in fifo read, tv in fifo clock, tv in iso,

tv in reset b, tv in clock;

inout tv in i2c data;

// RAM JAM

inout [35:0] ram0 data;

output [18:0] ram0 address;

output ram0 adv ld, ram0 clk, ram0 cen b, ram0 ce b, ram0 oe b,

ram0 we b;

```

```

output [3:0] ram0 bwe b;

inout [35:0] ram1 data;

output [18:0] ram1 address;

output ram1 adv ld, ram1 clk, ram1 cen b, ram1 ce b, ram1 oe b,

ram1 we b;

output [3:0] ram1 bwe b;

// RAM clock feedback

input clock feedback in;

output clock feedback out;

//assign clock feedback out=1'b0;

// Flash crap

inout [15:0] flash data;

output [23:0] flash address;

output flash ce b, flash oe b, flash we b, flash reset b, flash byte b;

input flash sts;

// Misc outputs

output rs232 txd, rs232 rts;

input rs232 rxd, rs232 cts;

input mouse_clock, mouse_data, keyboard_clock, keyboard_data;

// Clocks

input clock 27mhz, clock1, clock2;

// System display

output disp blank, disp clock, disp rs, disp ce b, disp reset b;

input disp data in;

output disp data out;

// Buttons and LEDs

input button0, button1, button2, button3, button enter, button right,

button left, button down, button up;

input [7:0] switch;

output [7:0] led;

// Data ports

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

inout [15:0] systemace data;

output [6:0] systemace address;

output systemace ce b, systemace we b, systemace oe b;

input systemace irq, systemace mpbrdy;

output [15:0] analyzer1_data, analyzer2_data, analyzer3 data,

analyzer4 data;

output analyzer1 clock, analyzer2 clock, analyzer3 clock,

analyzer4 clock;

//// IO Assignments /////

```

```

// Audio Input and Output

assign beep= 1'b0;

assign audio reset b = 1'b0;

assign ac97 synch = 1'b0;

assign ac97 sdata out = 1'b0;

// ac97 sdata in is an input

// VGA Output

11

assign vga out red = 8'h0;

// assign vga out green = 8'h0;

// assign vga out blue = 8'h0;

assign vga_out_sync_b = 1'b1;

11

11

assign vga out blank b = 1'b1;

// assign vga out pixel clock = 1'b0;

// assign vga out hsync = 1'b0;

// assign vga_out_vsync = 1'b0;

// Video Output

assign tv out ycrcb = 10'h0;

assign tv out reset b = 1'b0;

assign tv out clock = 1'b0;

assign tv_out_i2c_clock = 1'b0;

assign tv out i2c data = 1'b0;

assign tv out pal ntsc = 1'b0;

assign tv out hsync b = 1'b1;

assign tv out vsync b = 1'b1;

assign tv out blank b = 1'b1;

assign tv out subcar reset = 1'b0;

// SRAM unused

assign ram1 data = 36'hZ;

assign ram1 address = 19'h0;

assign ram1 adv ld = 1'b0;

assign ram1 cen b = 1'b1;

assign ram1 ce b = 1'b1;

assign ram1 oe b = 1'b1;

assign ram1 we b = 1'b1;

assign ram1 bwe b = 4'hF;

// clock feedback in is an input

// Flash ROM

assign flash data = 16'hZ;

assign flash address = 24'h0;

assign flash ce b = 1'b1;

assign flash oe b = 1'b1;

assign flash we b = 1'b1;

assign flash reset b = 1'b0;

assign flash byte b = 1'b1;

// flash sts is an input

// RS-232 Interface

```

```

assign rs232 txd = 1'b1;

assign rs232 rts = 1'b1;

// rs232 rxd and rs232 cts are inputs

// LED Displays

assign disp blank = 1'b1;

assign disp clock = 1'b0;

assign disp rs = 1'b0;

assign disp ce b = 1'b1;

assign disp reset b = 1'b0;

assign disp data out = 1'b0;

// disp data in is an input

// button0, button1, button2, button3, button_enter, button_right,

// button left, button down, button up, and switches are inputs

// User I/Os

assign user1 = 32'hZ;

assign user2 = 32'hZ;

assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace_data = 16'hZ;

assign systemace address = 7'h0;

assign systemace ce b = 1'b1;

assign systemace we b = 1'b1;

assign systemace oe b = 1'b1;

// systemace_irq and systemace_mpbrdy are inputs

// Logic Analyzer

assign analyzer1 clock = 1'b1;

assign analyzer3 clock = 1'b1;

reg [8:0] rstcnt;

wire sysclk;

wire locked;

wire rst;

wire ram clk;

wire out_clk;

assign rst = ~button0;

assign ram1 clk = 1'b0;

```

```

wire refclk;

```

```

IBUFG ref buf1 (.I(clock 27mhz), .O(refclk));

// Main sysclk generator

wire sysclk buf;

BUFG CLKFX BUFG main (.I(sysclk buf),

.O(sysclk));

wire clkfb_main, clk0_main, ramclkout;

BUFG CLK0 BUFG main (.I(clk0 main),

.O(clkfb main));

DCM DCM main (.CLKFB(clkfb main),

.CLKIN(refclk),

.DSSEN(1'b0),

.PSCLK(1'b0),

.PSEN(1'b0),

.PSINCDEC(1'b0),

.RST(),

.CLKDV(),

.CLKFX(sysclk buf),

.CLKFX180(),

.CLK0(clk0 main),

.CLK2X(),

.CLK2X180(),

.CLK90(),

.CLK180(),

.CLK270(),

.LOCKED(),

.PSDONE(),

.STATUS());

defparam DCM main.CLK FEEDBACK = "1X";

defparam DCM main.CLKDV DIVIDE = 2.0;

defparam DCM main.CLKFX DIVIDE = 1;

defparam DCM main.CLKFX MULTIPLY = 4;

defparam DCM main.CLKIN DIVIDE BY 2 = "FALSE";

defparam DCM main.CLKIN PERIOD = 37.037;

defparam DCM main.CLKOUT PHASE SHIFT = "NONE";

defparam DCM main.DESKEW ADJUST = "SYSTEM SYNCHRONOUS";

defparam DCM main.DFS FREQUENCY MODE = "LOW";

defparam DCM main.DLL FREQUENCY MODE = "LOW";

defparam DCM main.DUTY CYCLE CORRECTION = "TRUE";

defparam DCM main.FACTORY JF = 16'hC080;

defparam DCM main.PHASE SHIFT = 0;

defparam DCM main.STARTUP WAIT = "FALSE";

//assign ram0 clk = sysclk;

// Main ramclk generator

wire clkfb ram, clk0 ram, ramram, fb out;

BUFG CLK0 BUFG ram (.I(clk0 ram), .O(fb out));

IBUFG RAM FB (.I(clock feedback in), .O(clkfb ram));

BUFG del1 (.I(fb_out), .O(clock feedback out));

assign ram0 clk = fb out;

DCM DCM ram (.CLKFB(clkfb ram),

.CLKIN(sysclk),

```

```

.DSSEN(1'b0),

.PSCLK(1'b0),

.PSEN(1'b0),

.PSINCDEC(1'b0),

.RST(rstcnt<=9'b111111100),

.CLKDV(),

.CLKFX(),

.CLKFX180(),

.CLK0(clk0 ram),

.CLK2X(),

.CLK2X180(),

.CLK90(),

.CLK180(),

.CLK270(),

.LOCKED(),

.PSDONE(),

.STATUS());

defparam DCM ram.CLK FEEDBACK = "1X";

defparam DCM ram.CLKDV DIVIDE = 2.0;

defparam DCM ram.CLKFX DIVIDE = 1;

defparam DCM ram.CLKFX MULTIPLY = 4;

defparam DCM ram.CLKIN DIVIDE BY 2 = "FALSE";

defparam DCM ram.CLKIN PERIOD = 37.037;

defparam DCM ram.CLKOUT PHASE SHIFT = "NONE";

defparam DCM ram.DESKEW ADJUST = "SYSTEM SYNCHRONOUS";

defparam DCM ram.DFS FREQUENCY MODE = "LOW";

defparam DCM ram.DLL FREQUENCY MODE = "LOW";

defparam DCM ram.DUTY CYCLE CORRECTION = "TRUE";

defparam DCM ram.FACTORY JF = 16'hC080;

defparam DCM ram.PHASE SHIFT = 0;

defparam DCM ram.STARTUP WAIT = "FALSE";

// Main out clk generator

wire outclk buf;

BUFG CLKFX BUFG out (.I(outclk buf),

.O(out clk));

wire clkfb out, clk0_out;

BUFG CLK0 BUFG out (.I(clk0 out),

.O(clkfb out));

DCM DCM out (.CLKFB(clkfb out),

.CLKIN(refclk),

.DSSEN(1'b0),

.PSCLK(1'b0),

.PSEN(1'b0),

.PSINCDEC(1'b0),

.RST(),

.CLKDV(),

.CLKFX(outclk buf),

.CLKFX180(),

.CLK0(clk0 out),

.CLK2X(),

.CLK2X180(),

```

```

.CLK90(),

.CLK180(),

.CLK270(),

.LOCKED(),

.PSDONE(),

.STATUS());

defparam DCM out.CLK FEEDBACK = "1X";

defparam DCM out.CLKDV DIVIDE = 2.0;

defparam DCM out.CLKFX DIVIDE = 27;

defparam DCM out.CLKFX MULTIPLY = 25;

defparam DCM out.CLKIN DIVIDE BY 2 = "FALSE";

defparam DCM_out.CLKIN_PERIOD = 37.037;

defparam DCM out.CLKOUT PHASE SHIFT = "NONE";

defparam DCM out.DESKEW ADJUST = "SYSTEM SYNCHRONOUS";

defparam DCM out.DFS FREQUENCY MODE = "LOW";

defparam DCM out.DLL FREQUENCY MODE = "LOW";

defparam DCM out.DUTY CYCLE CORRECTION = "TRUE";

defparam DCM out.FACTORY JF = 16'hC080;

defparam DCM out.PHASE SHIFT = 0;

defparam DCM out.STARTUP WAIT = "FALSE";

assign tv in clock = refclk;

wire out done;

wire in_ready, out_ready;

wire in done;

wire new out;

wire nf, f;

reg f0;

reg [21:0] fcnt;

reg [20:0] fcnt2;

wire [8:0] in_x, in_y, out_x, read_x, read_y;

wire [35:0] word, data in;

wire tv clk;

wire highZ;

ram manager2 deconflict (.clk(sysclk), .rst(rst),

.out_ready(out_ready), .read_x(read_x),

.read y(read y), .out x(out x),

.new out(new out), .in ready(in ready),

.in_done(in_done), .in_x(in_x), .in_y(in_y),

.data_in(data_in), .addr(ram0_address),

.word(word), .data(ram0_data),

.adv(ram0 adv ld), .clk en(ram0 cen b),

.chip en(ram0 ce b), .write en(ram0 we b),

.bwrite en(ram0 bwe b), .highZ(highZ));

assign ram0 oe b=1'b0;

```

// Video Input

```

assign tv in fifo read = 1'b1;

assign tv in fifo clock = 1'b0;

assign tv in iso = 1'b1;

assign tv in reset b = ~rst;

// tv in ycrcb, tv in data valid, nalyzer4 clock = tv in clock

// tv in aef, tv in hff, and tv in aff are inputs

wire write tv prom;

// Half speed ADV7185 output clock buffer

IBUFG buf half ( .O(tv clk), .I(tv in line clock2) );

assign led = {refclk, out clk, f, rst, ram0 clk, tv in i2c clock,

tv in i2c data, sysclk; //tv in ycrcb[9:2];

wire ir1, ir0;

wire [8:0] in_x_c, in_y_c, in_x_cam, in_y_cam;

wire [35:0] data_in_c, data_in_cam;

// Instantiate the module

tvInControl2 tv2 ( .in clk(tv clk), .clk(sysclk), .rst(rst),

.lum in(tv in ycrcb[19:12]),

.chrom_in(tv_in_ycrcb[9:2]), .in_ready(ir0),

.in done(in done), .in x(in x cam),

.in y(in y cam), .data in(data in cam), .ovf(ovf),

.newFrame(f) );

assign analyzer2 clock = sysclk;

colorbar cbar1 (.clk(sysclk), .rst(rst), .in ready(ir1),

.in_x(in_x_c), .in_y(in_y_c), .data_in(data in c) );

assign in x = ~button1 ? in x c : in x cam;

assign in y = ~button1 ? in y c : in y cam;

assign data_in = ~button1 ? data_in_c : data_in_cam;

assign in ready = button3 & (~button1 ? ir1 : ir0);

assign analyzer4 clock = tv in clock;

wire ack;

wire sending;

wire [3:0] tv addr;

wire [3:0] rom addr;

wire [7:0] tv dout;

assign write tv prom = (~sending && (~button left | ~button right));

TV i2c tv prg ( .rst(rst | write tv prom), .clk(sysclk),

.i2c data(tv in i2c data),

.i2c clock(tv in i2c clock), .isAcked(ack),

.sending(sending), .byteAddr(tv addr), .dout(tv dout)

);

```

```

// Left button programs saturation and right button programs contrast

// from switch[7:0] value

assign rom addr = ~button left ? 8'd5 : ( ~button right ? 8'd8 :

8'd15 ) ;

initRAM tv prg prom( .clka(sysclk), .clkb(sysclk), .dina(switch),

.addra(rom addr), .wea(write tv prom),

.addrb(tv addr), .doutb(tv dout));

wire [7:0] lum;

wire [7:0] lum0,lum1,lum2,lum3,lum4,lum5,lum6,lum7,lum8;

reg [7:0] Cr, Cb;

wire [7:0] cr, cb;

reg [10:0] x,y;

wire [10:0] xx, yy;

reg h sync, v sync, blank;

wire hs, vs, bl;

wire hbl, vbl;

wire [7:0] vout;

read ram2 final out (.clk(out clk), .sysclk(sysclk), .rst(rst),

.new_out(new_out), .rx(read_x), .ry(read_y),

.out ready(out ready), .inx(out x), .word(word),

.h sync(hs), .v sync(vs), .blank(bl), .Cr(cr),

.Cb(cb), .lum0(lum0), .lum1(lum1), .lum2(lum2),

.lum3(lum3), .lum4(lum4), .lum5(lum5),

.lum6(lum6), .lum7(lum7), .lum8(lum8),

.out x(xx), .out y(yy));

assign analyzer4 data = {8'b0, refclk, out clk, ram0 clk, h sync,

v sync, out ready, new out, 1'b0};

assign analyzer1 data = {8'b0, word[17:10]};

assign analyzer2 data = {8'b0, lum4};

assign analyzer3 data = {8'b0, lum0};

reg [7:0] lum real;

wire [7:0] lum edge;

reg [7:0] 10,11,12,13,14,15,16,17,18;

always @(posedge refclk)begin

rstcnt<= rst ? 9'b0 : (rstcnt>=9'b11111111) ? 9'b111111111 :

rstcnt+1;

end

always @(posedge out_clk) begin

f0<=f;

// Switch the buffer select on a frame rising edge

h sync<=~hs;

v sync<=~vs;

blank<=~bl;</pre>

```

```

10<=1um0;

11<=1um1;

12<=1um2;

13<=1um3;

14<=1um4;

15<=1um5;

16<=lum6;

17<=1um7;

18<=1um8;

x < = xx;

y<=yy;

Cr<=cr;

Cb<=cb;

lum real <= ~button enter ? lum : ~button up ? lum edge : 14;</pre>

end

// Choose a new frame output at 60 Hz (both edges of frame signal)

assign nf = f \& \sim f0;

wire [23:0] rgb out;

sharpen 3 sharp1 (.clk in(out clk), .lum0(10),.lum1(11), .lum2(12),

.lum3(13), .lum4(14), .lum5(15), .lum6(16),

.lum7(17), .lum8(18), .y out(lum));

edge filt edge1 (.clk in(out clk),

.y in({10,11,12,13,14,15,16,17,18}),

.y out(lum edge) );

ycbcr_2_rgb tl (.clk_in(out_clk), .y_in(lum_real), .cb_in(Cb),

.cr in(Cr), .rgb out(rgb out));

assign vga out blue = rgb out[7:0];

assign vga out red = rgb out[23:16];

assign vga out green = rgb out[15:8];

assign vga out hsync = h sync;

assign vga out vsync = v sync;

assign vga out sync b = 1'b1;

assign vga out blank b = blank;

assign vga out pixel clock = out clk;

wire [23:0] rgb;

endmodule

```

```

module average finder(

input clk in,

// VGA clock

// global reset

input rst in,

input new frame,

// signal indicating start of frame

input pixel active,

// indicates whether pixel in frame or

blanking interval

//pixel y_value

input [7:0] data in,

output reg [7:0] y av

//average value

);

reg [22:0] y_sum = 0;

//cumulative sum

reg [6:0] sample clock = 0;

reg sample active;

reg frame reset;

always @ (*) begin

// Sampling - pixel value is not added to y sum at regularly spaced

// intervals, such that 64 samples are taken every 75 pixels

sample active = ((sample clock == 7'd3) ||

(sample clock == 7'd10) ||

(sample clock == 7'd17) ||

(sample clock == 7'd24) ||

(sample_clock == 7'd31) ||

(sample clock == 7'd37) ||

(sample clock == 7'd44) ||

(sample clock == 7'd51) ||

(sample clock == 7'd58) ||

(sample clock == 7'd65) ||

(sample clock == 7'd72))?

0 : 1;

end

always @ (posedge clk in) begin

// reset

frame reset <= new frame;</pre>

if (rst in) begin

y sum <= 0;

sample clock <= 0;</pre>

y av <= 0;

end else begin

sample clock <= (sample clock > 7'd74) ? 7'd0 :

(pixel active) ? sample_clock + 1:

sample clock;

y sum <= (frame reset) ? 0: (^data in === 1'bX) ? 0:</pre>

(sample active && pixel active) ? y sum +

data in[7:4] : y sum;

y av <= (frame reset) ? y sum >> 14: y av;

end

end

```

```

endmodule

```

```

// Engineer: j.abel

11

// Module Name: avg value

// Description: assign character addresses for frame average brightness

11

display in overlay

module avg value(

input clk in,

input [7:0] y avg,

output reg [4:0] char_tens, //address of characters

output reg [4:0] char ones

);

//character addresses

parameter ZERO = 15;

parameter ONE = 8;

parameter TWO = 14;

parameter THREE = 13;

parameter FOUR = 4;

parameter FIVE = 3;

parameter SIX = 11;

parameter SEVEN = 10;

parameter EIGHT = 2;

parameter NINE = 7;

//reg to convert average to a percentage

reg [14:0] percent big;

reg [7:0] percent;

//unclipped digits of percentage

wire [3:0] hundreds, tens raw, ones raw;

//clipped digits of percentage

reg [3:0] tens, ones;

//converts percentage to a binary-coded decimal

num2bcd conv (percent, hundreds, tens raw, ones raw);

always @ (*) begin

//percentage calculation (of 255 - max brightness of a pixel)

percent = percent big >> 8;

//output clipping

tens = (hundreds > 0) ? 4'd9 : tens raw;

ones = (hundreds > 0) ? 4'd9 : ones raw;

//character assignment

case (tens)

0: char tens = ZERO;

1: char tens = ONE;

2: char tens = TWO;

3: char tens = THREE;

4: char tens = FOUR;

5: char tens = FIVE;

```

```

6: char tens = SIX;

7: char_tens = SEVEN;

8: char tens = EIGHT;

9: char tens = NINE;

endcase

case (ones)

0: char ones = ZERO;

1: char ones = ONE;

2: char ones = TWO;

3: char ones = THREE;

4: char ones = FOUR;

5: char ones = FIVE;

6: char ones = SIX;

7: char ones = SEVEN;

8: char ones = EIGHT;

9: char ones = NINE;

endcase

end

always @ (posedge clk in) begin

//allows percentage to be converted with discrete arithmetic

percent_big <= y_avg * 100;</pre>

end

```

```

endmodule

```

```

module num2bcd(

input [7:0] percent,

output reg [3:0] hundreds,

output reg [3:0] tens_raw,

output reg [3:0] ones_raw

);

integer i;

always @ (*) begin

hundreds = 4'd0;

tens_raw = 4'd0;

ones_raw = 4'd0;

//iterative algorithm to convert to BCD (shift, add 3)

for (i=7; i>=0; i = i-1) begin

if (tens_raw >= 5)

tens raw = tens raw + 3;

```

```

if (ones_raw >= 5)

ones_raw = ones_raw + 3;

hundreds[0] = tens_raw[3];

tens_raw = tens_raw << 1;

tens_raw[0] = ones_raw[3];

ones_raw = ones_raw << 1;

ones_raw[0] = percent[i];

end

end

```

```

endmodule

```

```

// Engineer: jt. mcguire

11

// Module Name: colorbar

// Description: generates colorbars for testing

11

module colorbar(clk, rst, in_ready, in_x, in_y, data_in );

input clk, rst;

output reg in ready;

output [8:0] in x, in y;

output reg [35:0] data_in;

//pixel location

reg [8:0] hcount;

reg [8:0] vcount;

//replicates camera timing

reg [2:0] cnt;

assign in x = hcount;

assign in y = vcount;

always @(posedge clk) begin

if(rst)begin

//reset

hcount<=9'b0;</pre>

vcount<=9'b0;

data in<=36'b0;</pre>

cnt<=3'b0;

in ready<=1'b0;</pre>

end else begin

cnt<=cnt+1;</pre>

//color bar generation

if(cnt==3'b0)begin

in ready<=1'b1;</pre>

if (hcount<70) begin

```

```

hcount<=hcount+1;</pre>

data in<={8'hff, 10'b0, 8'hff, 10'b0};</pre>

vcount<=vcount;</pre>

end else if (hcount<130) begin

hcount<=hcount+1;</pre>

data in<={8'h5f, 10'haa, 8'h5f, 10'haa};</pre>

vcount<=vcount;</pre>

end else if (hcount<200) begin

hcount<=hcount+1;</pre>

data in<={8'h2f, 10'h36, 8'h2f, 10'h36};</pre>

vcount<=vcount;</pre>

end else if (hcount<311) begin

hcount<=hcount+1;</pre>

vcount<=vcount;</pre>

data in<={8'h01, 10'h01, 8'h01, 10'h01};</pre>

end else begin

hcount<=9'b0;</pre>

data_in<=data in;

if (vcount>=479) begin

vcount<=9'b0;</pre>

end else begin

vcount<=vcount+1;</pre>

end

end

end else begin

//holds values otherwise

hcount<=hcount;</pre>

data in<=data in;</pre>

vcount<=vcount;</pre>

in ready<=1'b0;</pre>

end

end

end

```

```

endmodule

```

```

input [2:0] lvl state, //Filter states from FSM

input is_edge, //Detects whether pixel on edge of frame

output reg [7:0] y_out //Single pixel out

);

parameter SOBEL = 3'd1;

parameter NOISE = 3'd2;

parameter SHARP = 3'd3;

parameter SUN = 3'd4;

// Filter Outputs

wire [7:0] y sobel, y med, y sharp, y sun;

//For edge dilation

wire current edge;

reg old edge;

//Filter module calls

edge_filt edge1(.clk_in(clk_in), .y_in(y_kern_in), .y_avg(y_avg),

.old edge(old edge), .y out(y sobel),

.current edge(current edge));

median_filt med1(.clk_in(clk_in), .y_in(y_kern_in), .y_out(y_med));

sharpen_filt sharp1(.clk_in(clk_in), .y_in(y_kern_in),

.y out(y sharp));

sun_filt sun1(.clk_in(clk_in), .y_in(y_kern_in), .lvl_state(lvl_state),

.y avg(y avg), .y out(y sun));

always @ (*) begin

//filter selection

y_out = (is_edge) ? y_kern_in[29:24]:

(conv state == SOBEL && ~is edge) ? y sobel:

(conv_state == NOISE && ~is edge) ? y med:

(conv state == SHARP && ~is edge) ? y sharp:

(conv state == SUN && ~is edge) ? y sun:

y kern in[29:24];

end

always @ (posedge clk in) begin

old edge <= current edge;</pre>

end

endmodule

// Engineer: course staff

11

// Module Name: debounce

// Description: debounces incoming button signals

11

```

```

module debounce(

```

```

input clk in,

input noisy in,

output wire clean out

);

reg [19:0] count;

reg output reg;

reg old;

assign clean out = output reg;

always @ (posedge clk in) begin

if(count == 16'd50000) begin

output reg <= old;</pre>

count <= 20'b0;

end else if(noisy in == old) begin

count <= count + 1;</pre>

end else begin

count <= 20'b0;

old <= noisy in;</pre>

end

end

```

```

endmodule

```

```

// Engineer: j. abel

11

// Module Name: edge filt

// Description: Sobel edge detection filter

11

module edge filt(

input clk in,

input [71:0] y_in, //3x3 pixel kernel

//average frame brightness

input [5:0] y_avg,

input old edge,

//indicates whether previous pixel was a

//Sobel edge

output reg [5:0] y_out,

output reg current edge //indicates that current pixel is an edge

);

parameter THRESHOLD = 8'd160; //threshold for edge detection

parameter EDGE_COLOR_TSH = 8'd160; //threshold frame brightness to

parameter THRESHOLD = 8'd160;

//determine edge display color

parameter BLACK = 8'd16;

parameter WHITE = 8'd235;

//Sums of positive and negative values in Sobel kernel

wire [9:0] g x pos;

wire [9:0] g x neg;

```

```

wire [9:0] g y pos;

wire [9:0] g y neg;

reg [7:0] edge color;

//Sobel convolution - arithmetic

assign g x pos = y in[55:48] + y in[7:0] + (y in[31:24]<<1);

assign g x neg = y in[71:64] + y in[23:16] + (y in[47:40]<<1);

assign g y pos = y in[23:16] + y in[7:0] + (y in[15:8]<<1);

assign g y neg = y in[71:64] + y in[55:48] + (y in[63:56]<<1);

//Edge color assignment

always @ (*) begin

edge color = (y avg > EDGE COLOR TSH) ? BLACK : WHITE;

end

always @ (posedge clk in) begin

//edge detection from sums

current_edge <= (((g_x_pos >= g_x_neg) &&

((q x pos-q x neq) >= THRESHOLD)) ||

((g x neg >= g x pos) &&

((g x neg-g x pos) >= THRESHOLD)) ||

((g_y_pos >= g_y_neg) &&

((g_y_pos-g_y_neg) >= THRESHOLD)) ||

((g y neg >= g y pos) &&

((g y neg-g y pos) >= THRESHOLD))) ?

1 : 0;

//output assignment

y out <= (current edge || old edge) ? edge color : y in[29:24];</pre>

end

```

```

endmodule

```

```

// Engineer: j. abel

11

// Module Name: filt sel

// Description: FSM for selecting image processing filters

11

module filt sel(

input clk in,

input 1 btn,

input r btn,

input u btn,

input d btn,

input reset,

output reg [2:0] adj_state, //controls adjustment filter

output reg [2:0] conv_state, //controls convolution filter

//controls convolution filters

//activates overlay

output reg overlay

);

```

```

// Button rising edge detection

reg l old; reg r old; reg u old; reg d old;

wire l edge; wire r_edge; wire u_edge; wire d_edge;

assign l edge = l btn & !l old;

assign r edge = r btn & !r old;

assign u edge = u btn & !u old;

assign d edge = d btn & !d old;

always @ (posedge clk in) begin

// Reset

if (reset) begin;

adj state <= 3'd0;</pre>

conv state <= 3'd0;</pre>

overlay <= 0; end

// Filter selection FSM

else begin

adj_state <= (l_edge) ? adj_state - 1: (r_edge) ? adj_state + 1:</pre>

adj state;

conv_state <= (u_edge) ? conv state + 1: (conv state == 3'd5) ?</pre>

3'd0 : conv state;

overlay <= (d edge) ? ~overlay: overlay; end</pre>

l_old <= l_btn;</pre>

r old <= r btn;</pre>

u old <= u btn;

d old <= d btn;

end

```

```

endmodule

```

```

// Engineer: j. abel

11

// Module Name: font reader

// Description: reads font character from BRAM

11

module font reader(

input clk in,

input [10:0] hcount, //pixel location

input [9:0] vcount,

input [10:0] x loc,

//location of corner of digit

input [9:0] y loc,

input [4:0] char_in, //shortened address of character

output wire is_text //indicates whether current pixel is text

);

//size parameters

parameter HEIGHT = 36;

parameter WIDTH = 32;

```

```

//actual memory address

reg[14:0] address;

reg in box;

wire pixel out;

//BRAM reader

font bram font(.clka(clk in), .addra(address), .douta(pixel out));

//prevents erroneous pixel assignment outside a box defining a digit

assign is text = (in box) ? pixel out : 0;

always @ (*) begin

//determines whether current pixel in digit box

in box = ((hcount >= x loc && hcount < (x loc+WIDTH)) &&

(vcount >= y loc && vcount < (y loc+HEIGHT))) ?</pre>

1 : 0;

//converts shortened address to actual address

address = (in box) ? ((hcount-x loc) + (vcount-y loc)*WIDTH)

+ (HEIGHT*WIDTH*char in): 0;

end

```

```

// Engineer: j.abel

11

// Module Name: level_adjustment

// Description: pixel level adjustment using linearized gamma correction

11

module level adjustment(

input clk in,

input [7:0] y in,

input [2:0] adj mode,

input [7:0] y avg,

output reg [7:0] y out

);

reg [7:0] y reg;

wire [10:0] y mult; //prevents overflow when multiplying

reg [1:0] auto mode; //mode of automatic level adjustment

// brightness levels

parameter BRIGHT3 = 3'd3;

parameter BRIGHT2 = 3'd2;

parameter BRIGHT1 = 3'd1;

parameter ZERO = 3'd0;

parameter DARK1 = 3'd7;

parameter DARK2 = 3'd6;

parameter DARK3 = 3'd5;

parameter AUTO = 3'd4;

```

```

// automatic levels and thresholds

parameter A DARK = 2'b01;

parameter A OK = 2'b00;

parameter A LIGHT = 2'b10;

parameter THR DARK = 8'd72;

parameter THR LIGHT = 8'd168;

assign y mult = y in;

always @ (*) begin

// automatic mode assignment

auto mode = (y avg > THR LIGHT) ? A DARK :

(y avg < THR DARK) ? A LIGHT : A OK;

end

always @ (posedge clk in) begin

// automatic level adjustment

if (adj_mode == AUTO) begin

case (auto mode)

A LIGHT: begin

y_out <= (y_in >= 8'd191) ? 8'd235 :

((y_mult*5)>>2)-4; end

A_DARK: begin

y_out <= (y_in < 8'd61) ? 8'd16 :</pre>

((y mult*5)>>2)-59; end

default: y out <= y in;</pre>

endcase

end else begin

// manual level adjustment - based on linear remapping

case (adj mode)

BRIGHT3: begin

y_out <= (y_in >= 8'd125) ? 8'd235 : (y_mult*2)-16;

end

BRIGHT2: begin

y out <= (y in >= 8'd162) ? 8'd235 : ((y mult*3)>>1)-8;

end

BRIGHT1: begin

y out <= (y in >= 8'd191) ? 8'd235 : ((y mult*5)>>2)-4;

end

DARK1: begin

y_out <= (y_in < 8'd61) ? 8'd16 : ((y_mult*5)>>2)-59;

end

DARK2: begin

y_out <= (y_in < 8'd90) ? 8'd16 : ((y_mult*3)>>1)-118;