# 6.111 Final Project: FPGA SDR Colin Chaney Charles Lindsay

| Introduction                                   | 3  |

|------------------------------------------------|----|

| FPGA Implementation Overview                   | 3  |

| Digital Signal Processing Chain (Charles)      | 4  |

| Overview                                       | 4  |

| SDR Input Signal Generation and Testing        | 4  |

| GNU Radio Development                          | 5  |

| Band Pass Filter Specifications                | 5  |

| Modules                                        | 6  |

| ADC (ADC_Interface.sv)                         | 6  |

| Local Oscillator (Local_Oscillator.sv)         | 7  |

| Mixer (Mixer.sv)                               | 9  |

| IIR Filter (AM_BP_filter.sv)                   | 10 |

| AM Stage 1 (implemented in top_level.sv)       | 11 |

| FM Stage 1 (FM_demod_state_1)                  | 11 |

| Peak Detect and Hold (Peak_detect_hold.sv)     | 12 |

| Audio Condition (AM_audio_condition.sv)        | 13 |

| Human Interface (Chaney)                       | 13 |

| Overview                                       | 13 |

| Displaying a Signal                            | 14 |

| Trigger_Buffer.sv                              | 14 |

| Signal Display Block Diagram Overview          | 14 |

| Function_Pixel_Logic.sv                        | 15 |

| FFT and Center Frequency Tuning (histogram.sv) | 16 |

| A Basic FFT                                    | 16 |

| A Basic Frequency Marker                       | 17 |

| Zoom Functionality                             | 18 |

| Displaying the Intermediate Frequency (IF)     | 19 |

| Waterfall Display                              | 19 |

| User Input                                     | 20 |

| Summary                                        | 23 |

| Acknowledgments                                | 23 |

| Appendix                                       | 24 |

## Introduction

Software Defined Radios (SDRs) are special in the fact that they use very few analog components. In most cases the only analog components are the RF front ends that ensure a clean analog signal is fed into the ADC of the radio. Where SDRs have an advantage to analog radios is that they are flexible. A SDR is able to apply any number of signal processing tricks with the received data and not be locked into a single solution. This can be especially useful in applications such as satellites, where being able to reconfigure hardware on orbit can be essential to mission success.

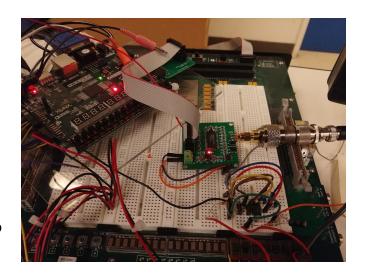

For our project, our aim was to demodulate AM and FM audio while providing an intuitive user interface. Since we realized that demodulating real RF waves off of the air would be a stretch, we wanted to focus on getting the demodulation to work with function generators. For our user interface we wanted to be able to display any waveforms coming from the ADC as well as the demodulated audio. In addition we wanted to be able to view the frequency spectrum of our incoming signal, such that we could tune the center frequency much easier and identify radio signals such as broadcast stations.

# **FPGA Implementation Overview**

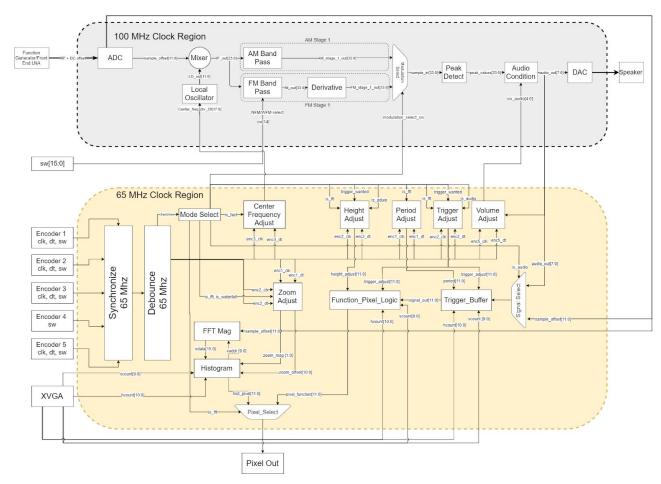

In the FPGA we have two separate clock domains, both encompassing different parts of the project. The 100 MHz clock domain focuses on the signal processing of demodulating the audio while the 65 MHz domain focuses on user interaction through encoders and a VGA display. Both the raw ADC data and the demodulated audio are sent to the display modules to be shown. The raw ADC data is also sent to a Fast Fourier Transform (FFT) module, so that users can view the entire frequency spectrum of the ADC signal.

Integration for this project was hardly an issue since the two clock domains create a pretty distinct separation between the realms. Charles was able to experiment with DSP filters and not affect any of the VGA display modules that Colin was working on.

# Digital Signal Processing Chain (Charles)

#### Overview

On a high level, the digital signal processing (DSP) chain implemented on the Artix-7 FPGA is simply an analog superheterodyne receiver. The user inputs a desired frequency to tune to, which adjusts the radio's local oscillator frequency in order to mix the received RF signal down to the intermediate frequency the bandpass filter is centered around. The resulting signal output from the bandpass filter for AM will be a single carrier frequency mixed with an audio signal. By performing envelope detection the audio signal can be extracted from the high frequency carrier. In the case of FM, more complex DSP must take place for good quality signal output, which usually consists of a phase-locked loop (PLL) digital circuit. In order to reduce complexity given our short development period, our design demodulates FM via derivative demodulation and also uses existing AM demodulation modules.

## SDR Input Signal Generation and Testing

One or two function generators were used to drive the ADC analog input for all tests and demonstrations. Analog AM and FM signals ranging from 500 kHz to 5 MHz were output to test our system over the full frequency range of its intended design. We also output audio signals from our phones to the function generator in order to play music that could be modulated over any carrier frequency to simulate an AM broadcast station.

In addition, our radio is designed to operate with an RF front end biased above 0 V, although we did not have time to design a medium wave antenna and amplifier combination to receive AM broadcast radio.

### **GNU Radio Development**

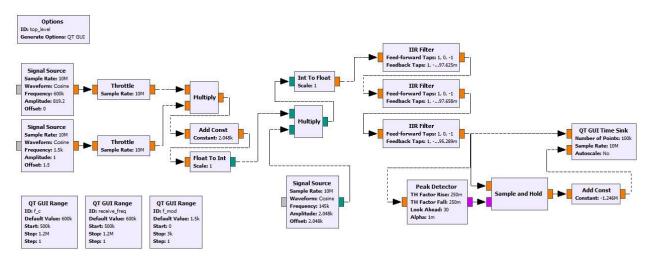

To model the complete AM demodulation from input signal generation through envelope detection, our system was simulated with GNU Radio blocks. This proved extremely useful for determining the maximum size of data passing through each module in order to help properly set our gain in our implementation and avoid overflow issues which are extremely difficult to detect in some cases. In addition, we could easily test FIR and IIR bandpass filter designs before simulating them on the FPGA which sped up the overall development process.

AM demodulation implementation built with GNU Radio.

## **Band Pass Filter Specifications**

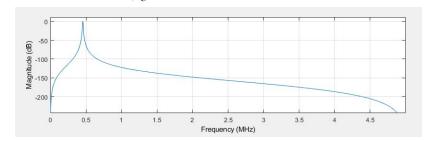

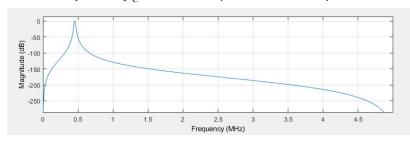

All bandpass filters were centered around the intermediate frequency  $f_C = 455~kHz$ . For FM bandpass filters, the <u>Carson Bandwidth Rule</u> was used to determine the width of the passband given the maximum frequency deviation  $\Delta f$  and audio frequency  $f_{i_{max}}$ . For narrow band FM (NFM)  $\Delta f = 5~kHz$  and  $f_{i_{max}} = 3~kHz$ , and for wideband FM (WFM)  $\Delta f = 75~kHz$  and  $f_{i_{max}} = 15~kHz$  which is typically used in US FM broadcast stations. The stopband for all filters were determined by the minimum spacing of broadcast stations in the US. The attenuation at the stop band was limited by the number of IIR filter sections we chose to implement, where more sections would have provided a steeper filter cutoff.

#### **AM Bandpass**

- Passband:  $f_{C}$  +/- 3 kHz

- Stopband:  $f_C$  +/- 5 kHz (8dB attenuation)

#### NFM Bandpass

- Passband:  $f_C$  +/- 8 kHz

- Stopband:  $f_C$  +/- 10 kHz (3dB attenuation)

#### WFM Bandpass

- Passband:  $f_C$  +/- 90 kHz

- Stopband:  $f_C$  +/- 110 kHz (3dB attenuation)

#### Modules

## ADC (ADC\_Interface.sv)

The AD9220 ADC we used has a maximum sampling rate of 10 MSPS, which limited the frequencies we could sample to below the nyquist frequency of 5 MHz. Since we were using a function generator for hardware testing and only outputting sinusoidal waveforms, we assumed that aliasing could be ignored as we could control the input spectrum.

An external breakout board for the AD9220 ADC was connected to the FPGA via two PMOD connectors. A clock divider was implemented to synthesize a 10 MHz clock which is connected directly to the PMOD port driving the ADC clock pin. The 12 data pins and out of range (OTR) pin are synchronized with two registers. Initially, the ADC module was designed to delay for four 100 MHz clock cycles after the rising edge of the synthesized 10 MHz clock before updating the module sample output. This includes two cycles to

wait for both sync register outputs to reflect the most recent signal on the ADC pin, and two cycles to wait for the ADC data to become valid per AD9220 timing requirements. As we frequently observed glitches in the ADC output, we increased the delay to ten 100 MHz clock cycles and observed no future glitches. The sample output contains a DC bias therefore can be an unsigned value, but later in the signal chain this DC bias is removed and the processed signal is centered around 0 V.

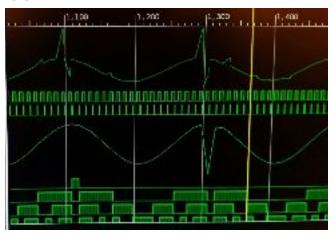

Debugging with ILA, where bottom analog waveform is the module output. An example of ADC glitch with four clock cycle delay

#### Local Oscillator (Local Oscillator.sv)

Generates a sine wave that, when mixed with the sampled data output from the ADC, shifts the frequency content a user wants to demodulate into the desired pass band. The desired center frequency  $f_c$  is set by the user through our human interface, and the local oscillator (LO) synthesizes the frequency necessary to mix this signal down to the intermediate frequency (IF) where  $f_{IF} = 455 \ kHz$  and  $f_{LO} = f_c - f_{IF}$ . This is the typical IF used in most broadcast AM receivers.

A sine wave lookup table is implemented in a ROM with an 8 bit address that corresponds to the current phase, where  $phase = \frac{2\pi*addr}{2^8-1}$  and each address contains a 12 bit value for the amplitude at that phase. In order to maintain signal resolution further down the DSP chain, the LO output must operate at 10 MSPS or greater to match the ADC sampling rate. This limits the lowest frequency we can tune our radio to since the number of samples per second will decrease as the LO frequency is decreased since the number samples n in our sine wave lookup table is constant. This can represented as  $\frac{n}{T_c} \geq 10 \, MSPS$  where  $T_c$  is the period of the sine wave being generated. Since the lowest frequency allocated to broadcast AM radio is 535 kHz, we chose to set the lowest frequency our SDR can receive to 500 kHz. This means a minimum  $f_{LO} = 45 \, kHz$ , therefore n must be at least 8 bits to maintain an output sample rate of at least 10 MSPS, so we use an 8 bit ROM address.

The top 8 bits of the 32 bit register value phase are connected to the ROM address port. Once every 100 MHz clock cycle phase is incremented by phase inc which must be less than 32 bits, where  $phase\_inc = \frac{f_{LO}}{f_{obs}}(2^{32}-1)$  . Letting parameter  $\alpha = \frac{(2^{32}-1)}{f_{obs}}$ ,  $phase\_inc = \alpha * f_{LO}$ . If we want to be able to tune to all possible center frequencies from 0 Hz to 5 MHz with 1 Hz resolution, we would need  $f_c$  to be 23 bits. This means  $f_{LO}$  would be 23 bits in the maximum case, so that limits our  $\alpha$  to a maximum of 9 bits given phase and phase inc are 32 bits. This results in a large loss of precision of the true output frequency of the LO with respect to the user set value, especially at high frequencies, due to floating point rounding errors when calculating the value of  $\alpha$  used in implementation. To implement an accurate LO,  $\alpha$  was constrained to a 14 bit value which meant our desired frequency had to be allocated to an 18 bit value now representing the desired center frequency  $f_c$  divided by 20. This is because with a frequency range of 0 Hz to 5 MHz, we can only achieve approximately 20 Hz of resolution using an 18 bit value. An error analysis in MATLAB showed that the error in desired LO frequency versus actual LO frequency increases linearly with frequency, and at 1 MHz the error is around 10 Hz if  $\alpha$  is 14 bits which we considered sufficient to ensure no loss of information occurs during the subsequent bandpass filter stages.

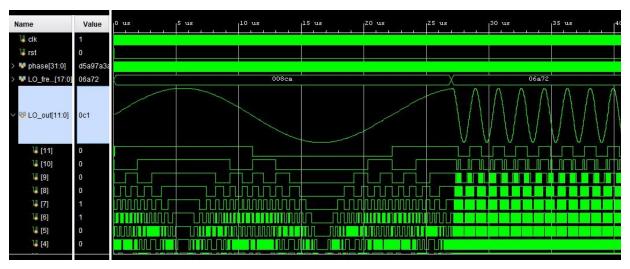

Simulation verifying LO generates signal with desired frequency, that changes once during test

## Mixer (Mixer.sv)

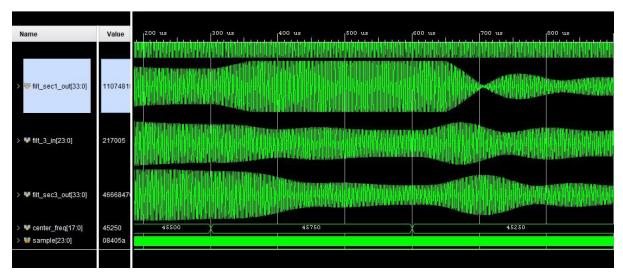

Multiples two 12 bit values, in this case the sampled data and local oscillator output where  $IF_{out} = sample\_offset * LO_{out}$ . Although a very simple implementation, this is one of the most powerful modules in the signal processing chain and produces very interesting outputs when viewed in the time domain, as seen on this synthesized ILA used to debug all stages up through mixing. This contains the desired low frequency signal and also undesired high frequency signal resulting from mixing, the latter of which must be filtered to obtain the original signal now shifted to the IF frequency of 455 kHz.

Mixer output on synthesized ILA

#### IIR Filter (AM\_BP\_filter.sv)

This filter module is used in both AM and FM demodulation, and consists of a customizable IIR filter section where any number of coefficients can be input to create an  $N^{th}$  order IIR filter.

An FIR filter was initially considered, but due to the 10 MSPS sampling rate there are only 10 clock cycles in which the summation of all filter values can be calculated as we are limited the FPGA's 100 MHz clock. This means we are limited to implementing bandpass filters with either a maximum of 10 taps if we choose to compute 1 value per clock cycle and sum with 1 register, or must use a more complicated implementation and much more hardware on the FPGA.

Given the bandpass filter specification for AM, the number of taps required is about 2000, therefore there were two proposed solutions to implement a FIR. It would be possible to downsample the IF signal to 1 MHz by first low passing to filter out high frequencies in the IF and avoid aliasing, and then after downsampling compute the output of a 400 tap FIR filter. By using four ROMS to hold filter tap coefficients and four BRAMS to hold previous sample values and operating them in parallel, you could sum 100 filter values separately over 100 clock cycles and add the four registers containing the final sums in order to compute the filter output just before the next sample arrived. This would be a fairly complex implementation and use a large amount of FPGA resources, so an IIR filter was selected as it could be easily implemented with cascaded sections each only containing 3 to 6 taps each for an AM or FM filter.

Each IIR filter consists of 1 section where  $y[n] = \sum a_k y[n-k] + \sum b_l x[n-l]$ , k = [0, N-1] and l = [1, M-1]. The feedback coefficients  $a_k$ , or denominator, and feed-forward coefficients  $b_l$  were generated in MATLAB using the Filter Designer GUI. These signed coefficients are multiplied by  $2^{16}$  and rounded to the nearest integer to eliminate some floating point precision

errors in implementation. Some nonidealities in filter implementation were still observed, for example the simulated passband attenuation for AM was approximately 2.5 dB where it was designed to be 8 dB. This is not an issue since in reality most AM broadcast stations are further apart than the filter was designed at 10 kHz spacing, since stations tend to be at least 20 kHz apart in most cities.

When computing the filter output, the x and y sums tended to grow extremely high, so there are three 100 bit registers used in each IIR filter section. A 3 section IIR bandpass filter was simulated with a 455 kHz AM signal in order to determine an appropriate number of bits for these registers to avoid overflow and set proper gains, and determine a maximum filter output value.

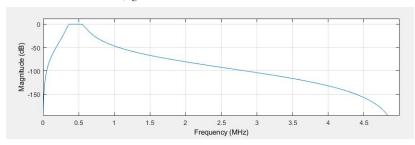

Simulation verifying output of 3 IIR filter sections for the AM bandpass filter do not overflow, and properly attenuate frequencies outside the pass band. Center\_freq varies throughout test.

#### AM Stage 1 (implemented in top level.sv)

The first stage of the AM filter is implemented in  $top\_level.sv$  and consists of 3 IIR filter sections in series to create a bandpass filter centered around the intermediate frequency (IF), where the input is  $IF_{out}$  converted to a signed value. The output of each filter is right shifted to ensure the value does not overflow when passed into the next section. See the DSP section overview for filter design specifications.

## FM Stage 1 (FM\_demod\_state\_1)

Includes both a narrow band (NFM) and wideband FM (WFM) IIR bandpass filter. The filter input comes directly from  $IF_{out}$  converted to a signed value. A push button in our human interface allows each modulation scheme to be selected.

Originally a frequency detection method by identifying zero crossings in the filtered signal was proposed, but due to the low frequency FM deviation relative to the carrier frequency it would be difficult to identify changes in frequency. For example, a 455 kHz carrier signal with 15 kHz frequency deviation will see a maximum period deviation corresponding to 7 clock cycles given our 100 MHz clock, so it would be difficult to achieve good resolution without first mixing the carrier down to a frequency close to 0 Hz and low pass filtering the signal. Due to the extra complexity in implementation, a derivative demodulation scheme was chosen to increase resolution and decrease resources.

The difference of the past two values output from the final bandpass filter section is computed and output to the peak detection module. An FM signal  $f(t) = Acos(w_ct + k Js(t))$  where s(t) is the audio signal being modulated and  $w_c$  is the carrier phase has a derivative  $\frac{df(t)}{dt} = -A(w_c + ks(t)) * sin(w_ct + k Js(t)).$  This is essentially an AM signal, which allows the FM signal to be demodulated using the same modules as AM demodulation. This reduces system complexity greatly with the downside of some noise being introduced as the signal is not a simple AM signal.

We were able to successfully demodulate FM and output a tone with the correct frequency using this demodulation method, but several harmonics were present at times in addition to the modulated frequency and were noticeable when listening to the output tone. A simple averaging filter may have helped eliminate some of this noise.

Noisy FM signal output to speaker

## Peak Detect and Hold (Peak\_detect\_hold.sv)

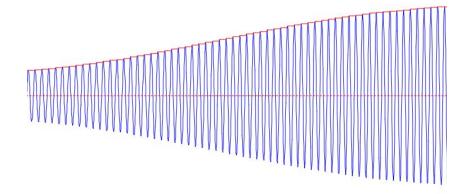

Demodulates an AM signal via envelope detection. This detects both positive and negative peaks of the signed input and will flip the sign if necessary to generate an output signal with the maximum resolution by identifying all extrema of the signal. The input signal will either be a true AM signal or FM signal derivative, both which update with a new input value at 10 MHz.

AM signal with 500 kHz carrier, generated in GNU Radio SDR simulation

The current input and previous input are used to calculate the derivative, and the sign of the derivative is encoded as a binary value and appended to an array containing only the previous 10 sign values. The sum of the array is constantly computed, and if the sum = 5 then it registers a peak has been detected. This works for both positive and negative peaks, as there will be an equal number of positive and negative derivatives surrounding a peak.

Once a peak is detected, an array of the previous 10 input values is searched to find the minimum or maximum value, which is determined by summing all values in the array. If the sum is less than zero, the algorithm will find the minimum value and set the output register to the magnitude of this value which is the value of the peak. This also effectively downsamples the signal to 0.91 MSPS, as only peaks register as valid output values and points in between are ignored.

## **Audio Condition** (AM\_audio\_condition.sv)

This module takes the output signal from the peak detect and hold module and generates a 48 kHz, 8 bit audio signal for the DAC module which converts the digital audio signal into an analog output to drive a speaker.

A clock divider is used to down sample the 0.91 MSPS input to 48 kHz. This 48 kHz signal contains a DC offset which is estimated by averaging the previous 32 audio values. The final output <code>audio\_out</code> is computed by removing the DC offset and shifting the zero centered signal according the input volume. Since <code>ds\_audio\_offset</code> is a 34 bit value, the maximum number of bits the signal must be shifted to avoid overflow during assignment to the 8 bit audio value is 26 bits, therefore <code>audio\_level</code> must be a 5 bit value.

```

audio_out <= ( (ds_audio_offset - avg) >>> ('d26 - audio_level) )

```

# Human Interface (Chaney)

#### Overview

For human interfacing, our SDR has both a VGA monitor output and a laser cut wood piece with rotary encoders. The VGA monitor works at a resolution of 1024x768 at 60 Hz. The VGA monitor is able to display the incoming raw signal from the ADC or the demodulated audio. The VGA monitor can also be used to display the frequency information of our ADC signal, telling us what types of signals are available to our radio. This frequency spectrum is capped at the nyquist frequency divided by two, which in this case is 2.5 MHz. On this screen we are able to see where our current center frequency is set to, making it easy for users to adjust to signals on the screen. In this frequency display, a user could also zoom to different areas of the spectrum and gain more clarity. We also tried to implement a waterfall display, but were unsuccessful in getting it to work as expected.

## Displaying a Signal

#### Trigger\_Buffer.sv

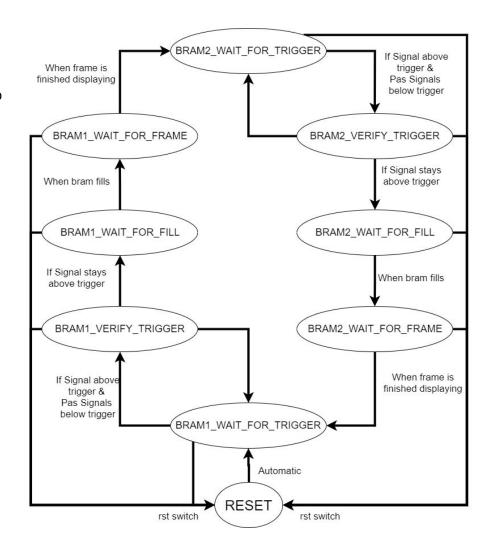

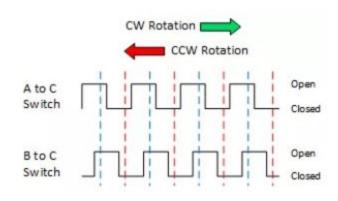

To display a signal, we had to implement a somewhat complex state machine that wrote a signal between two BRAMs. We wouldn't need a complex state machine if we didn't allow our user to change the sample rate. Allowing the user to change the sampling rate lets users see signals of varying frequencies. The general process of this state machine is that it writes to one BRAM while the display grabs data from the other BRAM. Doing this allows the display to wait until a sample of any frequency captured before displaying it.

#### Signal Display Block Diagram Overview

RESET: This is the default state when the FPGA is started. In this state we reset all the addresses to 0, the signal out to 0, and the past signal values to the trigger value (we do this so that all past values are filled before the trigger is evaluated). We go back to this state whenever the reset switch is flipped. It automatically transitions to BRAM1\_WAIT\_FOR\_TRIGGER.

BRAM1\_WAIT\_FOR\_TRIGGER: In this stage, we setup the display to read whatever signal snapshot is saved in BRAM2 (signal\_out <= data\_from\_frame2). We do that by making the address for BRAM2 dependent on the hount of the frame (frame2\_addr <= (hcount\_in - 'd101)). As you go to the right of the screen you grab later values of the BRAM. As we wait for the trigger, we write back to 20 past values. For the trigger to be satisfied, all past 20 values have to be below the trigger line and the current signal value has to be at or above the trigger line. An additional constraint is placed where the difference between the current signal and the past signal can't be too high ((signal\_in - past\_signal) < 'd1000). Having this does create issues for extremely high frequency signals, as you can jump from low to high in a matter of a few cycles. This was done to prevent noise and was considered a good tradeoff, as high frequency information is hard to visually comprehend. Once the trigger is met we move to BRAM1\_VERIFY\_TRIGGER and setup BRAM1 to be written to.

BRAM1\_VERIFY\_TRIGGER: In this stage we verify that the trigger is in fact correctly triggered. We do this by making sure that the signal value stays above the trigger line for NEEDED\_HIGH amount of samples. Once this happens we switch to the state BRAM1\_WAIT\_FOR\_FILL. During this time we write to BRAM1 in normal operation, which will be explained in BRAM1\_WAIT\_FOR\_FILL.

BRAM1\_WAIT\_FOR\_FILL: In this state we keep writing to BRAM1 until we capture the full snapshot for our display. To make the sampling period variable we have a counter and the address to BRAM1 is not changed until the counter reaches the wanted period number. BRAM1 becomes filled when the address gets to 821, as we are displaying less than 821 samples on the display.

BRAM1\_WAIT\_FOR\_FRAME: Since BRAM1 is full, we can theoretically switch it so that BRAM1 is what the display is using and BRAM2 is being written to. However, we need to wait until the frame ends to switch the BRAMs. We know the frame is over when the vocunt reaches 767.

Afterward, we repeat the same states as before but for BRAM2 being written to and BRAM1 being what is used for the display. The cycle continues over and over again, sending out the signal we want to display at any given hount.

#### Function\_Pixel\_Logic.sv

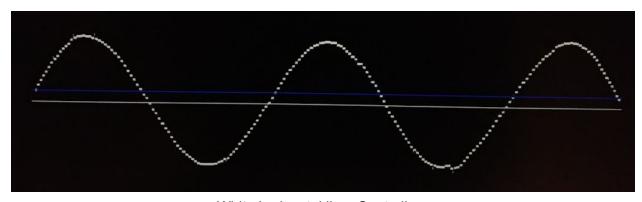

When displaying a signal on the monitor, there are three separate components. Those components are the centerline, the function/signal itself, and the trigger line. The centerline shows what the length and 0 height scale are, as such it is just a white line across the screen. We declare the centerline as {12{((vcount\_in==384) & (hcount\_in>100) & (hcount\_in<923))}}, meaning the 0 height line is at the vcount of 384 and the signal is displayed between an hcount of 101 to 922. The trigger line is very similar, but we have to scale it's height the same as we scale the signal height, which we will discuss later.

From Trigger\_Buffer we are able to get whatever signal value we are supposed to display. This signal value should change based upon the hount, as dictated in the Trigger\_Buffer module. This means we only need to focus on the height of the function and make sure we are only displaying within a certain boundary.

We first have to scale the signal height so it is matched with the user input height\_adjust. The concept of height\_adjust is that it determined the highest possible pixel height. To make this so, we multiple our signal in with our height\_adjust to form a new 24 bit value. We then bitshift this new value to the right by 11 bits so that the original height\_adjust acts like a decimal multiplier. We do the exact same scaling for the trigger line so that we can display it. Displaying between demodulated audio and the raw ADC signal has different offsets. The raw ADC signal will have a 2.5 volt offset, as driven by the function generator or RF amplifier. The audio signal will have no offset since any DC bias in removed in the audio conditioning module.

Once we have the scaled heights in pixels, the logic becomes easy. The trigger line is exactly the same as the centerline, except it's height is offset by the scaled trigger height ({4{((vcount\_in==(12'sd384 - scaled\_trigger\_height)) & (hcount\_in>100) & (hcount\_in<923))}}). The trigger line is also blue, as to differentiate it from the centerline. To display the actual signal/function we first have to make sure it is within the hcount range of the centerline. Afterward we see if our current vcount is equal to the centerline pixel height minus the scaled pixel height of the signal. To make the signal thicker we also check if it is one above or one below. If any of those conditions are met, it makes the pixel on the screen white. All in all, this results in a signal being shown that starts at the trigger line and continues until it has reached the end of the sample window

White horizontal line: Centerline Blue horizontal line: Triggerline

## FFT and Center Frequency Tuning (histogram.sv)

#### A Basic FFT

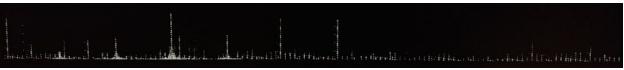

A radio is no good if you aren't able to see what types of signals you can tune to and know where you are currently tuned to. To be able to see what types of signals are available, we had to implement a fast fourier transform (FFT). This would let us see what type of frequencies were strong in the ADC signal. For actually implementing the FFT we modified the example code provided on the course website. The example code used a 4096 point FFT, which is fine for our purposes. Two big differences between our final code and the example code were that we did not oversample and we used a different clock domain. We wanted to be able to see a large spectrum, up to 2.5 MHz, which oversampling would ruin. Since our ADC interface is clocked at 100 MHz, our system clock would not be 104 MHz. In turn our ADC\_data\_valid was used in fft\_bram to signify that a fsample was valid and that fhead be incremented.

Where most of our most important changes came into play were with the fft magnitude scaling and the actual histogram pixel generator. In the fft magnitude block, a scaling factor was used to differentiate between magnitudes. After playing around with the values I found that 12'b011111111000 proved to be the best scaling value and could differentiate between noise and peaks of data the best.

Full RF Spectrum FFT

Our only initial changes to the histogram module were to move the FFT up the screen, more towards the middle, and to make the height higher for each individual bin. We accomplished the first by altering vheight such that it subtracted from a lower number, thus being higher up on the

screen (vheight = 10'd500 - vcount). The second was accomplished by making hheight be right shifted less, going from 7 to 4 (hheight = vdata >> 4;).

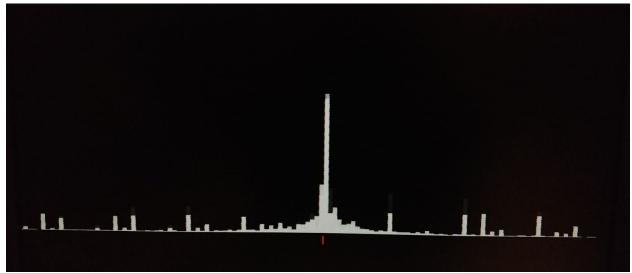

#### A Basic Frequency Marker

Making these small changes provided all of the effective functionality we needed to be able to see the frequency components of the signal from our ADC. From there we had to implement a marker that showed us what our current center frequency was. This would let us be able to tune the marker to different frequencies and hear different things.

The first step in determining where to put this marker would be to figure out how much frequency changes from pixel to pixel. Our screen takes up 1024 pixels horizontally, and in that span we cross half of our nyquist frequency, 2.5 MHz. That means that the frequency per pixel would be 'd2500000' >> 10 or around 2,441.

Our initial frequency always starts at 600 KHz. Dividing 600,000 by that number yields an initial hount position of 246. Testing this out with a 600 KHz signals shows that this math is indeed correct.

RF Spectrum FFT

From there all we had to do was adjust the position of this market based upon how our center frequency changed. Since our center frequency was mod 20, that meant we had to multiply our center frequency wire by 20 to get the real effective frequency. From there we just had to see if the difference between the current frequency and the new one was above this "spacer" value. A hard part about this though was distinguishing from negative and positive changes. For instance, center\_freq - current\_freq will be a small number if center\_freq is larger, but if it is smaller instead, the number would overflow and be a large number. That would make a positive and negative frequency appear to be the same. To combat this we put an upper limit for how much the frequency could change in a single clock cycle, that being 100 KHz. This made sense for our system, as it would be impossible for a person to change their center frequency that fast.

The current center frequency and position is adjusted when a large enough discrepancy is seen. The addition and subtraction works 1 pixel per clock cycles. This means if someone jumped multiple pixels in one clock cycle, it would take more clock cycles to register that change. This was okay for the purposes of this project as a human cannot perceive this.

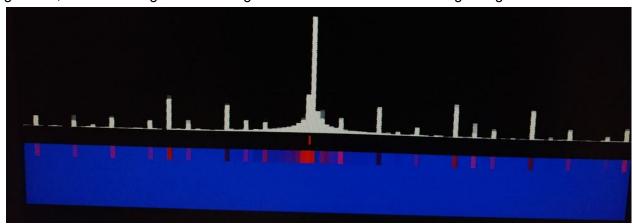

#### Zoom Functionality

Everything up to this point has created a frequency spectrum and allowed us to tune to different stations. As part of our goals we wanted to be able to zoom in on different parts of the FFT spectrum. The first part of this was to actually zoom and make the frequency window covered by the 1024 pixels shorter. This could be accomplished by bit shifting the address of the BRAM that gives us the FFT values to the right (vaddr = (hcount[9:0] >> range)). This would mean that a single address would last longer, 2 times longer in the case of a single bit shift and 4 times in the case of two bit shifts. This provided that functionality quite well.

Zoomed FFT

What was more complex was being able to change the window. Bit shifting like this made it so that we could zoom in on the smaller frequencies easier. To actually look at frequencies in the middle we had to add an offset (vaddr = (hcount[9:0] >> range) + zoom\_offset). What made this more complex is how it changed the center frequency marker. The center frequency marker position also had to be bit shifted right with range to make it scale down too. The zoom offset, however, was separate from this and had to be done before the bit shifting (display\_position = ((current\_position - zoom\_offset) << range)). The zoom offset also worked in the opposite direction for the center frequency line, as you move to the right the center frequency would move left.

Since the <code>display\_position</code> wire could overflow and display when zooming in different domains where it shouldn't. We had to better establish the frequency window we were looking at and make sure the current center frequency was in the window. The minimum on the window would be determined by the pixel/frequency resolution and what our zoom offset was. The zoom offset was representative of how far away we were from a 0 frequency in terms of pixels, so the minimum frequency was just the product of the offset and the pixel/frequency resolution (<code>min\_frequency\_window = zoom\_offset \* spacer</code>). The max frequency of the window would be the

minimum frequency of the window plus the total frequency we span in the screen (max\_frequency\_window = min\_frequency\_window + max\_frequency). This max frequency span of the screen would be determined by the original max frequency bit shifted by the zoom amount (max\_frequency = 'd2500000 >> range;). For example, if we our zoom factor was 2'b01 the max frequency span of the window would be 1.25 MHz.

What worked so well with this solution is that we didn't have to change the calculations for how the center frequency marker position changed. The relative position of the different zooms and offset was calculated independent of the position of the marker when there is no zoom and offset.

#### Displaying the Intermediate Frequency (IF)

Since our radio is a superheterodyne, there is an IF that we operate at. We wanted to be able to display this IF on the frequency spectrum if need be. We added a special marker of a different color to show this when a certain switch it flipped. The original position of this IF doesn't change, with the hount being 187. The same type of processing is applied to the IF (if\_position = ('d187 - zoom\_offset) << range;).

#### Waterfall Display

As part of our checklist we wanted to be able to have a waterfall display. We were not able to implement it fully. The concept of it was that we would set the zoom\_offset to a number closer to the center frequency and set the zoom to the maximum. We would split the screen into 8 sections horizontally and 7 sections vertically. We would take the average of the areas by having an accumulator and bit shifting it then push the values down as they change. In our waterfall display we were not able to get the averaged values to work or flow down. We were able to test our color gradient in real time on the first section of pixels vertically. In the color gradient, cold colors signified low magnitude and warm colors were high magnitude.

Waterfall Implementation Test

## **User Input**

All of the modules have talked about user inputs but not explained how they work. To make the project feel more like a real radio, we wanted to use knobs. At first we thought about using

potentiometers but decided to use rotary encoders instead. We put the rotary encoders on a laser cut piece to make the display look nice.

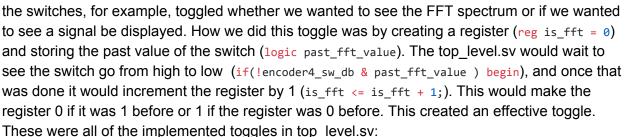

The rotary encoders had three different things they could do. They could turn clockwise, counter-clockwise, and have their switch be pressed. There are three pins important to this, those being clk, dt, and sw. All of these pins are active low. The simplest of the three is the switch, which has voltage go low whenever it is pressed.

Charles & Chaney FPGA SDR

- Is\_fast

- Fast mode for period and center frequency adjust

- Modulation select sw

- o AM or FM demodulation

- Changed LED color on FPGA so user could see what mode they were on

- Trigger\_wanted

- Adjust signal height or trigger height

- Is\_fft

- Look at FFT spectrum or signal

- Is\_audio

- Look at demodulated audio or raw signal, only works if fft mode is off

- Is\_waterfall

- Look at regular FFT or waterfall display, only works if fft mode is on

The clk, and dt pins are a little more complex. Rotary encoders work through light sources and optical sensors. The light sources go through a track that can block light or not block light. The clk and dt pins have different tracks that cause them to go high and low at different times. If you turn the encoder clockwise you will find that the clk pin goes low first and then the dt pin does low. Once a turn is completed they both go high. If you turn counter-clockwise instead the dt pin goes low first. An important note is that these encoders can be

finicky, so it was really important to synchronize and debounce them to the correct clock.

The general outline of a state machine for these switches is shown below. The idea is that we wait to see if either clk or dt pulses low first. If clk pulses low first then we increment up. If dt pulses low first then we increment down. We wait until both signals stabilize and go high before we wait to increment again.

Several versions of this were implemented in many different modules. I'll list them all briefly and talk about how each one is different.

- Control\_center\_frequency.sv

- Maximum of 18'd250\_000 and a minimum of 'd25\_000. Fast mode increments at

'd300 per tick and regular mode at 'd25 per tick.

- Control volume.sv

- Maximum of 'd26 and a minimum of 'd0 and changes at 1 per tick.

- Has a special variable is\_max to make sure that the volume does not get too loud.

It makes sure the volume is below the bit shift point that would cause the number to overflow.

- Control\_zoom\_magnitude.sv

- Maximum of 'd3 and a minimum of 'd0 and changes at 1 per tick.

- Only works if fft mode is on and waterfall is off.

- Control\_zoom\_window.sv

- Three separate state machines that depend on what the value of zoom\_magnitude is.

- o Only works if fft mode is on and waterfall is off.

- Zoom\_magnitude == 2'b00

- Zoom\_pos\_out is always 0

- Zoom magnitude == 2'b01

- Maximum of 'd503 and a minimum of 'd0 and changes at 'd10 per tick.

- Zoom magnitude == 2'b10

- Maximum of 'd779 and a minimum of 'd0 and changes at 'd20 per tick.

- O Zoom\_magnitude == 2'b11

- Maximum of 'd867 and a minimum of 'd0 and changes at 'd30 per tick.

- Control period.sv

- Maximum is 'd3950 and minimum is 'd0.

- o If in fast mode it changes at 'd20 per tick and 'd1 per tick if not

- Only works if fft mode is off.

- Control\_height

- o Two separate state machines for whether audio is on or off

- Audio off

- Maximum of 'd390 and minimum of 'd5.

- Moves at 'd10 per tick.

- Audio on

- Maximum of 'd520 and minimum of 'd3.

- Moves at 'd20 per tick.

- Only works if fft mode is off and trigger adjust is off.

- Control\_trigger\_height.sv

- Two separate state machines for whether audio is on or off

- Audio off

- Maximum of 'd4000 and minimum of 'd5.

- Moves at 'd50 per tick.

- Audio on

- Maximum of 'd3970 and minimum of 'd33.

- Moves at 'd20 per tick.

- Only works if fft mode is off and trigger adjust is on

# Summary

All in all we were able to meet a good number of our goals for the project. Where we fell short was not being able to get the waterfall display to work or getting the front end properly put together. These issues might have been resolved a bit better had we started working on the project seriously earlier.

Getting our bandpass filter to work took much longer than expected, as we were expecting to implement a simple FIR filter as we had done in previous labs until we realized that given our tight timing restraints this would not be possible. This definitely proves that it is extremely important to have a really well thought out design before implementation, or at least allow for a lot of extra time in case issues like this are encountered. Although we did start later than planned, we were able to solve major issues such as these as we did allow extra time in our schedule. It just meant that we weren't able to get some of the more experimental components like an RF front end working.

# Acknowledgments

We would like to think Gim and Joe for being great lecturers and also mentors throughout the project! We both put a lot of time into the project and enjoyed working on it, but we wouldn't have gotten it off the ground without Joe's help on the hardware side and also signal processing advice (we'd both only taken 6.003 / 16.002).

# **Appendix**

```

All code can be found at the Github link <a href="https://github.com/cmll12/FPGA">https://github.com/cmll12/FPGA</a> SDR

module top_level(

input clk_100mhz, //10 ns period

```

```

input [15:0] sw, //reset switch

input btnc, btnu, btnl, btnr, btnd,

input [5:0] jb, //ADC data in

input [7:1] ja, //ADC data in

input [7:0] jc, //Encoders

input [7:0] jd, //Encoders

output logic ja_0, //ADC clk pin

output logic led16_r,

output logic led16_g,

output logic led16_b,

output logic [15:0] led,

output logic aud_pwm,

output logic aud_sd,

output[3:0] vga_r,

output[3:0] vga_b,

output[3:0] vga_g,

output vga_hs,

output vga_vs

);

//system reset as sw[15]

logic rst;

assign rst = sw[15];

//Creates both another 100mhz clock and a 65mhz clock.

//A second 100mhz clock was needed because the original

//clock is constrained to the clkdivider

logic clk100mhz;

logic clk 65mhz;

clk_wiz_0 clkdivider(.clk_in1(clk_100mhz),

.clk_out1(clk100mhz),

.clk_out2(clk_65mhz));

```

//A wire for each pin of an an encoder that we used. In //total we had 5 encoders with three wires being important

```

//for operation, those being clk, dt, and sw.

wire encoder1_clk;

wire encoder1_dt;

wire encoder1_sw;

wire encoder2 clk;

wire encoder2_dt;

wire encoder2_sw;

wire encoder3_clk;

wire encoder3 dt;

wire encoder3_sw;

wire encoder4_sw;

wire encoder5_clk;

wire encoder5_sw;

wire encoder5_dt;

//Each of the signals are synchronized to the 65 mhz clock

//based upon their PMOD input port. We chose 65 mhz because

//most modules that need the inputs from these devices run on

//65 mhz

synchronize encoder1_clk_synchronize(

.clk(clk_65mhz),

.in(jc[0]),

.out(encoder1_clk));

synchronize encoder1_dt_synchronize(

.clk(clk_65mhz),

.in(jc[1]),

.out(encoder1_dt));

synchronize encoder1_sw_synchronize(

.clk(clk_65mhz),

.in(jc[5]),

.out(encoder1_sw));

synchronize encoder2_clk_synchronize(

.clk(clk_65mhz),

.in(jc[2]),

.out(encoder2_clk));

synchronize encoder2_dt_synchronize(

.clk(clk_65mhz),

.in(jc[3]),

.out(encoder2_dt));

```

```

synchronize encoder2_sw_synchronize(

.clk(clk_65mhz),

.in(jc[4]),

.out(encoder2_sw));

synchronize encoder3_clk_synchronize(

.clk(clk_65mhz),

.in(jc[6]),

.out(encoder3_clk));

synchronize encoder3_dt_synchronize(

.clk(clk_65mhz),

.in(jc[7]),

.out(encoder3_dt));

synchronize encoder3_sw_synchronize(

.clk(clk_65mhz),

.in(jd[2]),

.out(encoder3_sw));

synchronize encoder4_sw_synchronize(

.clk(clk_65mhz),

.in(jd[3]),

.out(encoder4_sw));

synchronize encoder5_clk_synchronize(

.clk(clk_65mhz),

.in(jd[4]),

.out(encoder5_clk));

synchronize encoder5_sw_synchronize(

.clk(clk_65mhz),

.in(jd[0]),

.out(encoder5_sw));

synchronize encoder5_dt_synchronize(

.clk(clk_65mhz),

.in(jd[5]),

.out(encoder5_dt));

//After synchronizing the signals we have to

//debounce them. These wires corespond to the

```

```

//debounces signal afterward

wire encoder1 clk db;

wire encoder1_dt_db;

wire encoder1_sw_db;

wire encoder2 clk db;

wire encoder2_dt_db;

wire encoder2_sw_db;

wire encoder3_clk_db;

wire encoder3_dt_db;

wire encoder3_sw_db;

wire encoder4_sw_db;

wire encoder5_clk_db;

wire encoder5_sw_db;

wire encoder5_dt_db;

//All of the encoder signals are debounced

debounce encoder1_clk_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder1_clk),

.clean_out(encoder1_clk_db));

debounce encoder1_dt_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder1_dt),

.clean_out(encoder1_dt_db));

debounce encoder1_sw_debounce(

.reset in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder1_sw),

.clean_out(encoder1_sw_db));

debounce encoder2_clk_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder2_clk),

.clean_out(encoder2_clk_db));

debounce encoder2_dt_debounce(

.reset in(rst),

.clock_in(clk_65mhz),

```

```

.noisy_in(encoder2_dt),

.clean_out(encoder2_dt_db));

debounce encoder2_sw_debounce(

.reset in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder2_sw),

.clean_out(encoder2_sw_db));

debounce encoder3_clk_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder3_clk),

.clean_out(encoder3_clk_db));

debounce encoder3_dt_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder3_dt),

.clean_out(encoder3_dt_db));

debounce encoder3_sw_debounce(

.reset_in(rst),

.clock in(clk 65mhz),

.noisy_in(encoder3_sw),

.clean_out(encoder3_sw_db));

debounce encoder4_sw_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder4_sw),

.clean_out(encoder4_sw_db));

debounce encoder5_clk_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder5_clk),

.clean_out(encoder5_clk_db));

debounce encoder5_sw_debounce(

.reset_in(rst),

.clock_in(clk_65mhz),

.noisy_in(encoder5_sw),

```

```

.clean_out(encoder5_sw_db));

debounce encoder5_dt_debounce(

.reset_in(rst),

.clock in(clk 65mhz),

.noisy_in(encoder5_dt),

.clean_out(encoder5_dt_db));

//This is a general code block used many times.

//The purpose is to toggle a mode of operation

//by clicking the switch on an encoder. This one

//is meant to change whether fast mode is enabled

reg is_fast = 0;

//Used to compare against past value of operation.

logic past_fast_value;

always ff @(posedge clk 65mhz) begin

//This makes sure we go from a high to a low value.

//The encoders are active low.

if(!encoder3_sw_db & past_fast_value ) begin

//If this happens then we need to change mode.

//By adding 1 the bit will either overflow or not,

//toggling between the modes

is fast \leq is fast + 1;

end

//Write past value so we can see the transition from

//high to low.

past fast value <= encoder3 sw db;

end

//Used to select if we are on AM or FM demodulation.

reg modulation select sw = 0;

logic past_modulation_value;

always_ff @(posedge clk_65mhz) begin

if(!encoder5_sw_db & past_modulation_value ) begin

modulation_select_sw <= modulation_select_sw + 1;

end

past_modulation_value <= encoder5_sw_db;</pre>

end

//Used to see if we want to change or trigger height

//or if we want to change our signal height.

reg trigger wanted = 0;

logic past_trigger_value;

```

```

always_ff @(posedge clk_65mhz) begin

if(!encoder2 sw db & past trigger value ) begin

trigger_wanted <= trigger_wanted + 1;

past_trigger_value <= encoder2_sw_db;</pre>

end

//Used to toggle the FFT or signal display

reg is fft = 0;

logic past_fft_value;

always_ff @(posedge clk_65mhz) begin

if(!encoder4_sw_db & past_fft_value ) begin

is_fft \le is_fft + 1;

end

past_fft_value <= encoder4_sw_db;</pre>

end

//Used only if we aren't display the FFT. This

//toggles whether we want to see the raw ADC in

//signal or if we want to see the demodulated

//audio signal.

reg is_audio = 0;

logic past_audio_value;

always ff @(posedge clk 65mhz) begin

//Relies on previous is_fft values so we don't switch

//it if we are in the wrong display mode.

if(!encoder1 sw db & past audio value & !is fft) begin

is_audio <= is_audio + 1;</pre>

end

past_audio_value <= encoder1_sw_db;</pre>

end

//Used only if we are displaying the FFT. This toggles

//whether we want to do the narow band waterfall or not.

//Currently the waterfall doesn't work.

reg is waterfall = 0;

logic past_waterfall_value;

always_ff @(posedge clk_65mhz) begin

//Relies on previous is_fft values so we don't switch

//it if we are in the wrong display mode.

if(!encoder1_sw_db & past_waterfall_value & is_fft) begin

is waterfall <= is waterfall + 1;

end

```

```

past_waterfall_value <= encoder1_sw_db;</pre>

end

//LED lights to help show what modulation scheme we are on

always comb begin

//If high, this means we are demodulating FM.

if(modulation_select_sw) begin

//If sw[14] is high, it means we are demodulating

//a wide band FM. Else, it is narrow band FM.

if(sw[14]) begin

//Sets color blue

led16 r \le 0;

led16_g <= 0;

led16_b <= 1;

end else begin

//Sets color green

led16_r <= 0;

led16_g <= 1;

led16_b <= 0;

end

//We are demodulating AM

end else begin

//Sets color red

led16_r <= 1;

led16_g <= 0;

led16_b <= 0;

end

end

//Wires for VGA display

wire [10:0] hcount;

// Pixel on current line

wire [9:0] vcount;

// Line number

wire hsync, vsync, blank; // Signals to output on connector

reg [11:0] rgb;

// Pixel out color

//Given module that outputs the correct timing for each signal

xvga xvga1(.vclock_in(clk_65mhz),.hcount_out(hcount),.vcount_out(vcount),

.hsync_out(hsync),.vsync_out(vsync),.blank_out(blank));

//Setup speaker output

assign and sd = 1;

//ADC variables

```

```

logic [11:0] sample; //The actual output of the ADC

logic ADC_data_valid; //Goes high if data is valid

logic B1,B2,B3,B4,B5,B6,B7,B8,B9,B10,B11,B12; //Specific raw bits out

logic ADC_clk_gen;

//The clock we send out to get the ADC working

logic OTR;

//Overflow bit

//Map ADC pins to FPGA PMOD pins

assign B1 = ia[3];

assign B2 = ia[5];

assign B3 = ja[7];

assign B4 = jb[1];

assign B5 = jb[3];

assign B6 = jb[5];

assign B7 = jb[4];

assign B8 = jb[2];

assign B9 = jb[0];

assign B10 = ja[6];

assign B11 = ja[4];

assign B12 = ja[2];

assign OTR = ja[1];

assign ja_0 = ADC_clk_gen; //10MHz clock output from ADC interface

//Variable used for the center frequency

logic [17:0] center_freq_div_20;

//Module that adjusts the center frequency based on the knob inputs

control_center_frequency adjust_frequency(

.clk(clk_65mhz),

.right(encoder3_clk_db),

.left(encoder3_dt_db),

.reset(rst),

.center_frequency_out(center_freq_div_20),

.is_fast(is_fast));

logic [4:0] sw_audio;

//Determine audio level

logic signed [7:0] DAC_audio_in; //Audio sent to DAC

//Sets the volume based on the knob inputs and the current DAC value

control_volume(

.clk(clk 65mhz),

.up(encoder5_clk_db),

```

```

.down(encoder5_dt_db),

.reset(rst),

.DAC_in(DAC_audio_in),

.volume_out(sw_audio));

//Interface with AD9220

ADC Interface AD9220 (.clk 100mhz(clk100mhz),.rst(rst),.sample offset(sample),

.ADC_data_valid(ADC_data_valid),.ADC_clk(ADC_clk_gen),.B1(B1),.B2(B2),

.B3(B3),.B4(B4),.B5(B5),.B6(B6),.B7(B7),.B8(B8),.B9(B9),.B10(B10),

.B11(B11),.B12(B12),.out_of_range(OTR));

//Local Oscillator

logic [11:0] LO_out;

Local_Oscillator LO (.rst(rst), .clk_in(clk100mhz),.center_freq_div_20(center_freq_div_20),

.LO_out(LO_out));

//Mixer

logic [23:0] IF out;

Mixer sample_LO_mixer (.in_a(sample),.in_b(LO_out),.p_out(IF_out));

//convert mixer IF out to signed integer

logic signed [23:0] IF signed;

assign IF\_signed = {\sim}IF\_out[23], IF\_out[22:0]};

//FM Demodulation Stage 1 (BP filter and derivative)

logic signed [33:0] FM_stage_1_out;

logic FM_sample_ready;

FM_demod_stage_1 FM_stage_1

(.clk(clk100mhz),.rst(rst),.IF_in(IF_signed),.IF_data_valid(ADC_data_valid),

.FM_BP_width(sw[14]),.FM_derivative_out(FM_stage_1_out),.FM_data_valid(FM_sample_read

y));

//end FM demod stage 1 -----

//AM Demodulation Stage 1 (BP filter)

//AM Bandpass Filter

//section 1 -----

//initialize coeffs

```

```

parameter N = 3;

logic signed [17:0] b1 [(N-1):0]; //N b feedforward coeffs [b(N-1)...b0), unpacked array

logic signed [17:0] a1 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

assign b1 [(N-1):0] = '{-18'sd65536,18'sd0,18'sd65536}; //b coeff MATLAB: [1,0,-1]

assign a1 [(N-2):0] = '{18'sd65380,-18'sd125527}; //a coeff MATLAB:

logic signed [33:0] filt_sec_1_out;

logic sec_1_ready;

//triggers on ADC sample valid

AM_BP_Filter #(.N(N)) AM_BP_sec_1 (.clk_in(clk100mhz),.rst(rst),.b(b1),.a(a1),

.sample_ready(ADC_data_valid),.sample(IF_signed),.filt_out(filt_sec_1_out),.filt_valid(sec_1_re

ady));

//section 2 -----

//same N as section 1

logic signed [23:0] filt sec 2 in;

//divide output from filter section 1 by 2^11 to fit 24 bit input parameter

assign filt_sec_2_in = (filt_sec_1_out>>>11);

//initialize coeffs

logic signed [17:0] b2 [(N-1):0]; //N b feedforward coeffs [b(N-1)...b0), unpacked array

logic signed [17:0] a2 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

assign b2 [(N-1):0] = '{-18'sd65536,18'sd0,18'sd65536}; //b coeff MATLAB: [1,0,-1]

assign a2 [(N-2):0] = '{18'sd65383,-18'sd125680}; //a coeff MATLAB:

logic signed [33:0] filt_sec_2_out;

logic sec_2_ready;

AM_BP_Filter #(.N(N)) AM_BP_sec_2 (.clk_in(clk100mhz),.rst(rst),.b(b2),.a(a2),

.sample_ready(sec_1_ready),.sample(filt_sec_2_in),.filt_out(filt_sec_2_out),.filt_valid(sec_2_rea

dy));

//section 3 -----

//same N as section 1

logic signed [23:0] filt_sec_3_in;

//divide output from filter section 1 by 2^11 to fit 24 bit input parameter

```

```

assign filt_sec_3_in = (filt_sec_2_out>>>11);

//initialize coeffs

logic signed [17:0] b3 [(N-1):0]; //N b feedforward coeffs [b(N-1)...b0), unpacked array

logic signed [17:0] a3 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

assign b3 [(N-1):0] = '{-18'sd65536,18'sd0,18'sd65536}; //b coeff MATLAB: [1,0,-1]

assign a3 [(N-2):0] = '{18'sd65227,-18'sd125456}; //a coeff MATLAB:

logic signed [33:0] AM_stage_1_out;

logic AM_sample_ready;

AM_BP_Filter #(.N(N)) AM_BP_sec_3 (.clk_in(clk100mhz),.rst(rst),.b(b3),.a(a3),

.sample_ready(sec_2_ready),.sample(filt_sec_3_in),.filt_out(AM_stage_1_out),.filt_valid(AM_sa

mple_ready));

//end AM demod stage 1 ------

//AM and FM Demodulation stage 2 (peak detect and audio condition)

//Modulation_select_sw, sw[5], determines which demod to use (0 = AM, 1 = FM)

logic signed [33:0] peak_detect_sample_in;

logic peak detect sample ready;

always_comb begin

if (!modulation_select_sw) begin

peak _detect_sample_ready = AM_sample_ready;

peak_detect_sample_in = AM_stage_1_out;

end else begin

peak_detect_sample_ready = FM_sample_ready;

peak_detect_sample_in = FM_stage_1_out;

end

end

//Peak Detect and Hold

//magnitude of peak values of signal

logic [34:0] peak_values;

logic peak_ready;

Peak_detect_hold AM_peak_detect

(.clk(clk100mhz),.rst(rst),.sample_ready(peak_detect_sample_ready),

.sample_in(peak_detect_sample_in),.peak_value(peak_values),.sample_ready_out(peak_ready

));

```

```

//Audio Condition

//output to DAC module

AM audio condition condition AM for DAC

(.clk(clk100mhz),.rst(rst),.audio_offset(peak_values>>2),.audio_level(sw_audio),

.audio_out(DAC_audio_in));

//ila -----

fm_stage_1_ila ila_fm_stage_1

(.clk(clk100mhz),.probe0(filt_sec_6_out),.probe1(filt_sec_5_out));

//end demod stage 2 -----

//Drive DAC with demodulated audio

logic pwm_val;

DAC_stuff (.clk_in(clk100mhz), .rst_in(rst), .level_in({~DAC_audio_in[7],DAC_audio_in[6:0]}),

.pwm_out(pwm_val));

assign aud pwm = pwm val?1'bZ:1'b0;

//VGA Stuff

//The height_adjust is used to see what relative height

//is wanted when displaying signals

logic [11:0] height_adjust;

control_height my_height(

.clk(clk_65mhz),

.up(encoder2_clk_db),

.down(encoder2_dt_db),

.reset(rst),

.sw(trigger_wanted),

.is_audio(is_audio),

.is_fft(is_fft),

.height_out(height_adjust));

//The trigger_adjust is used to set the trigger level

//of the signals.

logic [11:0] trigger_adjust;

control_trigger_height my_trigger(

.clk(clk_65mhz),

```

```

.up(encoder2_clk_db),

.down(encoder2_dt_db),

.reset(rst),

.sw(trigger_wanted),

.is_audio(is_audio),

.is_fft(is_fft),

.height_out(trigger_adjust));

//This sets the period we wait between taking samples.

//Having a higher period lets people see lower frequency

//signals

logic [11:0] period;

control_period my_period(

.clk(clk_65mhz),

.is_fast(is_fast),

.right(encoder1_clk_db),

.left(encoder1_dt_db),

.reset(rst),

.is_fft(is_fft),

.period_out(period));

//In the case where we want to display a signal, we

//need to decide between the demodulated audio or the

//raw ADC signal

logic [11:0] signal_to_display;

always_comb begin

//Sets correct signal based on what the user wants

//to display

if(is_audio) begin

signal_to_display = {DAC_audio_in, 4'b0};

end else begin

signal_to_display = sample;

end

end

//The display signal is what actually gets sent to the

//display. Why this is different is because we want to

//buffer our signal between two brams. This lets us see

//signals of varying frequencies.

logic [11:0] display_signal;

trigger_buffer my_buffer(.clock_in(clk_65mhz),.reset_in(rst),

.signal_in(signal_to_display),

.trigger_height(trigger_adjust),

```

```

.hcount_in(hcount),.vcount_in(vcount),

.period(period),

.signal_out(display_signal));

//Based on the display signal, this module gives us what

//the pixel color should be for any given point on the screen.

wire [11:0] pixel_function;

function_pixel_logic plot(.vclock_in(clk_65mhz),.reset_in(rst),

.height_adjust(height_adjust),

.signal_in(display_signal),

.trigger_height(trigger_adjust),

.hcount_in(hcount),.vcount_in(vcount),

.is_audio(is_audio),

.pixel_out(pixel_function));

//A border on the display is created. This is there to auto

//adjust the display easier

wire border = (hcount==0 | hcount==1023 | vcount==0 | vcount==767 |

hcount == 512 \mid vcount == 384);

//Registers for the blanking, horizontal sync, and vertical sync signals.

//This is here in case there is some pipelining.

reg b,hs,vs;

//FFT Stuff

// INSTANTIATE SAMPLE FRAME BLOCK RAM

// This 16x4096 bram stores the frame of samples

// The read port is read by the bram to fft module and sent to the fft.

logic fwe;

// Whether or not we want to write to the bram

logic [11:0] fhead = 0; // Frame head - a pointer to the write point, works as circular buffer

logic [15:0] fsample; // The sample data from the ADC

logic [11:0] faddr; // Frame address - The read address, controlled by bram to fft

logic [15:0] fdata; // Frame data - The read data, input into bram_to_fft

fft_bram bram1 (

.clka(clk100mhz),

.wea(fwe),

.addra(fhead),

.dina(fsample),

.clkb(clk100mhz),

.addrb(faddr),

.doutb(fdata));

```

```

//If the ADC is valid we want to icrement fhead to move to the next

//position. Will overflow with time.

always_ff @(posedge clk100mhz) begin

if (ADC_data_valid) begin

fhead <= fhead + 1;

end

end

//Write only when we finish a valid sample.

assign fwe = ADC_data_valid;

//Switch the input into the bram between the IF and the signal.

//Used for demonstration purposes.

always_comb begin

if(sw[1]) begin

fsample = IF_out[23:10];

end else begin

fsample = {sample, 2'b0};

end

end

//SAMPLE FRAME BRAM READ PORT SETUP

//For this project, we just need to display the FFT on 60Hz video, so let's only send the frame

of samples

//once every 60Hz.

//Synchronize the vsync to 100mhz since it is on 65mhz

logic vsync 100mhz, vsync 100mhz pulse;

synchronize vsync_synchronize(

.clk(clk100mhz),

.in(vsync),

.out(vsync_100mhz));

//Since vsync goes low when active, we must invert to make it a pulse.

level_to_pulse vsync_ltp(

.clk(clk100mhz),

.level(~vsync_100mhz),

.pulse(vsync_100mhz_pulse));

// INSTANTIATE BRAM TO FFT MODULE

// This module handles the magic of reading sample frames from the BRAM whenever start is

asserted.

// and sending it to the FFT block design over the AXI-stream interface.

logic last_missing; // All these are control lines to the FFT block design

```

```

logic [31:0] frame tdata;

logic frame tlast, frame tready, frame tvalid;

bram_to_fft bram_to_fft_0(

.clk(clk100mhz),

.head(fhead),

.addr(faddr),

.data(fdata),

.start(vsync_100mhz_pulse),

.last missing(last missing),

.frame_tdata(frame_tdata),

.frame tlast(frame tlast),

.frame tready(frame tready),

.frame_tvalid(frame_tvalid)

);

// This is the FFT module, implemented as a block design with a 4096pt, 16bit FFT

// that outputs in magnitude by doing sqrt(Re^2 + Im^2) on the FFT result.

// It's fully pipelined, so it streams 4096-wide frames of frequency data as fast as

// you stream in 4096-wide frames of time-domain samples.

logic [23:0] magnitude tdata; // This output bus has the FFT magnitude for the current index

logic [11:0] magnitude_tuser; // This represents the current index being output, from 0 to 4096

logic magnitude_tlast, magnitude_tvalid;

fft mag fft mag i(

.clk(clk100mhz),

.event_tlast_missing(last_missing),

.frame_tdata(frame_tdata),

.frame tlast(frame tlast),

.frame_tready(frame_tready),

.frame_tvalid(frame_tvalid),

.scaling(12'b011111111000),

.magnitude tdata(magnitude tdata),

.magnitude_tlast(magnitude_tlast),

.magnitude_tuser(magnitude_tuser),

.magnitude_tvalid(magnitude_tvalid));

// Let's only care about the range from index 0 to 1023, which represents frequencies 0 to

omega/2

// where omega is the nyquist frequency (sample rate / 2)

logic in_range = ~[magnitude_tuser[11:10]; // When 13 and 12 are 0, we're on indexes 0 to

1023

// INSTANTIATE HISTOGRAM BLOCK RAM

// This 16x1024 bram stores the histogram data.

```

```

// The write port is written by process fft.

// The read port is read by the video outputter or the SD care saver

// Assign histogram bram read address to histogram module unless saving

logic [9:0] haddr; // The read port address

logic [15:0] hdata; // The read port data

histogram_bram bram2 (

.clka(clk100mhz),

.wea(in range & magnitude tvalid), // Only save FFT output if in range and output is valid

.addra(magnitude tuser[9:0]),

// The FFT output index, 0 to 1023

.dina(magnitude_tdata[15:0]),

// The actual FFT magnitude

.clkb(clk100mhz), // input wire clkb used to be clk 65mhz

.addrb(haddr),

// input wire [9:0] addrb

.doutb(hdata)

// output wire [15:0] doutb

);

//This module controls how much we zoom in on the FFT.

logic [1:0] fft_zoom_mag;

control_zoom_magnitude my_zoom(

.clk(clk_65mhz),

.up(encoder2 clk db),

.down(encoder2_dt_db),

.reset(rst),

.is fft(is fft),

.is_waterfall(is_waterfall),

.zoom_out(fft_zoom_mag));

//This module controls the offset where we are zooming

//in on. This in effect determine the windows of our zoom.

logic [9:0] zoom offset;

control_zoom_window my_zoom_window(

.clk(clk 65mhz),

.up(encoder1_clk_db),

.down(encoder1_dt_db),

.reset(rst),

.is_fft(is_fft),

.is_waterfall(is_waterfall),

.zoom_magnitude(fft_zoom_mag),

.zoom_pos_out(zoom_offset));

//Module that outputs the pixel for the FFT.

//Includes other logic for the center frequency line

//and waterfall display.

logic [12:0] hist_pixel;

```

```

logic [1:0] hist_range;

histogram fft_histogram(

.clk(clk_65mhz),

.rst(rst),

.hcount(hcount),

.vcount(vcount),

.blank(blank),

.range_in(fft_zoom_mag), // How much to zoom on the first part of the spectrum

.vaddr(haddr),

.vdata(hdata),

.freq(center_freq_div_20),

.is_if(sw[1]),

.is_waterfall(is_waterfall),

.zoom_offset_in(zoom_offset),

.pixel(hist_pixel));

// VGA OUTPUT

always_ff @(posedge clk_65mhz) begin

//No pipelining so the signals are the same

hs <= hsync;

vs <= vsync;

b <= blank;

//If we want to display the fft the pixel is

//whaterver we get from the histogram module

if(is_fft) begin

rgb <= hist_pixel;

end else begin

//otherwise, if sw[0] is on we want to show

//our border for display calibration

if (sw[0]) begin

rgb <= {12{border}};

//If not, then we display whatever signal

end else begin

rgb <= pixel_function;

end

end

end

//Assign connector values accordingly.

assign vga_r = ~b? rgb[11:8]: 0;

assign vga_g = \sim b ? rgb[7:4] : 0;

assign vga_b = \sim b ? rgb[3:0] : 0;

```

```

assign vga_hs = \sim hs;

assign vga_vs = ~vs;

endmodule

module ADC Interface(

input clk_100mhz, //10 ns period

input rst, //system reset

output logic [11:0] sample_offset, //most recent sample, 0-4095

output logic ADC_data_valid, //triggered high at 10 MHz, otherwise off

//ADC I/O

output logic ADC_clk, //ADC clk pin

input B1,B2,B3,B4,B5,B6,B7,B8,B9,B10,B11,B12,//bits 1-12 from ADC

input out_of_range

);

//format ADC values in array, including out of range bit

logic [12:0] raw_values;

assign raw_values[12:0] = {out_of_range, B1,B2,B3,B4,B5,B6,B7,B8,B9,B10,B11,B12};

//10 mhz clk (100 ns) with 50% duty cycle with rising edge synced with 100mHz clk

//rising edge. ADC sample rate = 10 MSPS

logic clk 10mhz;

logic [3:0] clk_count;

assign ADC_clk = clk_10mhz;

//trigger every time clk 10mhz goes high while creating 50% DC 10mhz clk

logic trigger;

always_comb begin

if (!rst) begin

if (clk count \leq 4) clk 10mhz = 1;

else clk_10mhz = 0;

end else

clk\ 10mhz = 0;

always_ff @(posedge clk_100mhz) begin

if (!rst) begin

//reset clk every 10 counts of 100mHz clk, otherwise increment

if (clk_count == 9) begin

clk_count <= 0;

trigger <= 1;

end else begin

clk_count <= clk_count + 1;

```

```

trigger <= 0;

end

end else begin

clk_count <= 9;

trigger <=0;

end //end else

end //end always_ff

//sync ADC pins by passing input through 2 registers

//registers for syncing ADC input data

logic [12:0] prev_data;

logic [12:0] sync_data;

always_ff @(posedge clk_100mhz) begin

if (rst) begin

prev_data <= 13'b0;

sync_data <= 13'b0;

end else begin

//sync all 12 input pins with 2 registers

for (int i=0; i<=12; i=i+1) begin

prev_data[i] <= raw_values[i];

sync_data[i] <= prev_data[i];</pre>

end //for

end //rst else

end //always_ff

//updates ouput value once ADC data has become valid

//AND passes through 2 registers (waits 10 clk periods for

//data valid, + 2 clk periods for sync registers. So delay_period = 2,

//which grabs value at 10 ns after last ADC clk high

//Asserts ADC data valid once new data is valid

parameter delay_period = 'd2;

logic [3:0] count;

always_ff @(posedge clk_100mhz) begin

if (rst) begin

count <= delay_period + 1; //ensures data won't become valid until after first trigger

sample_offset[11:0] <= 12'h000;

ADC_data_valid <= 0;

end else begin

if (trigger) begin

count <= 1;

end else begin

//once waited for 2 clk periods...

```

```

if (count == delay_period) begin

//assert data valid

ADC_data_valid <= 1;

//ouput ADC synced data if not out of range, otherwise output max value

sample_offset[11:0] <= !sync_data[12] ? sync_data[11:0] : 12'hFFF;</pre>

end else ADC_data_valid <= 0;

//just keep counting....should be okay becuase trigger will always reset count before it

overflows

count <= count + 1;

end //end trigger else

end //rst else

end //end always ff

Endmodule

module AM_BP_Filter #(parameter N = 8) //N = number of feedforward coeff, max 8

(

input clk_in,

input rst,

//coeffiecients multiplied by 2^16

input signed [17:0] b [(N-1):0], //N b feedforward coeffs [b(N-1)...b0), unpacked array

input signed [17:0] a [(N-2):0], //N-1 feedback coeffs [a(N-1)...a1], unpacked array

input sample_ready, //ADC data valid

input signed [23:0] sample, //IF_in

output logic signed [33:0] filt_out,

output logic filt_valid //indicate new filter value available

);

logic signed [23:0] x [7:0]; //store past 8 x values, up to and including x[n]

logic signed [100:0] y [7:0]; //store past 8 y values up to and inlcuding y[n-1]

//pointer to x[n] and y[n-1] in x and y arrays

logic [2:0] index;

//indicate begin calculating filter ouput

logic sum_values;

//used in computing x and y terms for filter output

```

```

logic signed [100:0] x_sum;

logic signed [100:0] y_sum;

logic [3:0] ii;

//ensures index overflow does not result in calling x or y at a negative val

logic [2:0] val_index;

assign val_index = index - ii;

always_ff @(posedge clk_in) begin

if (rst) begin

//intialize x & y values to all 0

for (int i=0; i<8; i=i+1) begin

x[i] <= 0;

y[i] <= 0;

//reset x and y sums

x_sum \le 0;

y_sum <= 0;

end

//reset current value pointer

index \leq 0;

end else begin

if (sample_ready) begin

//update x with most recent sample

x[index] \le sample[23:0];

//start computing filter output, reset sums

sum_values <= 1;

//reset sum values

x_sum <= 0;

y_sum <= 0;

//increment pointer index

index <= index+1;

//start ii at 1, since incrementing index

//therefore x[n] is at [index-1]

ii <= 1;

end else begin //sample ready

//calculate x and y sums for past N values

if (sum_values && (ii <= N)) begin

x_sum \le x_sum + ((x[val_index]*b[ii-1])>>>16);

//only summing N-2 y terms

y_sum <= (ii <= (N-1)) ? ( y_sum + ( (y[val_index]*a[ii-1])>>>16 ) ) : y_sum;

ii <= ii + 1;

end else if (sum_values) begin

//stop summation

```

```

sum_values <= 0;

//compute filt_out

filt_out <= x_sum - y_sum;

filt_valid <= 1;

//store this to be used as previous value of y

y[index] <= x_sum - y_sum;

end else begin

filt valid \leq 0;

end //sum values

end //else sample ready

end //rst else

end //end always_ff

Endmodule

module AM_audio_condition(

input clk, //should be 100 MHz for proper sampling

input rst,

//signal from peak detect, 10 MSPS

input [33:0] audio offset,

//audio level, set by 3 switches

input [4:0] audio_level,

//8 bit audio signal, centered at 0

output logic signed [7:0] audio_out

);

//downsample to 48 khz ------

parameter COUNT_48k = 2082;

logic [11:0] count;

logic trigger;

//down-sampled, amplitude adjusted audio (48kHz). Still contains DC offset and is 24 bits

logic [33:0] ds_audio_offset;

//trigger once every COUNT_48k cycles

assign trigger = (count == COUNT_48k);

//HP filter trigger

logic sample_ready;

always_ff @(posedge clk) begin

if (rst) count \leq 0;

```

```

else begin

//rst count every COUNT_48k periods of 100MHz clock for 48kHz sample rate

if (trigger) begin

count \leq 0;

ds_audio_offset <= audio_offset;</pre>

sample_ready <= 1;

end else begin

sample ready <= 0;

count <= count + 1;

end //else trigger

end //else rst

end

//Moving average to compute audio offset

//array of past peak detect outputs

logic [33:0] window [31:0];

//current index in window

logic [4:0] index;

logic [5:0] sum_i; //index for computing sum

logic [38:0] sum; //sum of values in window

logic [33:0] avg; //average value of window

always_ff @(posedge clk) begin

if (rst) begin

//initialize all values in window to 0

for (int i=0; i<32; i=i+1) begin

window[i] \le 0;

end

//reset index

index \leq 0;

sum i \le 0;

sum \le 0;

end else begin //rst else

if (sample_ready) begin

//store current down sampled offset audio

window[index] <= ds_audio_offset;</pre>

index \le index + 1;

sum <= 0;

sum_i <= 0;

end else begin

//no sample, still computing avg

if (sum i < 32) begin

sum <= sum + window[sum_i];</pre>

```

```

sum_i = sum_i + 1;

end if (sum_i == 32) begin //done computing avg

sum_i <= 33; //causes system to stay in next else condition until ready to compute

sum again

avg <= (sum >> 5); //divide sum by 32 (# of window values) to get average

end else begin

//Shift level of audio and shrink to 8 bit value

//uses ds audio offset grabbed when sample ready = 1

//shifts between 20 and 6 bits (since max audio level = 15)

audio_out <= ( (ds_audio_offset - avg) >>> ('d26 - audio_level) );

end //sum i < 32

end //sample_ready else

end //rst

end //always_ff

Endmodule

module DAC_stuff(input clk_in, input rst_in, input [7:0] level_in, output logic pwm_out);

//PWM generator for audio generation

logic [7:0] count;

assign pwm_out = count<level in;

always ff @(posedge clk in)begin

if (rst_in)begin

count <= 8'b0;

end else begin

count <= count+8'b1;</pre>

end

end

Endmodule

module FM_demod_stage_1(

input clk,

input rst,

//ouput from RF mixer

input signed [23:0] IF_in,

//driven by ADC_data_valid

input IF_data_valid,

//if 1, use wideband FM, if 0, use narrowband FM

input FM BP width,

//derivative of band passed FM signal

```

```

output logic signed [33:0] FM_derivative_out,

output logic FM_data_valid

);

parameter N = 3;

logic signed [17:0] a1 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

logic signed [17:0] a2 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

logic signed [17:0] a3 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

logic signed [17:0] a4 [(N-2):0]; //N-1 feedback coeffs [a(N-1)...a1], unpacked array

//select NFM or WFM

always comb begin

if (FM_BP_width) begin

//FM (Wideband) Bandpass Filter

a1 [(N-2):0] = '{18'sd61600,-18'sd119464}; //a coeff MATLAB:

a2 [(N-2):0] = '{18'sd62943,-18'sd125245}; //a coeff MATLAB:

a3 [(N-2):0] = '{18'sd57240,-18'sd117002}; //a coeff MATLAB:

a4 [(N-2):0] = '{18'sd58551,-18'sd120066}; //a coeff MATLAB:

end else begin

//FM (narrowband) bandpass filter

a1 [(N-2):0] = '{18'sd64789,-18'sd124533}; //a coeff MATLAB:

a2 [(N-2):0] = '{18'sd64853,-18'sd125569}; //a coeff MATLAB:

a3 [(N-2):0] = \frac{18}{300} = \frac

a4 [(N-2):0] = \frac{18}{3855}, -18\frac{34342}{4342}; //a coeff MATLAB:

end //if narrow or wide

end //always_comb