# 6.111 Final Project:Freeform Production of Gorgeous Audio

Rahul Yesantharao and Jacob Pritzker

# **Table of Contents**

| I. Overview / Motivation:                                         | 4   |

|-------------------------------------------------------------------|-----|

| II. Total System Diagram                                          | 5   |

| III. Major Modules                                                | 5   |

| A. Keyboard (Jacob)                                               | 5   |

| B. MIDI Keyboard Interface (Jacob)                                | 6   |

| C. VGA Display (Jacob)                                            | 8   |

| D. Song Creation (Jacob)                                          | 12  |

| E. Game Logic (Rahul)                                             | 13  |

| F. Song Select Module (Rahul)                                     | 14  |

| G. Learning Mode (Rahul)                                          | 15  |

| H. Microphone Input (Rahul)                                       | 16  |

| H.i. FFT Calculation                                              | 17  |

| H.ii. FFT Analysis                                                | 19  |

| I. Top Level                                                      | 21  |

| J. Miscellaneous Modules (Menu, Timer, Score Calculation) (Rahul) | 22  |

| IV. Trickiest Pieces of the Project                               | 23  |

| V. Lessons Learned / Advice for Future Projects                   | 25  |

| Appendix A: Verilog Code                                          | 28  |

| top_level.sv                                                      | 28  |

| game_controller.sv                                                | 45  |

| menu.sv                                                           | 59  |

| create_song.sv                                                    | 60  |

| keyboard.sv                                                       | 62  |

| UART_decoder.sv                                                   | 71  |

| VGA_helper.sv                                                     | 81  |

| fft_analyzer.sv                                                   | 100 |

| fft_sampler.sv                                                    | 109 |

| timer.sv                                                          | 112 |

| hann.sv                                                           | 114 |

| nexys4ddr_audio.xdc                                               | 114 |

| Appendix B: Python Scripts                                        | 125 |

| create_song_coe.py                                                | 125 |

| hann_gen.py                                                       | 126 |

#### I. Overview / Motivation:

For our final project, we planned to make a musical system with multiple modes.

In our baseline goal, we aimed to have a keyboard mode, in which a user could play many octaves' worth of notes using switches on the Nexys4, with audio coming from the Nexys4's audio output port. We also aimed to have a simple game mode, similar to Guitar Hero, in which a user could select a song, and then LEDs on the Nexys4 would light up, corresponding to notes in a song that a user would try to match using the switches.

In our expected goal, we wanted to replace the switches on the Nexys4 and audio generation from the Nexys4 with a MIDI keyboard. This required proper interfacing with the MIDI keyboard. In addition, we wanted to provide a display system on a lab monitor that would allow a user to navigate a menu to select between different modes and different songs. Furthermore, we wanted to include a falling notes display, like in Guitar Hero. Lastly, we wanted to allow for menu navigation either with buttons on the Nexys4 or with whistling a high vs. low note into a microphone.

In our stretch goal, we wanted to allow for a singing input mode, where a user would try to sing a song accurately, rather than play it on a keyboard. In addition, we wanted to implement a learning mode, in which a user would be walked through a song in order to learn it before being scored for it. Lastly, we wanted to allow a user to define a song of their choosing for the game mode, rather than being restricted to our preset options.

We ultimately accomplished all of these goals except the singing mode stretch goal.

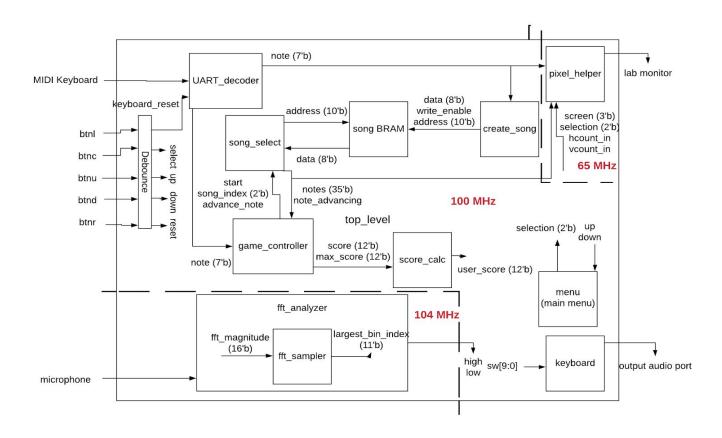

To accomplish this, we wrote many major modules for our system, which we describe in depth below. At a high level, the major modules performed MIDI decoding, output display logic, game logic, interfacing with memory, and FFT calculations for microphone menu navigation. Due to FFT requirements and VGA display requirements, our system used three different clock domains.

The overall system diagram, and then discussion of each piece, can be found below, in Sections II and III.

## II. Total System Diagram

## III. Major Modules

#### A. Keyboard (Jacob)

For our baseline goal, we used the bottom 7 switches on the Nexys4 to choose a note, and then output a PWM signal at the corresponding frequency from the audio output of the Nexys4. The keyboard module works similarly to the starting code we used in Lab 5A. However, I wanted to extend this to work for an entire piano's worth of notes. In order to do so, I first made a look up table to convert from 7-bit note indices to frequencies (in Hz). I then used the formula shown in Lab 5A to convert from a frequency to a phase increment:

$$rac{\left(440rac{ ext{cycles}}{s}

ight)\cdot\left(2 imes10^{32}-1rac{ ext{phase}}{ ext{cycle}}

ight)}{48 imes10^3rac{ ext{samples}}{s}}pprox 39370534rac{ ext{phase}}{ ext{sample}}$$

(This example showed how to calculate this for a 440 Hz desired frequency. It is from <a href="http://web.mit.edu/6.111/volume2/www/f2019/index.html">http://web.mit.edu/6.111/volume2/www/f2019/index.html</a>.)

By making the phase increment variable, according to this formula, it allowed me to at any time switch which note was being played by stepping through the sine wave look up table (from Lab 5A) at different speeds. I used switches 7-9 for volume control.

I used the same code for generating the PWM wave as was used in Lab 5A.

In our final version of the project, we included an option to still use the switches on the Nexys4 instead of the MIDI keyboard. If the top switch (sw[15]) is high, then the input mechanism is the switches. If it is low, then the input mechanism is the MIDI keyboard.

#### **B. MIDI Keyboard Interface (Jacob)**

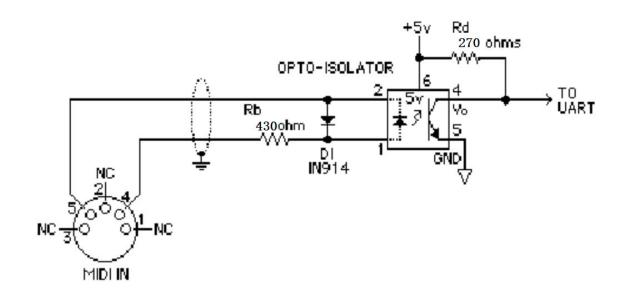

We wanted to allow for user input via a MIDI keyboard. The keyboard we used has a MIDI output port, but the Nexys4 does not have a MIDI input port. Therefore, in order to connect them properly, I needed to build the following circuit to replicate the front-end of a MIDI input port:

diagram from <a href="https://learn.sparkfun.com/tutorials/midi-tutorial/all">https://learn.sparkfun.com/tutorials/midi-tutorial/all</a>

This circuit uses an opto-isolater, meaning the keyboard and the Nexys4 are not electrically connected. This made voltage regulation simple, even though the keyboard outputs 5V and the Nexys4 works at 3.3V. I powered the opto-isolater at 3.3V, meaning the output would be in the range 0V - 3.3V, but because the input side of the opto-isolater is not electrically connected to the power rails, it was okay to put the 5V output from the keyboard into it. The opto-isolater I used was the CPC5002.

Once this circuit was in place, the output from it was essentially a UART transmit line. I could then connect this to an input pin on the Nexys4, and then sample it and interpret it properly.

Before I did this, however, I needed to establish what messages the keyboard would output. While it was similar to standard MIDI messages, the keyboard we used slightly modified some of the MIDI protocols. The only information we cared about was which note was being pressed at any given time.

By scoping the output from the keyboard, I learned that whenever a note is pressed, the keyboard sends two bytes: first, a byte indicating a note index, second, the byte 8'h40. Similarly, whenever a note is released, the keyboard sends two bytes: first, a byte indicating a note index, second, the byte 8'h00. By contrast, the standard MIDI protocol sends the status (on/off) byte first, then the note byte, as well as other information. In addition, the actual on/off bytes are different in the standard MIDI protocol.

Now that I understood the messages that would be sent, I wrote three modules to convert the UART transmit line signal into the information we needed.

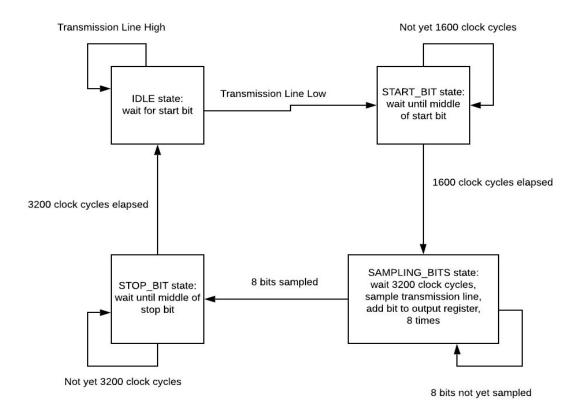

First, I wrote the UART\_decoder module, which samples the transmit line and determines the bytes sent by the MIDI keyboard. This module is a 4-state finite state machine with the following state diagram:

The MIDI protocol sends 31,250 bits per second. It sends a byte as a 10-bit packet, where the first bit is a low start bit, then it sends the 8 bits for the byte (least significant bit first), then it sends a high stop bit.

Running the UART\_decoder module with a 100 MHz clock, there are 3,200 clock cycles per bit. Since the UART transmission line sits high when idle, my FSM has an IDLE state, in which it samples the input transmission line once every 200 clock cycles, trying to catch the falling edge, indicating a start bit. Once it sees the line go low, it switches to the START\_BIT state, in which it waits 1,600 clock cycles, so that it is then near the middle of that start bit. It then switches to the SAMPLING\_BITS state, in which it repeatedly waits 3,200 clock cycles and samples the transmission line 8 times, thus grabbing the 8 bits for the byte and filling up the output register. Then, after doing this 8 times, it switches to the STOP\_BIT state, in which it waits another 3,200 clock cycles to get to the middle of the high stop bit, at which point it switches back to the IDLE state, waiting for the next low start bit.

The UART\_decoder module instantiates the MIDI\_decoder module, and passes in the output bytes that it got from the transmission line as input to the MIDI\_decoder.

Essentially, the MIDI\_decoder's job is to take the bytes from the UART\_decoder module and output an 88-bit register, with a 1 at every index corresponding to a note currently being played, and a 0 everywhere else. In order to do so, it checks whether each incoming byte is a status byte (either the note on or note off byte). If it is not, then it stores the note index contained in that byte in a register called last\_note. If it is a status byte, then it checks the last\_note register to see what note that status of on or off corresponds to, and updates the 88-bit register accordingly.

The UART\_decoder module also instantiates the key\_press module, which takes the 88-bit output from the MIDI\_decoder and outputs a single 7-bit index corresponding to the note currently being played. It works by first adding up all 88 bits in the input register. If this sum is 0, it means no note is being played, so it outputs 7'h7F, which is our index for a blank. If this sum is greater than 1, it outputs 7'h7E, which is our index for an invalid note (since we only allowed for one note being played at a time). If this sum is 1, then it has a case statement based on the value of the 88-bit register, outputting the appropriate index of the single note being played. This output is then passed up to the UART\_decoder module, which outputs this 7-bit index.

#### C. VGA Display (Jacob)

For the VGA display, I wrote a module called pixel\_helper that output the appropriate pixel for given hount and vocunt values, depending on what mode our system is in.

There are 7 different possible types of screens to display, so pixel\_helper has a 3-bit input register called screen, indicating which type of screen to display.

#### There is:

- 1) Main Menu

- 2) Keyboard mode

- 3) Song Creation mode

- 4) Basic song menu

- 5) Custom song menu

- 6) Learning mode

- 7) Game mode

Because the display is always from among this set (with a few squares or rectangles on top), I made a COE file for each of the special images I required, and then generated ROMs to store these images and their colors in memory.

I needed a keyboard image for keyboard mode, learning mode, and game mode:

(I constructed this image in Paint so that it would have the precise correct number of octaves to match the MIDI keyboard we used.)

I needed an image for the main menu display:

Keyboard Mode Create a Song Learning Mode Game Mode

(This text and text in all other images uses Times New Roman font.)

I needed an image for the basic song menu:

# Mary Had a Little Lamb Tetris Theme Heart and Soul

I needed an image for the custom song menu:

# Mary Had a Little Lamb Tetris Theme Heart and Soul Custom Song

Lastly, I needed an image for instructions for song creation mode:

# Play your song!

I made 5 specialized versions of the blob\_image module from Lab 3, one for each of these images, and instantiated a copy of each in pixel helper.

In addition to these images, I also needed a selector for menu navigation. For this, I instantiated the blob module from Lab 3, making a 35 by 35 red blob. Another input to pixel\_helper is the 2-bit selection register, which tells it where a user currently is within a menu (all of our menus have at most 4 options, so 2 bits is enough to specify the location). I then made a look up table module to convert a position (0, 1, 2, or 3) within a menu into a y-position. By setting the x-location of this blob to 650 and the y-location determined by the output of the lookup table, users can navigate the menus and see the red selector move between options.

Furthermore, pixel\_helper has a 6-bit register user\_note as input, indicating what note is currently being played by the user. I wanted there to be a corresponding display for this during

keyboard, learning, and game modes. I therefore made another instantiation of the blob module, this time a 10 by 60 green blob. The y-position is always 580 (to be just above the image of the keyboard, which I placed at y-location 640 to be at the bottom of the screen). For the x-position, I made a look up table that converted note indices into x-positions, based on the exact location where each note started and ended in the image display. For a blank note or an invalid note (multiple notes played at once), the x-location is set to 11'h7FF, thus not showing up on the screen.

During learning mode, I wanted to display the single note that the user is up to in the song they are learning. I therefore gave pixel\_helper a 6-bit register learning\_note as input, and made yet another instantiation of the blob module, this time a 10 by 160 blue blob. The y position is always 480 (to be just above the image of the keyboard), and the x-position is set by the output of the look up table that converts note indices to x-positions.

Lastly, during game mode, I wanted to make a falling notes display, showing 5 notes at once. I therefore gave pixel\_helper a 35 bit register *notes* as input, which is a shift register. It contains the note index of the note that should currently be played in notes[34:28], the note after that in notes[27:21], then the next note in notes[20:14], then the next note in notes[13:7], and the next note after that in notes[6:0]. I therefore made 5 more instantiations of the blob module, all 10 by 160 blue blobs.

In order to synchronize the falling notes display with the underlying game, I knew that each note should last 0.25 seconds. Therefore, I needed each note blob to drop 160 pixels in 0.25 seconds. Working at a 65 MHz clock, I had each blob increase its y-location by 2 every 203,125 clock cycles.

I also gave pixel\_helper an input called new\_note, which goes high when a new note is shifted into the notes register, and is low otherwise. When this signal is high, the 5 note blobs' y-locations are reset to 864 (which is -160 since the height of the screen is 1024), 0, 160, 320, and 480. Then (on the next clock cycle, to make sure the notes register has already updated properly), the x-locations of these 5 blobs is updated to the 5 locations corresponding to the notes in the shift register. Since the new\_note signal goes high every 0.25 seconds, each note blob falls at the right speed so that when a new note shifts in, the transfer looks seamless.

Lastly, in order to give the user a sense of the speed of the notes, I included horizontal, single-pixel thick black lines at y-locations 0, 160, 320, and 480. This was done by just checking if vcount was one of those values, and if so, outputting 12'h000.

In total, pixel helper has a case statement depending on what screen display it should have.

- 1) In main menu mode, it outputs the logical AND of the pixels from the main menu image, and the selector blob.

- 2) In keyboard mode, it outputs the logical AND of the pixels from the keyboard image, and the user note blob.

- 3) In song creation mode, it outputs the pixels from the song creation image.

- 4) In the basic song menu, it outputs the logical AND of the pixels from the basic song menu image, and the selector blob.

- 5) In the custom song menu, it outputs the logical AND of the pixels from the custom song menu image, and the selector blob.

- 6) In learning mode, it outputs the logical AND of the pixels from the keyboard image, the user note blob, and the learning note blob.

- 7) In game mode, it outputs the pixels from the keyboard image if vocunt is at least 640. Otherwise, it outputs 0 if vocunt is 0, 160, 320, or 480 (for the horizontal lines). Otherwise, it outputs the logical AND of the pixels from the 5 note blobs, as well as the user note blob.

#### **D. Song Creation (Jacob)**

In song creation mode, I needed to sample the user's input from the keyboard every 0.25 seconds, and then send the appropriate signals to store these input notes in our song BRAM.

The create\_song module has an enable input and a 7-bit input value (based on what note the user is playing). It outputs an 8-bit data value to write to the BRAM, a write\_enable signal, and an address to write to in the BRAM.

Because we want to sample the user's playing every 0.25 seconds, we wait 25,000,000 clock cycles in between samplings (due to the 100 MHz clock).

When enable is first asserted, the address value is initialized to 753. This is because address is always incremented by 1 just before writing to the BRAM, meaning the first location written to is 754. This ensures that the first 4 notes of a custom song will all be blanks (giving the user time to get to the correct starting note in game mode), since we initialize the song BRAM to have blanks at addresses 750, 751, 752, and 753.

Then, when enable is high, a counter is incremented every clock cycle. When it has reached 24,999,999, the user input value is written to the next location in the BRAM (so write\_enable is set high for one clock cycle), and the counter goes back to 0. This continues as long as enable is high and there is still room left in the BRAM.

We allow for 242 notes to be input by the user (and at one note every 0.25 seconds, this corresponds to 1 minute and a half second for a custom song). When the user has reached the maximum allowable memory location in the BRAM, create\_song never sets write\_enable high again. Since the BRAM is initialized with an END\_NOTE special value (indicating to the game logic that the song is over) in the final address, create\_song does not need to add this value.

However, if enable stops being high (a user has left song creation mode), then create\_song immediately (on the next clock cycle) writes the END\_NOTE special value to the next address in the BRAM (so that the game logic will know that the song ends there). After this, as long as enable is low, write enable is set low so that the BRAM is not changed.

Due to this setup, if a user again enters song creation mode, they will simply overwrite their previous custom song.

All of the outputs from the create\_song module get passed up to the top\_level module, which instantiates the BRAM. The BRAM is dual port, so the output values from create\_song are the input values for the write port on our song BRAM.

#### E. Game Logic (Rahul)

The game controller is a large finite state machine that tracks every state of the game, as well as the user's score and progress. As input, it takes a pulse indicating whether or not the game is currently active, the note that user is currently playing (represented by a MIDI index), the current game type (learn or play), button inputs (for menu navigation), and a 1-bit indicator of whether a custom song has been created.

The FSM has 6 states, each of which are only used when the game is on. When the game is off, as indicated by a 0 on the game\_on input, the module simply zeros out all the internal state and waits to be turned on once again. When the game is powered on, it enters the idle state, STATE\_IDLE, and latches all of the relevant input values, such as the current game type (play/learn). It then progresses to the song selection state (STATE\_SONG\_SELECT), which enters into a menu (see menu module below) that allows the user to select which song they wish to play or learn. Once this has been chosen, the FSM saves the song selection as state, and feeds a start signal into the song select module (described below). This allows the song select module to begin feeding a shift register of 5 notes to the game controller, which are used for the actual gameplay.

The game controller progresses to one of two states, either the play (STATE\_PLAY) or learn (STATE\_LEARN) mode. In both of these states, the FSM uses almost the same logic. In the play state, It uses a counter to sample the user's input note every tenth of a second, and it compares

this to the expected note from the song selection module to determine whether the user is correctly playing the note. If they are indeed playing the correct note, it increments their score. In either case, it increments a second score counter which represents the maximum possible score for the current song. In playing mode, this is the only logic needed, as the song select module automatically advances the notes every quarter of a second, as described in the song select module section below. However, in the learn state, the module samples the user's note continuously, in order to determine whether or not the user has held the correct note for the correct length of a quarter of a second. Once they have, it asserts an advance\_note signal to signal to the song select module to shift in the next note. In this way, the user is able to correctly progress through the song, and thus learn it. In both states, the module has special logic for when it encounters a sentinel index that represents the end of a song (7'b111\_1100). Once it has encountered this note index, it advances to the next state, SONG\_FINISH, which represents the end of the game.

In STATE\_FINISH state, the game gets ready to reset. It zeros out all the values except for the user's score and the maximum possible score of the song. These two values are set as outputs back up to the top level module, where they are used to calculate and display the user's final percentage score. It then moves back to STATE\_IDLE, to wait for the next game to be played. This extra state mainly serves to signal to the top level that the game has finished, and to transfer control of the VGA display back to this upper level. When the module is in STATE\_FINISH, it sends this to the top level through an output register that allows the upper level to revert its internal state back to its top level menu, and thus restart the system.

The sixth state is STATE\_MODE\_SELECT, which is not currently used. It is intended for our third stretch goal, allowing the user to input notes by singing, rather than playing the keyboard. This mode takes the user to an extra menu that allows for the option to choose whether they will play keyboard or sing into a mic, but we did not complete implementing this stretch goal.

#### F. Song Select Module (Rahul)

The Song Select Module represents the interface between the Game Controller and the BRAM that holds the songs. It takes as input the desired song index as well as a start pulse that indicates to it when it should begin outputting that song, and whether it is operating in play or learn mode. In turn, it outputs a shift register that represents the next 5 notes in the song.

In addition to these control signals, the song select module also outputs the current address it wishes to read from and takes as input the note from that address. We could not directly put the BRAM into this module, because the song creation module (discussed above) also needs to interact with it. Thus, we had to place the BRAM itself at a higher level, and route the signals up to it. However, for the intents of the abstraction presented to the Game Controller (a module that

takes the song index and a start signal and outputs the top 5 notes), this does not make a difference

When the start signal is asserted it latches the current song index and the game type (play or learn). It then resets the current address to the beginning of the desired song. We placed every song in a fixed 250 byte segment of the BRAM, so these addresses were easy to calculate. It then enters a "startup" state, which is used to quickly load the first five notes of the song in 10 clock cycles (because the BRAM has a 2 cycle read latency). After performing this load, it moves to the regular state, which has two different behaviors, depending on whether it is operating in play or learn mode. In play mode, the module simply uses a counter to advance the address being read from the BRAM every quarter of a second, as each note represents a quarter of a second of song length. In learn mode, the module uses an input advance pulse to determine when to advance to the next note. In both modes, when the module reads a note index that represents the end of the song, it stops reading from the BRAM and begins shifting in rests. This is important, as the display may otherwise show random values falling on the screen after the end of the song, depending on whatever values may come after the song in memory.

One final important output of this module is a pulse that goes high every time a new note is shifted into the notes shift register. This is used by the pixel\_helper module to correctly update the display with the notes shifting in. The fact that the signal is used by the VGA logic is important, because VGA is clocked at 65MHz, which is slower than the game's 100MHz clock. Thus, although this signal is really a pulse, it goes high for four clock cycles every time it should represent a new song. This duplication is required so that the slower clock domain is able to still correctly sample the pulse.

In order to quickly and correctly generate the coe files for the song BRAM, I wrote a Python script that followed our internal format. I have included this at the end of the writeup in Appendix B.

#### G. Learning Mode (Rahul)

The learning mode of the game is part of the game controller and song select modules, as described above. It requires the addition of extra state, which is described in more detail here. The learning mode is similar to the playing mode, in that it reads notes from the BRAM and sends them out to the VGA display modules. However, the mechanism for advancing notes is different, as it must now wait for user input and advance depending on whether or not the user is correctly playing notes, rather than keeping an internal timer to continuously advance notes. To this end, the game controller was augmented with a special state that works similarly to a debouncer; it tracks the most recently played note, and for how long it has been played. When the most recently played note is the current note of the song, and its length is equal to the correct

note length (a quarter of a second), it advances the song forward to the next note. In order to allow for this external control on the note advancement, an advance input signal had to be added to the Song Select module, which in turn had to maintain an internal state of whether it was operating in play mode (and thus should advance notes on its own), or whether it was operating in learn mode (and should only advance notes when told to).

This extra functionality was possible to add in because of the clean abstractions chosen for other aspects of the game. By splitting the game control logic out into a separate FSM, adding the main learning mode logic was clean, as it represents an extra state in the game controller FSM. Furthermore, the separation of the song select module to act as an interface to the BRAM made it relatively clean to account for the fact that learning mode only advances notes when the user plays the correct note. The game controller took care of tracking all of the user input, and then only had to present a pulse on note advancement to the song select module, which only had to use this signal to determine when to advance notes. The modularization allows for clean coding and separation of functionality.

#### H. Microphone Input (Rahul)

The microphone input component of this project allows the user to navigate menus by whistling high or low notes. In order to accomplish the microphone input, I wrote two main modules, the fft\_analyzer and fft\_sampler modules. I also used some ancillary modules, such as the timer described below.

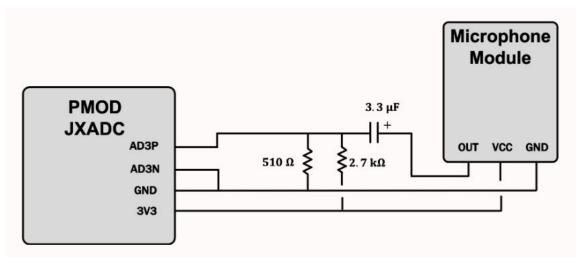

To perform the microphone input, I first had to actually set up an external microphone that provided an analog audio signal to the Nexys4. I used a small microphone breadboard module from lab and set up a quick circuit that used a capacitor to couple the signal and overlay it on a 0.5V DC offset, set up by a voltage divider between power (3.3V from the Nexys4) and ground. The microphone module outputs a 1V peak to peak signal, and the Nexys4 analog input reads on the range 0 to 1V, so this circuit allowed for maximum sensitivity to the analog waveform. The circuit is the same as is used in Lab 5A, and I have included an image from the lab below.

Microphone Input Circuit, image from Lab 5A (http://web.mit.edu/6.111/volume2/www/f2019/handouts/labs/lab5\_19a/index.html)

The fft\_analyzer runs on a 104MHz clock, because the Nexys4's internal ADC module uses 26 clock cycles to take samples. Thus, by clocking at a multiple of 26, I was able to configure the ADC IP block to exactly output a 1MHz sampled digital signal from the microphone input. The module consists of two major pieces.

First, it contains an entire pipelined FFT implementation, inspired heavily by the FFT Demo provided in class. This implementation performs a 4096 sample FFT of the current input audio at a rate of 60Hz, providing more than enough resolution to correctly identify the user's whistling and respond quickly. Second, it contains an FSM that performs all of the functions necessary to analyze the FFTs taken and determine whether a low or a high note is being whistled.

#### H.i. FFT Calculation

The first stage of the FFT calculation is an ADC IP block, which takes as input the analog signal from the vauxp3 and vauxn3 ports from the Nexys4 and outputs a 12-bit 1MHz sampling of the analog audio.

The second state of the pipeline is an oversampling step, which oversamples the digital audio sample by 16. In particular, it performs a sliding window summation of every 16 samples, and divides the resulting waveform by 4, so that it adds 2 bits to the waveform, resulting in 14-bit samples. This oversample allows the waveform to be downsampled to 62.5KHz, which is much better for the FFT we are interested in taking. We are differentiating whistling by a human, which ranges in the low 1000s and high 100s of Hz, so the FFT needs to be granular enough to clearly distinguish these frequencies. Thus, using a 1MHz sampling rate is useless, as it represents far too many high frequencies that are not relevant. By downsampling to 62.5 KHz,

we only consider frequencies up to 31.25 KHz, which is a tighter range around our relevant frequencies. This smaller range also allows the FFT to fit within a relatively small window, so that it does not use up too many resources on the chip (especially when they are not needed). The average oversampling is used rather than a simple sample in order to introduce less noise through the sampling process.

The next stage in the FFT pipeline is a BRAM that stores a frame of the most recent 4096 data samples from the oversampling stage. This allows the stages further down the line to read the input data when it is convenient, rather than having to read and buffer values when they are inputted. This BRAM simply has a looping counter that keeps writing in data from the oversampling stage. Because it is writing in data from the oversampling stage, it has to correctly synchronize with the oversampling stage and only write in a sample every 16 cycles, when a new one is ready.

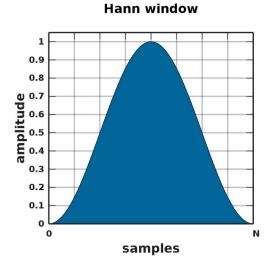

The fourth stage in the FFT processing pipeline is a module to move data from the BRAM to the FFT IP block. Because the FFT is calculated only once every 60th of a second, it reads from the data BRAM much less frequently than data is written to it, so this module acts as an interface between the two. This module is triggered on the 60Hz pulse to send the current 4096-sample data frame to the FFT. It also uses the frame tready signal from the FFT module, which indicates that the FFT IP is ready to receive the next data value, to advance the address it is currently reading from the BRAM. This module is a simple counter FSM, and simply maintains its current position in the BRAM and advances this position every time the FFT IP indicates over frame tready that the next sample should be sent. One extra piece that I added is a Hann windowing filter over this BRAM data. I created a 4096 element lookup table that holds Hann filter coefficients (rounded to 24 bits). I then read the correct element from the LUT and multiply it against the data value read from the BRAM to correctly filter the outputted data. Because the FFT takes in only a single finite frame of data, it implicitly treats it as though it is repeated infinitely. Thus, if the edges do not smoothly match up, the resulting FFT is very noisy. I used the Hann windowing filter to create a clean and more easily analyzable output FFT (see the image below for the filter). I have also included the Python script I used to generate this lookup table in Appendix B.

Hann Window of length N, image from Wikipedia (https://en.wikipedia.org/wiki/Hann function)

The fifth stage in the FFT pipeline is the actual FFT IP block. This is a specially designed FFT logical block that performs a fully-pipelined 4096 element FFT. I used the IP module from the FFT Demo provided in class without modification, as a length of 4096 provided enough granularity in the resulting FFT to distinguish the frequency range I was interested in.

The sixth stage of the FFT is another BRAM that holds the results of the FFT that is calculated 60 times a second. Because the FFT is calculated so infrequently, it is desirable to cache and hold the results in a BRAM, from which they can be read when needed, rather than having to immediately begin processing the FFT samples as they arrive. Thus, the final stage of the FFT is a BRAM that simply takes as input the output of the FFT IP and writes to the BRAM in sequential order. The BRAM actually only holds the magnitude of the first 1024 of the 4096 total samples, because this is block represents the range of frequencies that the whistle could range in, and is enough for the following analysis.

#### H.ii. FFT Analysis

The FFT analysis runs 60 times a second, processing each FFT after it has completely been written to the output BRAM. As soon as this happens, the first stage of the analysis is the fft\_sampler module. This module performs a sweep over a subset of the 1024-sample FFT and determines the index of the largest bucket. It only considers samples between indices 8 and 300, both of which are parameters that I tuned so that my system was responsive only to the frequency range of whistling. Within this range, it performs a sweeping window-sum of the samples, and saves the index of the window that has the largest magnitude. This window sum, rather than simply choosing the largest sample, helps to filter out any extraneous noise that

randomly shows up, because I noticed after spending time analyzing FFT outputs that the true frequency content generally has ancillary content in neighboring frequency buckets, whereas noise is more isolated to a single frequency range. The sample performs this scan using an FSM that is generally in an idle state, but then moves to a sweep state whenever a start input (based on the completion of a new FFT in the FFT calculation stage above) pulse is asserted. In the sweep state, it keeps an accumulating sum and a shift register of values currently in the window, calculates the sum at each index, and saves the index with the largest sum, as well as the actual sum. If the actual sum is larger than a threshold value, which I tuned to make sure that the system was only responsive to intended input and not environmental noise, it returns the index; otherwise, it returns a value to indicate that there is no current input.

The three tunable parameters of the fft\_sampler module are very important for tuning the system to work for a given input frequency range. Because this project dealt with whistling, I tuned the set of considered FFT indices to the lower end of the spectrum, 8 to 300. Because the underlying audio samples are at 62.5KHz and this is a 4096 sample FFT, that represents frequencies from 122Hz to 4.5KHz, which is a reasonable range for human whistling. The third parameter, the threshold magnitude for the windowed sum, is important to rule out any environmental noise. The environment always has a reasonable frequency component, and may randomly be large enough to dominate the input, especially when no noise is currently intended to be inputted to the system. By increasing the minimum threshold for how large an FFT window must be before it is considered actual input into the system, I could make it reject more noise and be more sensitive only to close inputs.

After this, there is a final FSM that keeps track of whether the user is inputting a low or a high whistle into the microphone. It cannot simply check at each cycle whether the user is inputting low or high and return this value, because the microphone was noisy enough that this was not a consistently high value as the user whistled. Thus, even with rising edge detection, the inputted note would look more like several inputted notes and the user would shoot up or down the menus without having any fine grained control. Thus, I used a more sophisticated FSM to track user input.

The high/low detection works as follows. When the system is in the tracking state, if it detects either a high or a low note for long enough (both the cutoff frequency between high/low and the minimum required length are tunable parameters), it outputs the correct value as a detected note, and enters the waiting state. In the waiting state, the system starts a 0.5 second timer, and holds the previously detected note on the output until this timer expires. By using a timer, the system makes sure that it represents the users intended input with a clean output signal for a sufficiently long time and does not provide the user such fine grained control (e.g. 104MHz control) that they would quickly shoot up or down the menu even with a short whistle. To implement this behavior,

the FSM has two states: STATE\_TRACKING and STATE\_WAITING. It uses a 2-bit state variable to represent the current state of the detected audio, either high, low, or none. This state variable is updated as described. Further, it uses a counter variable to count how long the current note has been held, in order to determine when it has been held long enough to be considered a valid input.

There are three important tunable parameters in this case. The cutoff frequency between high and low notes is important to make sure that the system is usable. If the cutoff is too low or too high, the user will not be able to input both high and low notes and will not be able to navigate the menus with sound. Thus this threshold must be tuned so that it is easy to whistle both below and above it. The minimum length of a note to be considered a valid input is important to screen out noise. Many notes in the valid range may be generated for a cycle or two due to environmental noise. By making this parameter large enough, it is possible to screen out such noise. Making it too large, however, makes the system feel unresponsive, as the user will have to hold the note for a long time. Thus, there is a tradeoff between noise sensitivity and usability with this parameter. Finally, the third parameter is the length of the timer, which again provides a tradeoff between usability and sensitivity. If the timer is too short, the system will be too sensitive, and will not be able to accurately navigate menus. However, if the timer is too short, the system will be too slow to respond, and will provide a bad experience. Thus, it is important to choose good values for these parameters.

The overall output of the entire fft\_analysis module are two 1-bit signals, hi and lo, indicating whether a high or low note (respectively) are being inputted into the system. This interface provides a very clean integration with the top level, as it looks exactly equivalent to the btnu and btnd buttons on the Nexys4, which provide an alternative means of navigating menus.

#### I. Top Level

The top level module represents an integration of all of the major components described above. It essentially just consists of instantiations of all of the major modules, such as the UART decoder, VGA display, Game Controller, and FFT analyzer. In addition, it also maintains a small FSM to allow for the top level module to choose between the four main modes of the system: keyboard mode, song creation mode, learning mode, and playing mode. The FSM has two states, to represent whether it is currently in the top level menu, or whether it is operating in one of the chosen modes. There are two other main pieces of logic in the top level module. The first is a 1-bit signal that indicates whether or not a custom song has been created. It starts as 0, and goes to 1 once a new song is created. This signal is routed to the game\_controller module for its user. In addition, it also contains logic to switch the input mode of the system. Our baseline goal was to implement the system with switches as input, so we maintained this input option in the final version of the project. It can be activated by flipping on switch 15, at which point the system will

operate through the switches on the Nexys4, rather than the keyboard. This was purely for demonstration of the baseline goals, and it is expected that most users will prefer to play the game on the keyboard.

The other main purpose of the top level module is to correctly debounce and synchronize all of the signals. All of the user inputted signals must be debounced (buttons) and synchronized (switches) to the main 100MHz clock domain. Furthermore, the system uses 3 clock domains, 65MHz, 100MHz, and 104MHz, so any signals that are passed between these different boundaries must be synchronized to their new clocks. All of this synchronization logic is provided in the top level.

Finally, because the song BRAM is written to by the song creation mode and read from by the Song Select module, we place the actual BRAM itself in the top level because it is the lowest common ancestor of these two modules in the hierarchy of the project. We route all of the relevant signals (read and write addresses, write data, write enable) up to the top level to interface with the song BRAM.

#### J. Miscellaneous Modules (Menu, Timer, Score Calculation) (Rahul)

Many of the major modules used several helper modules that performed common subtasks in the larger components of the project. We briefly list a few of these modules here to describe some of the required functionality.

The Menu Module serves as an interface for all of the menus in the system. It provides an FSM that tracks the user's current menu choice based on an input up and down signal. It outputs this menu choice. It has a programmable upper bound, so that any number of menu items can be represented and dynamically changed. This module is used for all the menus in the system.

The Timer module provides a countdown timer for the FFT analysis. This countdown timer starts whenever the start input pulse is asserted, and counts down for a variable length, depending on the length inputted to it. It latches this length and counts down from it until it expires, and then is ready to start again with a new length. It perform this countdown with an FSM that has two states: counting down and idle.

The Score Calculation module provides an approximate decimal division functionality. It takes as input the user's score and the maximum possible score they could achieve, and returns their percentage score, rounded to the nearest integer. It accomplishes this by using two lookup tables for powers of 10 and 16, and by starting from the largest possible power of 10 (10^2) and subtracting off ever decreasing multiples of until the score hits zero. In other words, simulates division through repeated subtraction. It begins this computation every time a start signal is

asserted, at which point it latches the current score and maximum score, and performs the percentage calculation.

### IV. Trickiest Pieces of the Project

#### Jacob

One of the hardest pieces was getting the external circuit connecting the MIDI keyboard to the Nexys4 working. Originally, I used resistor values that were too low, which caused me to inadvertently blow out the LED inside the opto-isolator I was using. I spent hours trying to figure out why the circuit was not working. Gim helped me debug this and helped me choose resistor values in order to prevent the internal LED from blowing out.

Another difficulty I found was that occasionally, if a key was hit or released very quickly on the MIDI keyboard, no message would be sent. Therefore, the UART\_decoder module would not register the change in what note(s) were being played. This initially led to some issues, because if the UART\_decoder module thought some note was continually being played, then any other note played would then register as an invalid note, since then multiple notes were on. In order to fix this issue, I allowed for a reset of just the 88-bit register that keeps track of which notes are currently being played, using button btnl on the Nexys4. That way, if this ever happened, I could press btnl to indicate that no note is being pressed at the moment.

Perhaps the trickiest bug I had was that when we first integrated the game logic with the falling notes display for game mode, it worked most of the time, but every so often, the display would glitch, showing notes jumping all over the screen. It was interesting that it was always the case that a song glitched throughout, from beginning to end, or not at all. This was very difficult to debug because despite my best efforts, I could not find a pattern regarding when it would glitch and when it would not. I tried updating the x-locations of the 5 different notes on the display at different times from one another in order to see if perhaps the issue was with only some of them, but I could not find anything from that.

Then, I realized that the issue was occurring because of the slower clock speed of pixel\_helper than the game logic. The game logic runs at 100 MHz, while pixel\_helper runs at 65 MHz. The display logic for the falling notes, as explained above, relies crucially on the new\_note signal, which is an input to pixel\_helper that goes high when a new note has just been shifted into the shift register. Even though we were synchronizing this signal for the 65 MHz clock, I realized that because the game logic clock is faster, a single clock cycle of the 100 MHz clock might be too fast for the 65 MHz clock to see, depending on the shift between the clocks at the start of gameplay. This was the root of the bug, and also explains why there seemed to be no pattern to

when there was or was not glitching; glitching was determined by the shift between the clocks at the moment the game was started.

In order to remedy the situation, since the 100 MHz clock is less than twice as fast as the 65 MHz clock, we made the new\_note signal go high for 4 clock cycles. As soon as we did this, the display worked smoothly.

#### Rahul

One of the trickiest pieces of this project for me was the note representations of the songs, and how to correctly detect and deal with songs ending. Early on, I played around with the idea of storing the length of the song in the BRAM, before the notes of the song. This was a pretty simple idea, and it allowed for the songs to be variably sized. However, the implementation would be fairly complicated, as the lengths of songs would have to be read into register and held as state throughout the duration of the song, and passed on to interested modules, like the game controller and scoring modules. Further, I knew that we would try to complete the song creation mode, and this would complicate that logic as it would have to track and write in song lengths. Thus, I came up with a different way to represent the ends of songs. In particular, I assigned a special sentinel value that was unused by the note indices to represent the ending of a song. This representation allows for the songs to be played and the end states to be calculated on the fly, without needing any prior knowledge about the songs. This made it much simpler to track song state and to transition between songs when they ended. It also made it much easier later on to keep score, as all I had to do was add an extra counter that always incremented score, rather than only when the user gets the correct note, and I had the correct maximum score value.

The FFT analysis segment of this project also had many tricky parts. First off, it was difficult to get the FFT itself correctly functioning

After I had a clean FFT output that could correctly detect the input note, it was even more challenging to devise a system that would detect the user input in a responsive and smooth manner. The first issue to tackle was detecting the dominant note being inputted into the microphone at any given time. The microphone picks up a lot of environmental noise, so it was not enough to simply sweep through the frequency range and choose the largest bucket. Because of random noise input, this would sometimes be an invalid bucket index. Instead, after analyzing many FFT frames, I noticed that any valid input note produced relatively large frequency components in the immediately neighboring buckets. Thus, I decided to use an averaging window of size 2 to find the largest bucket, rather than a simple maximum. This choice provided robustness to noise

After fixing this frequency detection issue, there were still two main issues with user high/low differentiation. The first is that the detection is happening at 60Hz (the number of times per second an FFT is taken). Thus, if I naively outputted the detected hi/lo bucket at every sample, the system would be far too fast for a human to operate it, and any attempt to input a note would result in the menu pointer quickly advancing through the entire menu. The second issue is that the FFT itself was still fairly noisy, and so I could not necessarily assume that a user holding a steady input note would result in a steady high/low detection (if this was the case, I could have used an edge detector to fix the first issue). Thus, in order to remedy these issues, I used a timeout based technique. First, I ensured that the user's note was held for a sufficient number of cycles. At a fraction of a second, this value was short enough to expect to happen without intervening noise, and yet long enough to not accidentally misconstrue environmental noise as user input. Second, I used a timeout clock to insert a 0.5 second delay in between consecutive user inputs. In this manner, I was able to avoid the issue of updating the detected note too fast and making the system unusable. Tuning these two lengths was crucial to making the system responsive to the user and yet robust to noise.

#### V. Lessons Learned / Advice for Future Projects

#### Jacob

One lesson I learned that I would like to pass on to future project groups was regarding project management and scope. Initially, our goals were far too ambitious for a 2 person group, given the time constraints of the project. Essentially, we initially hoped to have keyboard mode and game mode, but also allow for user input via singing or via the MIDI keyboard. On top that, to help with the singing and playback of the singing, we were planning on doing some form of noise cancellation, in which our system would learn the characteristics of the noise in its environment and strip those from future recordings for noise-attenuated playback.

Because we saw how ambitious these goals were, we decided very early on to dive into the more challenging-seeming aspects, so that in case they were not feasible, we had time to focus our time elsewhere. I went to lab very early on in the project and began playing around with the FFT demo provided, and saw how much noise there seemed to be, spread throughout the frequency spectrum. I therefore recognized that picking out features of the noise in that environment may be very difficult.

I then did some research online to see if people had ever tried to do noise cancellation on an FPGA. Most of what I found had to do with real-time, active noise cancellation using beam-forming, which was not our intended goal. I soon recognized that noise cancellation would have been an entire project on its own, so we ended up removing that from our project, instead supplementing keyboard and game mode with learning and song creation mode.

The advice I would give future groups is to begin exploring some of the more difficult-seeming yet fundamental pieces of your project early on. This will give you time to assess how difficult and time-consuming that aspect of your project will be, which will give you a much better overall sense of how feasible your project is.

One other piece of advice I have for future groups is to integrate earlier than you think you need to. It always seems that integration should be simple, in that if each piece works, they should just work together. Due to different clock domains, as well as generating IP sources for slightly different boards, Rahul and I ended up spending many days just integrating pieces that already worked individually. While it might be best to integrate as you go as opposed to leaving all integration for the end, certainly make sure to integrate more than a few days before the project is due.

Lastly, I strongly recommend trying to get hardware working as early as possible. Hardware can be deceptively difficult to get working and integrated with the Nexys4, as I learned in trying to interface properly with the MIDI keyboard. Even something as simple as realizing I needed to order a cable, which delayed my working on the keyboard interface for a week, could have been detrimental had I not been working on it early in the project. Therefore, just trying to get some of these more unknown pieces operational early on can be a huge help.

#### Rahul

One lesson that I think will be very valuable to future groups is to think carefully about the abstractions and formats they wish to use in their project before beginning to implement anything. When I was working on the song selection and game controller logic, I had to create a good way to represent songs in memory and, in particular, how to deal with variable length songs. A naive idea is to store the lengths of the song in the BRAM, before the song data itself, but this implementation turns out to be much more involved and higher latency than the solution I used, as described in the section above on tricky parts of the project. Thinking about this abstraction before implementing it was very useful, and made it much more feasible for me to implement my stretch goal of learning mode afterwards, as this representation was much more amenable to different modes of song iteration. Similarly, by thinking through the operation of the system, I was able to write an abstract menu wrapper that we used throughout the system for all of the menus.

Another general piece of advice that I have for future groups is to begin early and implement the large components as soon as possible. As the semester progresses, all classes inevitably get much busier, and it is very easy to overestimate the amount of time you have left. I think the best way to counter this issue is to find the most complex component of the project and to implement and

test it first, so that a large piece of the project is complete early on, rather than tackling smaller, easier pieces first. This way, you will be able to make significant progress later on in smaller chunks, rather than leaving a large and complex piece for the end. Along this line of thinking, I implemented the entire first version of the game controller in the first week of working on the project, and was able to iteratively refine this implementation in smaller chunks throughout the following weeks. Similar to this advice, I would also generally suggest that future teams think through their projects and determine what the most difficult parts will be, so that they are able to appropriately order their work on it. I think that breaking down the work to be done into a clear and directly actionable set of objectives ordered by projected difficulty makes the project much more tractable.

A final piece of advice I have for future teams is to ensure that they begin working with any new concepts as early as possible. Before this project, I had never worked with the FFT module, and I had only very limited experience with audio input to the Nexys4 in general. Thus, understanding and getting these aspects of the system to work was disproportionately difficult. I did not originally anticipate this, and it took many late nights in the lab to figure out how to get the FFT to produce valid results that I could use to begin differentiating note inputs. When calibrating for how long various parts of the projects will take, I would suggest to teams to keep in mind that new concepts take much longer to learn than expected, and that starting on these parts early is a good idea.

## **Appendix A: Verilog Code**

See our GitHub repo (<a href="https://github.com/rahulyesantharao/FPGA">https://github.com/rahulyesantharao/FPGA</a>) to view this code in a more convenient code viewer. We have also included all of the project source code below, for completeness.

#### top level.sv

```

// Top level module: Integrates all of the components.

module top_level(

input clk_100mhz,

input [15:0] sw,

input btnc, btnu, btnd, btnr, btnl,

input vauxp3,

input vauxn3,

input vn_in,

input vp_in,

input [7:0] jb,

output logic [15:0] led,

output logic ca, cb, cc, cd, ce, cf, cg, dp,

output logic [7:0] an,

output logic aud_pwm,

output logic aud_sd,

output[3:0] vga_r,

output[3:0] vga_b,

output[3:0] vga_g,

output vga_hs,

output vga_vs

);

// setup clocks

wire clk_104mhz, clk_65mhz;

clk_wiz_0 clockgen(

.clk_in1(clk_100mhz),

.clk_out1(clk_104mhz),

.clk_out2(clk_65mhz));

// debounce reset

```

```

logic reset;

debounce btnr_debounce(.clk_in(clk_100mhz), .noisy_in(btnr), .clean_out(reset));

// synchronize switches

logic [15:0] sync_sw;

synchronize sw0_sync(.clk_in(clk_100mhz), .unsync_in(sw[0]),

.sync_out(sync_sw[0]));

synchronize sw1_sync(.clk_in(clk_100mhz), .unsync_in(sw[1]),

.sync out(sync sw[1]));

synchronize sw2_sync(.clk_in(clk_100mhz), .unsync_in(sw[2]),

.sync_out(sync_sw[2]));

synchronize sw3_sync(.clk_in(clk_100mhz), .unsync_in(sw[3]),

.sync_out(sync_sw[3]));

synchronize sw4_sync(.clk_in(clk_100mhz), .unsync_in(sw[4]),

.sync_out(sync_sw[4]));

synchronize sw5_sync(.clk_in(clk_100mhz), .unsync_in(sw[5]),

.sync_out(sync_sw[5]));

synchronize sw6_sync(.clk_in(clk_100mhz), .unsync_in(sw[6]),

.sync_out(sync_sw[6]));

synchronize sw7_sync(.clk_in(clk_100mhz), .unsync_in(sw[7]),

.sync_out(sync_sw[7]));

synchronize sw8 sync(.clk in(clk 100mhz), .unsync in(sw[8]),

.sync_out(sync_sw[8]));

synchronize sw9_sync(.clk_in(clk_100mhz), .unsync_in(sw[9]),

.sync_out(sync_sw[9]));

synchronize sw15_sync(.clk_in(clk_100mhz), .unsync_in(sw[15]),

.sync_out(sync_sw[15]));

// debounce buttons

logic db_btnc, db_btnu, db_btnd, db_btnl;

debounce btnc_debounce(.rst_in(reset), .clk_in(clk_100mhz), .noisy_in(btnc),

.clean out(db btnc));

debounce btnu_debounce(.rst_in(reset), .clk_in(clk_100mhz), .noisy_in(btnu),

.clean out(db btnu));

debounce btnd_debounce(.rst_in(reset), .clk_in(clk_100mhz), .noisy_in(btnd),

.clean_out(db_btnd));

debounce btnl_debounce(.rst_in(reset), .clk_in(clk_100mhz), .noisy_in(btnl),

.clean out(db btnl));

```

```

// Instantiate the keyboard module, to allow for system input through the Nexys4

switches.

keyboard my_keyboard(.clk_100mhz(clk_100mhz), .sw(sync_sw[9:0]), .vauxp3(vauxp3),

.vauxn3(vauxn3), .vn_in(vn_in), .vp_in(vp_in), .reset(reset),

.enable(sync_sw[15]),

.aud_pwm(aud_pwm), .aud_sd(aud_sd));

// 7-segment display

wire [31:0] seg_data;

wire [6:0] segments;

assign {cg, cf, ce, cd, cb, cc, ca} = segments[6:0];

display_8hex seven_seg_display(.clk_in(clk_100mhz), .data_in(seg_data),

.seg_out(segments),

.strobe_out(an));

assign dp = 1'b1;

// game controller

localparam VGA_IDLE = 3'd0;

localparam VGA_MODE_SELECT = 3'd0;

localparam VGA_SONG_SELECT = 3'd1;

localparam VGA_GAME_PLAY = 3'd2;

localparam VGA_GAME_FINISH = 3'd3;

// edge detectors of up/down buttons

logic old_db_btnd;

logic rising_btnd;

logic old_db_btnu;

logic rising_btnu;

logic old_db_btnc;

logic rising_btnc;

assign rising_btnd = db_btnd & !old_db_btnd;

assign rising_btnu = db_btnu & !old_db_btnu;

assign rising_btnc = db_btnc & !old_db_btnc;

always_ff @(posedge clk_100mhz)begin

```

```

if (reset) begin

old_db_btnd <= 1'b0;</pre>

old_db_btnu <= 1'b0;

old_db_btnc <= 1'b0;</pre>

end else begin

old_db_btnd <= db_btnd;</pre>

old_db_btnu <= db_btnu;</pre>

old_db_btnc <= db_btnc;</pre>

end

end

// forward declaration of FFT signals and game state

logic rising_lo;

logic rising_hi;

logic [3:0] game_state;

// top level menu

localparam TYPE_KEYBOARD = 2'd0;

localparam TYPE_4 = 2'd1;

localparam TYPE_LEARN = 2'd2;

localparam TYPE_PLAY = 2'd3;

logic [1:0] current_type_choice;

menu #(.BOTTOM_CHOICE(TYPE_KEYBOARD))

mode_menu(.clk_in(clk_100mhz), .rst_in(reset), .btn_up(rising_btnu |

rising_hi), .btn_down(rising_btnd | rising_lo), .choice(current_type_choice),

.top_choice(TYPE_PLAY));

// PARAMETERS

// the state of the game when it is completed

localparam GAME_STATE_FINISH = 4'd5;

// state parameter values

localparam STATE_MENU = 1'd0;

localparam STATE_TYPE = 1'd1; // absorbing, for now

// STATE

```

```

logic [1:0] current type; // the current mode of the system (top level or game

controller)

logic state; // the state the system is in (main menu or subchoice)

always_ff @(posedge clk_100mhz) begin

if(reset) begin

state <= STATE_MENU;</pre>

current_type <= TYPE_PLAY;</pre>

end else begin

case(state)

STATE_MENU: begin

state <= (rising_btnc) ? STATE_TYPE : STATE_MENU; // when btnc is</pre>

pressed, transition

current_type <= current_type_choice; // just keep tracking</pre>

end

STATE_TYPE: begin

// only go back to the top level when the game finishes

state <= (game_state == GAME_STATE_FINISH) ? STATE_MENU :</pre>

STATE_TYPE;

current_type <= current_type;</pre>

end

endcase

end

end

// Determine whether a custom song has been created.

logic enable; // whether or not the system is currently in song creation

assign enable = (state == STATE_TYPE && current_type == TYPE_4);

logic song_created = 1'b0; // whether or not a song has been created

always_ff @(posedge clk_100mhz) song_created <= enable | song_created;</pre>

// game controller signals

logic [2:0] game_vga_mode;

logic [1:0] game_menu_pos;

logic [34:0] game_current_notes;

logic [11:0] game_current_score;

logic [11:0] game_current_max_score;

```

```

logic [1:0] mode choice;

logic [1:0] song_choice;

logic new_note_shifting_in;

logic is_game_on; // calculated based on states from the top level FSM

assign is_game_on = (state == STATE_TYPE &&

(current_type == TYPE_PLAY || current_type == TYPE_LEARN)) ? 1'b1 : 1'b0;

// UART controller - retrieves the note played by the user

logic [6:0] user_note_out_keyboard;

UART_decoder my_note(.jb(jb), .clk_100mhz(clk_100mhz), .reset(db_btnl),

.led(user_note_out_keyboard));

// The user's input note. When switch 15 is on, it uses the switches, and

otherwise, it uses the keyboard.

logic [6:0] user_note_out;

assign user_note_out = sync_sw[15] ? sync_sw[6:0] : user_note_out_keyboard;

// The song creation module

logic ram_wea;

logic [9:0] ram_address;

logic [7:0] ram_write_data;

create_song my_song_creator (.clk_100mhz(clk_100mhz), .enable(enable),

.note_in(user_note_out), .value(ram_write_data), .write_enable(ram_wea),

.address_out(ram_address));

// The song BRAM, which interfaces with both create_song and song_select

(indirectly)

logic [7:0] song_read_note;

logic [9:0] song_read_current_addr;

song_rom my_songs(.clka(clk_100mhz), .addra(ram_address), .dina(ram_write_data),

.wea(ram_wea), .clkb(clk_100mhz), .addrb(song_read_current_addr),

.doutb(song_read_note));

// The game controller.

game_controller #(

.VGA_IDLE(VGA_IDLE),

.VGA MODE SELECT(VGA MODE SELECT),

```

```

.VGA SONG SELECT(VGA SONG SELECT),

.VGA_GAME_PLAY(VGA_GAME_PLAY),

.VGA_GAME_FINISH(VGA_GAME_FINISH))

my_game (

.clk_in(clk_100mhz),

.rst_in(reset),

.game_on(is_game_on),

.btnu(rising_hi | rising_btnu),

.btnd(rising_lo | rising_btnd),

.btnc(rising_btnc),

.keyboard_note(user_note_out),

.mic_note(7'b0),

.game_type_in(current_type),

.vga_mode(game_vga_mode),

.menu_select(game_menu_pos),

.current_notes(game_current_notes),

.current_score(game_current_score),

.current_max_score(game_current_max_score),

.game_state_out(game_state),

.mode_choice_out(mode_choice),

.song_choice_out(song_choice),

.shifting_out(new_note_shifting_in),

.song_select_read_note(song_read_note),

.song_select_current_addr(song_read_current_addr),

.custom_song_activated(song_created)

);

// FFT Analyzer

logic fft_hi, fft_lo;

fft_analyzer fft_in(

.clk_104mhz(clk_104mhz),

.vauxp3(vauxp3),

.vauxn3(vauxn3),

.hi(fft_hi),

.lo(fft_lo)

);

```

```

// synchronize fft lo/hi back to main clock

logic fft_sync_hi, fft_sync_lo;

synchronize sync_fft_hi(

.clk_in(clk_100mhz),

.unsync_in(fft_hi),

.sync_out(fft_sync_hi)

);

synchronize sync_fft_lo(

.clk_in(clk_100mhz),

.unsync_in(fft_lo),

.sync_out(fft_sync_lo)

);

// edge detectors of hi/lo buttons

logic old_sync_lo;

logic old_sync_hi;

assign rising_lo = fft_sync_lo & !old_sync_lo;

assign rising_hi = fft_sync_hi & !old_sync_hi;

always_ff @(posedge clk_100mhz)begin

if (reset) begin

old_sync_lo <= 1'b0;</pre>

old_sync_hi <= 1'b0;</pre>

end else begin

old_sync_lo <= fft_sync_lo;</pre>

old_sync_hi <= fft_sync_hi;</pre>

end

end

// VGA mode calculation - combines the game controller VGA mode and top level

state.

// vga states used by pixel_helper

localparam MAIN_MENU = 3'b000;

localparam KEYBOARD_INSTRUCTIONS = 3'b001;

localparam SONG_INSTRUCTIONS = 3'b010;

localparam BASIC SONG MENU = 3'b011;

```

```

localparam GAME MODE = 3'b110;

localparam LEARN MODE = 3'b101;

logic [2:0] full_vga_mode; // the final VGA mode.

assign full_vga_mode = (is_game_on) ?

game_vga_mode : ((state == STATE_MENU) ?

MAIN_MENU : ((current_type == TYPE_KEYBOARD) ?

KEYBOARD_INSTRUCTIONS : SONG_INSTRUCTIONS));

// VGA signals - sync all of the relevant signals above to the 65MHz clock.

logic [6:0] sync65_user_note;

logic [2:0] sync65_full_vga_mode;

logic [1:0] sync65_game_menu_pos;

logic [34:0] sync65_game_current_notes;

logic sync65_new_note_shifting_in;

logic [1:0] sync65_current_type_choice;

synchronize3 sync_full_vga_mode(

.clk_in(clk_65mhz),

.unsync_in(full_vga_mode),

.sync_out(sync65_full_vga_mode)

);

synchronize2 sync_game_menu_pos(

.clk_in(clk_65mhz),

.unsync_in(game_menu_pos),

.sync_out(sync65_game_menu_pos)

);

synchronize35 sync_game_current_notes(

.clk_in(clk_65mhz),

.unsync_in(game_current_notes),

.sync_out(sync65_game_current_notes)

);

synchronize sync_new_note_shifting_in(

.clk_in(clk_65mhz),

.unsync_in(new_note_shifting_in),

.sync_out(sync65_new_note_shifting_in)

);

synchronize2 sync current type choice(

```

```

.clk_in(clk_65mhz),

.unsync_in(current_type_choice),

.sync_out(sync65_current_type_choice)

);

synchronize7 sync_user_note(

.clk_in(clk_65mhz),

.unsync_in(user_note_out),

.sync_out(sync65_user_note)

);

// VGA output

// pixel on current line

wire [10:0] hcount;

wire [9:0] vcount;

// line number

wire hsync, vsync;

wire [11:0] pixel;

reg [11:0] rgb;

wire blank_ignore;

xvga xvga1(.vclock_in(clk_65mhz),.hcount_out(hcount),.vcount_out(vcount),

.hsync_out(hsync),.vsync_out(vsync),.blank_out(blank_ignore));

wire phsync,pvsync,pblank;

//pixel_helper module to get pixel values for VGA display

pixel_helper ph(.clk_65mhz(clk_65mhz), .screen(sync65_full_vga_mode),

.selection((sync65_full_vga_mode == BASIC_SONG_MENU) ? sync65_game_menu_pos :

sync65_current_type_choice),

.notes(game_current_notes), .new_note(sync65_new_note_shifting_in),

.learning_note(sync65_game_current_notes[34:28]), .user_note(sync65_user_note),

.hcount_in(hcount),.vcount_in(vcount), .reset(reset),

.hsync_in(hsync),.vsync_in(vsync),.blank_in(blank_ignore),

.phsync_out(phsync),.pvsync_out(pvsync),.pblank_out(pblank),.pixel_out(pixel));

reg b, hs, vs;

always_ff @(posedge clk_65mhz) begin

hs <= phsync;

vs <= pvsync;

b <= pblank;</pre>

```

```

rgb <= pixel;

end

// the following lines are required for the Nexys4 VGA circuit - do not change

assign vga_r = ~b ? rgb[11:8]: 0;

assign vga_g = \sim b ? rgb[7:4] : 0;

assign vga_b = \sim b ? rgb[3:0] : 0;

assign vga_hs = ~hs;

assign vga_vs = ~vs;

//////

// Performs the percentage calculation of the score and holds this in disp_score.

logic [11:0] disp_score;

score_calc my_score_calc(

.score(game_current_score),

.max_score(game_current_max_score),

.start(game_state == GAME_STATE_FINISH),

.clk(clk_100mhz),

.disp_score(disp_score)

);

// segment display - show the current note on the top two digits, and the final

score on the bottom 3 digits.

assign seg_data[31:24] = {1'b0, game_current_notes[34:28]};

assign seg_data[23:12] = 0;

assign seg_data[11:0] = disp_score;

// leds - shows the user input note on the top 7 leds and the desired note index

on the bottom 7

assign led[15:0] = (game_vga_mode == GAME_MODE || game_vga_mode == LEARN_MODE) ?

{user_note_out, 2'b0, game_current_notes[34:28]} : 16'b0;

endmodule

// Synchronization Modules

// - Modules to synchronize values of varying bitwidths.

```

```

// 1-bit Synchronizer

module synchronize #(parameter NSYNC=3) (

input clk_in,

input unsync_in,

output reg sync_out

);

reg [NSYNC-2:0] sync;

always_ff @(posedge clk_in) begin

{sync_out, sync} <= {sync[NSYNC-2:0], unsync_in};

end

endmodule

// 2-bit Synchronizer

module synchronize2 (

input clk_in,

input [1:0] unsync_in,

output reg [1:0] sync_out

);

reg [5:0] sync;

always_ff @(posedge clk_in) begin

{sync_out[1:0], sync[5:0]} <= {sync[5:0], unsync_in[1:0]};

end

endmodule

// 3-bit Synchronizer

module synchronize3 (

input clk_in,

input [2:0] unsync_in,

output reg [2:0] sync_out

);

reg [8:0] sync;

always_ff @(posedge clk_in) begin

{sync_out[2:0], sync[8:0]} <= {sync[8:0], unsync_in[2:0]};

end

endmodule

// 7-bit Synchronizer

```

```

module synchronize7 (

input clk_in,

input [6:0] unsync_in,

output reg [6:0] sync_out

);

reg [20:0] sync;

always_ff @(posedge clk_in) begin

{sync_out[6:0], sync[20:0]} <= {sync[20:0], unsync_in[6:0]};

end

endmodule

// 35-bit Synchronizer

module synchronize35 (

input clk_in,

input [34:0] unsync_in,

output reg [34:0] sync_out

);

reg [104:0] sync;

always_ff @(posedge clk_in) begin

\{\text{sync\_out}[34:0], \, \text{sync}[104:0]\} \leftarrow \{\text{sync}[104:0], \, \text{unsync\_in}[34:0]\};

end

endmodule

// Debounce Module - debounces an input signal, includes synchronization

module debounce (

input rst_in,

input clk_in,

input noisy_in,

output reg clean_out

);

reg [19:0] count;

reg new_input;

always_ff @(posedge clk_in) begin

if(rst_in) begin

new_input <= noisy_in;</pre>

```

```

clean_out <= noisy_in;</pre>

count <= 20'd0;

end else if(noisy_in != new_input) begin

new_input <= noisy_in;</pre>

count <= 20'd0;

end else if(count == 20'd1_000_000) begin

clean_out <= new_input;</pre>

end else begin

count <= count + 20'd1;</pre>

end

end

endmodule

// display module for 7-segment display

module display 8hex(

input clk in,

// system clock

input [31:0] data_in,  // 8 hex numbers, msb first

output reg [6:0] seg_out, // seven segment display output

output reg [7:0] strobe_out // digit strobe

);

localparam bits = 13;

reg [bits:0] counter = 0; // clear on power up

wire [6:0] segments[15:0]; // 16 7 bit memorys

assign segments[0] = 7'b100_0000; // inverted logic

assign segments[1] = 7'b111_1001; // gfedcba

assign segments[2] = 7'b010_0010;

assign segments[3] = 7'b011_0000;

assign segments[4] = 7'b001_1001;

assign segments[5] = 7'b001_0100;

assign segments[6] = 7'b000_0100;

assign segments[7] = 7'b111_1000;

assign segments[8] = 7'b000_0000;

assign segments[9] = 7'b001_1000;

assign segments[10] = 7'b000_1000;

assign segments[11] = 7'b000_0101;

assign segments[12] = 7'b100_0110;

```

```

assign segments[13] = 7'b010_0001;

assign segments[14] = 7'b000_0110;

assign segments[15] = 7'b000_1110;

always_ff @(posedge clk_in) begin

// Here I am using a counter and select 3 bits which provides

// a reasonable refresh rate starting the left most digit

// and moving left.

counter <= counter + 1;</pre>

case (counter[bits:bits-2])

3'b000: begin // use the MSB 4 bits

seg_out <= segments[data_in[31:28]];</pre>

strobe_out <= 8'b0111_1111;</pre>

end

3'b001: begin

seg_out <= segments[data_in[27:24]];</pre>

strobe_out <= 8'b1011_1111;

end

3'b010: begin

seg_out <= segments[data_in[23:20]];</pre>

strobe_out <= 8'b1101_1111;</pre>

end

3'b011: begin

seg_out <= segments[data_in[19:16]];</pre>

strobe_out <= 8'b1110_1111;

end

3'b100: begin

seg_out <= segments[data_in[15:12]];</pre>

strobe_out <= 8'b1111_0111;

end

3'b101: begin

seg_out <= segments[data_in[11:8]];</pre>

strobe_out <= 8'b1111_1011;

end

3'b110: begin

seg_out <= segments[data_in[7:4]];</pre>

strobe_out <= 8'b1111_1101;</pre>

```

```

end

3'b111: begin

seg_out <= segments[data_in[3:0]];</pre>

strobe_out <= 8'b1111_1110;</pre>

end

endcase

end

endmodule

// Score Calculation Module - Calculates the score as a percentage to the

// nearest integer. Performs this calculation in an iterative fashion,

// subtracting of multiples of decreasing powers of 10.

module score_calc(

input logic[11:0] score, // the current score

input logic[11:0] max_score, // the maximum score possible

input logic start, // a start pulse to begin the calculation

input logic clk, // the input clock

output logic[11:0] disp_score // a 3-digit decimal output (4 bits per digit)

);

// The scaling factor to get to the nearest integer.

localparam ACCURACY = 7'd100;

// state