# FPGA Fruit Ninja

By Nadia Salahuddin & Lydia Sun

# **Table of Contents**

| Overview                                | 3  |

|-----------------------------------------|----|

| Motivation                              | 3  |

| Summary                                 | 3  |

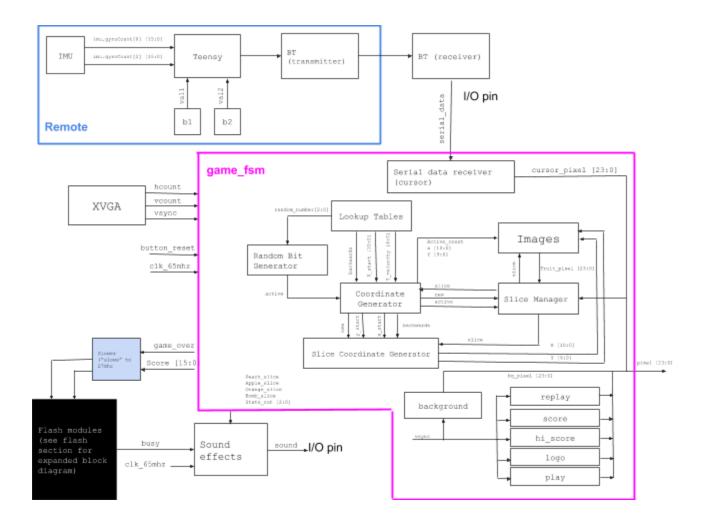

| Block Diagram                           | 4  |

| Modules                                 | 5  |

| Game FSM (Joint)                        | 5  |

| Random number generator (Nadia)         | 5  |

| Lookup Table (Nadia)                    | 6  |

| Coordinate Generator (Nadia)            | 6  |

| Coordinate Generator for Slices (Nadia) | 7  |

| Slice Finite State Machine (Nadia)      | 8  |

| Image Drawing Modules (Joint)           | 9  |

| Background (Lydia)                      | 10 |

| Remote (Lydia)                          | 10 |

| Serial data receiver (Lydia)            | 12 |

| Flash (Lydia)                           | 13 |

| Sound effects (Joint)                   | 14 |

| Challenges/Difficulties                 | 15 |

| Potential Improvements                  | 17 |

| Conclusions                             | 18 |

| References                              | 18 |

| Appendix                                | 19 |

## Overview

Fruit Ninja is a quite popular video game developed by Halfbrick and released in 2010. Countless Android and iOS users have played the game, and if not, have certainly heard of it. The conjunction of a straightforward user interface and Skinner box mechanics gave rise to an extremely popular game which was commercially successful by numerous standards.

The objective of the game is simple: drag your finger across a touch screen on a smart device of your choice and slice as many fruit as possible. Difficulty can vary based on which mode is selected in the start menu, and there exist various unique features to each mode. The simplicity of the design makes for an accessible game that can be catered to players of all ages.

The translation from software to hardware is always an interesting one; the methods for performing tasks are not always the same for both, and there are surely different problems to think about based on which medium is being used. We wanted to see how the different challenges in developing Fruit Ninja would change when recreating the game in hardware. The rest of this document describes the various revelations and trials we ran into in the creation of FPGA Fruit Ninja.

## Motivation

One of our motivations for making a game was its visibility. We personally find more satisfaction in a project with visible results. It also seemed like a fun idea to recreate something that we were already familiar with, but with our own spin. Additionally, we were especially interested in creating a remote because it combines previous knowledge from 6.08 (Arduino, IMUs, C++) with new concepts from 6.111 (serial). We were also eager to interface with different components like flash memory and sound creation.

# Summary

Our team decided to create an FPGA version of Fruit Ninja. Instead of using a touch screen, we created a remote with which a user could control a cursor. We loaded all the game graphics into the FPGA's BRAM, kept track of all time high score with flash memory, and added sound effects with a piezo buzzer. The basic rules and mechanics of the game are similar to the original, with fruit launching at random, game over on touching a bomb, and lives decreasing if fruits drop without being sliced.

# Block Diagram

## Modules

## Game FSM (Joint)

module game\_fsm (input [7:0] highscore, input vclock, input vsync, input serial\_data, input reset, input [10:0] hcount, input [9:0] vcount, output [23:0] pixel, output [7:0] ultimate\_score, output game\_state, output apple\_slice, output orange\_slice, output peach\_slice, output bomb\_slice, output [1:0] fell\_out, output [1:0] state out, input resetbutton);

This module does much of the heavy lifting in terms of where other modules ultimately are wired together. There are a couple of key parts of the game FSM:

- 1. Dealing with game state transitions: As the name of the module implies, this module determines when the game enters the start, play, and end states.

- a. START: This is the startup screen. It displays some images; pressing the start button on the remote whilst placing the cursor on the play button allows the user to start playing the game.

- b. PLAY: The user may play the game until he loses three lives by letting three fruit fall to the bottom of the screen unsliced, or by swiping through a bomb.

- c. GAME\_OVER: The user has lost the game. This screen displays the score the user accumulated in this iteration of the game and the high score. Pressing the start button on the remote whilst placing the cursor on the replay button allows the user to play the game once again.

- 2. Score and lives display: Using the image-drawing module from lab 3 (for rectangular shapes), we displayed the lives the user currently has using the fell and score outputs from the coordinate generator. The high score is also displayed at the end screen based on the input from the flash to the game FSM module.

- a. The score is displayed using numerous instantiations of the rectangular image-drawing module and displaying them or not based on what the score should be (so, a seven segment display but displayed using VGA).

- b. The location of the score shifts based on which game state the user is in, so the position registers for the score digits are changed in game state transitions at the clock edge.

- 3. Graphics: The spatial precedence in the game is determined in this module as below (elements sorted by z values):

background < fruits < bomb < cursor

The fruits have an arbitrary order. In general, order is set by checking for overlaps between elements and assigning pixel values to the desired top image. The state machine also determines which elements are on screen in which states.

## Random number generator (Nadia)

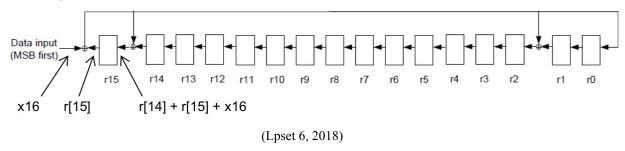

module randombitsgenerator (input clk, input data, output [15:0] randomnumber);

The cyclic redundancy check is quite similar to a linear-feedback shift register in their mathematical nature. LFSRs can seem to produce "random" bit strings if certain parameters are adjusted. This allows us to use a CRC-16 calculation to be a good proxy for "randomness", though not truly random (Rosenberg, 1997). Of course, trying out different parameters may be useful, as some data strings work better than others, as do different lengths of CRC generators and indexing into different bits for our lookup tables.

This module shifts in data bits to a CRC computation from an external source and outputs a 16 bit number that we can subsequently use in our lookup table to choose parameters that seem somewhat random for fruit motion generation.

The following is how CRC-16 is calculated:

## Lookup Table (Nadia)

module lookuptable (input clk, input [2:0] randomnumber, output reg [4:0] yvel1, output reg backwards1, output reg [9:0] xcostart1);

This module uses the random number generator to create usable parameters for the coordinate generator module. Based on the 3 bit input *randomnumber*, a case statement determines an initial y-velocity, backwards (whether the fruit moves left or right), and the initial x-coordinate for the fruit. These values are pre-selected by the envisioner based on what looks nice on the screen. Because the the gravity is chosen to be "2" for the duration of the game, initial velocities are chosen to be multiples of 2 to avoid overflow when determining the peak of the parabola in the coordinate generator module.

## Coordinate Generator (Nadia)

module coord\_generator (input rdy, input [2:0] slice, input active, input vsync, input [4:0] yvel, input backwards, input [9:0] xcostart, output [9:0] x\_coord, output reg [2:0] fell, output [9:0] y\_coord, output reg activeconst, output reg [7:0] score, output [4:0] yvelocity, output reg new);

This module takes in the inputs slice, active, vsync, backwards, yvel, xcostart, and outputs an x\_coord, y\_coord, activeconst, score, yvelocity, and new. It performs the coordinate calculation that allows the fruit on the screen to rise and fall along a parabolic trajectory. Instead of using the traditional parabolic motion equations and pipelining, the module takes advantage of sequential circuitry: numbers can be multiplied by repeatedly adding (which is what multiplication is, in essence). The module describes a finite state machine with two states: START and CALC. The finite state machine will only do state transitions while a ready signal (rdy) is asserted. Additionally, fell and y\_coord are reset at the positive edge of the ready signal (so as to restore lives at a new game and reduce a one-cycle flashing of the fruits and bomb) and the score is reset at the negative edge of the ready signal (so as to set the score to zero after a game is finished). Resetting the score at the positive edge proved to be an issue, if one is wondering.

#### **START**

the FSM latches on to an active bit (provided by the random number generator) and resets the y-coordinate, while taking in various parameters that determine the path in total from a lookup table (initial y velocity, initial x coordinate, and whether the fruit will travel backwards (left)). This latched active bit is then fed into activeconst to produce a level signal. This signal is routed to the image-drawing module to indicate that images that are inactive should not be drawn. New is asserted. This latching mechanism is important because the random number generator is changing at 65 MHz.

#### **CALC**

Y-coordinates and x-coordinates are generated. New is deasserted (this allows for a pulse signal when a new fruit appears on the screen; this is essential for deciding slice mechanics). The x-coordinate decreases or increases, based on the input backwards, by a fixed value:

```

x coord1 <= (left)? x coord1 - x vel: x coord1 + x vel;</pre>

```

\*left is the latched value of backwards provided as an input

The y-velocity changes every 9 (this is up to the user) cycles, as this means the fruit will move more slowly and hence more aesthetically. The y-velocity increases or decreases based on which part of the parabola the fruit is currently on, as does the y-coordinate:

\*reachedzero goes high when the y-velocity has, you guessed it, reached zero; y\_up goes low when reachedzero goes high

The fell, score, and new outputs are used to calculate game mechanics external to this module. Fell is calculated by seeing how many fruit go past the bottom of the screen while being active and unsliced. Score increments at the positive edge of the slice input. Finally, a state transition occurs when the fruit has traveled an entire parabola and is now past the bottom of the screen.

## Coordinate Generator for Slices (Nadia)

module coord\_generator\_slice (input begincalc, input vsync, input [4:0] yvel, input new, input backwards,

input [9:0] xcostart, input [9:0] ycostart, output [9:0] x coord, output [9:0] y coord);

Logically, this module is very similar to the regular coordinate generator except for the fact that it is a bit more specialized for bottom half slices of fruit. Essentially, there are two modules that determine the coordinates of the top (coord\_generator) and bottom (coord\_generator\_slice) halves at all times, but control signals such as active, new, and slice/begincalc (the two are used synonymously across coord generator and coord generator slice) are used to determine how exactly these coordinates are used.

The module calculates the coordinates for a downward parabolic motion from the peak of a trajectory. Such behavior necessitates the initial y velocity to be 0. The initial x-coordinate and y-coordinate are determined from the current x and y coordinates of the fruit's motion when it is unsliced. There are two states to this module's finite state machine: WAIT and CALC.

#### **WAIT**

In the wait state, the coordinates are such that the bottom half of the fruit is moving with the top half of the fruit, as it is unsliced (so the x-coordinate is the same and the y-coordinate is the same as the y-coordinate added to half the height of the picture so as to position the bottom half in the correct position). The state machine stays in this state until begincalc is asserted, which is the equivalent of the corresponding fruit being sliced.

#### **CALC**

In the calc state, the coordinates are generated and depend on where on the xy plane the fruit was split. The y-velocity still changes every nine cycles, as in the regular coordinate generator, but the y-velocity is either staying the same or incrementing. The x-coordinate depends on the backwards input; the bottom half could move either way. In this case, the input is always opposite the top half, as we wanted our fruit halves to separate in different directions for aesthetic purposes. When a new, active fruit is launched from the bottom, the finite state machine would go back to the wait state and again, the coordinates of the bottom half of the fruit would follow the top half of the fruit.

## Slice Finite State Machine (Nadia)

module slice\_dealer (input peachactive, input appleactive, input orangeactive, input clk, input apple\_new, input orange\_new, input peach\_new, input [23:0] applepix, input [23:0] cursorpix, input [23:0] orangepix, input [23:0] peachpix, output applesliced, output orangesliced, output peachsliced);

This module takes in the pixel values for the different fruit on the screen and the cursor and determines whether a slice has occurred. Separate finite machines for the different fruit allow for the slice output to stay high for the corresponding fruit while it is still in motion. The module additionally deals with the problem of inactive fruit and their slice status (in that inactive fruit cannot be sliced). The two states for the finite state machine are as follows:

#### WAIT

This state is the idle equivalent. The state machine resides in this state until it detects an overlap between any of the fruit pixels and the cursor pixels. Slice is deasserted the entire time the FSM is in this state.

#### SLICE

This state asserts slice as long as a new, active fruit has not appeared. The consequence of this is slice being a level signal as opposed to a pulse signal which allows for calculations in other modules that require such a construct (or, really, it's a design choice).

## Image Drawing Modules (Joint)

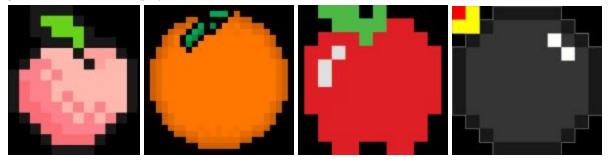

## Fruit and Bombs

Fruit and bombs are  $150 \times 150 \text{ 8-bit}$  bitmaps (except for the peach, which is  $132 \times 150$ ). We used this site to convert pngs to 8 bit bmp files. The coe files are generated with the MATLAB script provided under tools on the website and stored in the FPGA's BRAM. The background color on all the images is black, because the Verilog for the game replaces black pixels with the background color - all seemingly black colors in the fruit images are dark shades of grey.

## Drawing

Fruit are only drawn if the fruit is considered active (activeconst from coordinate generator); otherwise, the fruit will not appear on screen or have any effect on game score/lives.

The fruits are drawn similarly to the picture\_blob module provided in lab 3. However, because the fruits split apart, the top and bottom halves are actually drawn separately. Both read from the same ROM/coe file, - the top half of the fruit reads normally, but the bottom half of the fruit reads only from the bottom half of the coe file. Therefore, there are two image addresses (image\_addr\_1 for the top and image\_addr\_2 for the bottom):

```

assign image_addr_1 = (hcount-x) + (vcount-y) * WIDTH;

assign image_addr_2 = (hcount-xslice) + (vcount-yslice) * WIDTH +

(WIDTH * HEIGHT/2);

```

When a fruit is not sliced, image\_addr\_1 is used to index into the coe file. When the fruit is sliced, the top and bottom halves are drawn separately, and a register image\_addr is set to either 1 or 2 depending on which half is being drawn. Image\_addr\_2 indexes only into the bottom half of the coe file. Image\_addr is passed to the rom, which generates a signal image\_bits for mapping colors.

<sup>\*</sup>xslice and yslice correspond to the x and y coordinates of the bottom half of the fruit.

The bomb is drawn exactly like the picture\_blob module from lab 3, because it cannot be "sliced" (except for requiring active to be high in order for it to be drawn).

## Text & logo

The text and logos are also 8-bit bitmaps. All the text images are grayscale and only required one color coe file. These were made by downloading the font <u>Juicy Fruit</u> and exporting PowerPoint slides as images. These images also have a black background that is replaced by the game background.

## Background (Lydia)

module bg (input vsync, output [23:0] pixel);

The background for the game shifts between shades of pink and blue. This is achieved by fixing green and blue values at 164 and 255, respectively, while varying red. At every pulse of vsync, red increases by 1 until it reaches 255, at which point it decreases by 1 until it reaches 0 and the cycle begins again. I chose the fixed blue and green values by looking up an online RGB slider and picking which colors I thought would look best for a background.

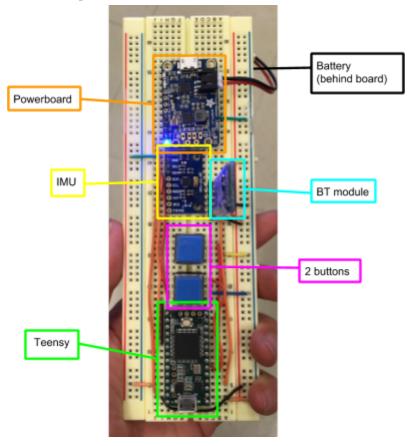

## Remote (Lydia)

## Description

The remote has two main purposes: to collect motion data from an IMU and process it, and to transmit data to the FPGA. The first task is accomplished by retrieving angular velocity from the gyroscope, integrating it to get position, and then translating the resulting values into a scale fit for the monitor (1024 x 768). The second task is accomplished by writing data to a pin (code provided by Joe) according to a serial protocol. The remote acts as the serial transmitter and the FPGA acts as the serial receiver.

## Components

The remote includes several components:

## **Teensy**

The Teensy is connected to everything else on the board. It computes x and y coordinates based on data from the IMU, and writes data to its TX pin to be sent by the transmitting BT module. Loop speed is set at 10 milliseconds.

## 2 buttons

The top button is meant for the user to select items, and the bottom button is meant to recalibrate the cursor position. Both buttons are active low. The top button's state is packaged into the data to be transmitted (see below for serial data transmission). A press on the bottom button triggers x and y coordinates to be reset to the center of the screen (coordinates (512, 389) on a 1024x768 screen).

#### **MPU9250**

This IMU is needed to retrieve angular velocity, so we used the gyroscope. The gyroscope measures 3 axes of motion, but we only needed two - the -z and x axes on the gyroscope, which correspond to the x and y axes, respectively, in the game and in relation to the screen. Integration is performed as so:

velocity = velocity $^{-1}$  X  $\delta$ t (loop speed) X leaky factor X sensitivity

The leaky factor is used to combat drift. Sensitivity helps the cursor move more with a smaller motion. The tricky part was balancing these two variables, because a lower leak is better for reducing drift, but a higher sensitivity is better for smoother and less constrained motion. Decreasing the loop speed also helps to create a smoother motion.

#### Adafruit BT module

The Bluetooth module was part of our stretch goals. Instead of wiring a connection from the Teensy's TX pin directly to an I/O pin on the FPGA, we connected BT modules to each of these. The BT modules are pre-programmed to connect to each other, and will reconnect and send data each time both are powered on. The tricky part is wiring them up correctly - the transmitting module receives data at its RX pin from the Teeny's TX pin, and the receiving module is connected to the FPGA with its TX pin.

#### Powerboard

This board allows the remote to be truly wireless, connecting power to a battery instead of an external source through micro-USB. As long as it is wired up correctly to supply power to the Teensy and the battery is charged, nothing more is needed for it to work. You can charge the battery by plugging in a micro-USB to the port on the board.

#### Serial data transmission

The data is packaged into 5 bytes to be sent from the Teensy - 2 bytes each for the 16 bit x and y coordinates, and 1 byte for the button. The data is big endian at the bit level and little endian at the byte level. The button data is only 1 bit long; the upper 7 bits are packed with 0s. The data is sent at 9600 baud.

## Serial data receiver (Lydia)

This module is similar to the serial receiver from lab 5c. Every time a sample is collected from the incoming serial data, it is shifted into a register. Instead of terminating after a certain number of bits have been received like in lab 5c, this serial receiver terminates after a certain number of bytes have been received and re-centers after every byte (see more in challenges and difficulties). The state machine is as follows:

#### **HIGH** (default/start state)

In this state, we wait for a certain amount of time before we transition into FALLING to wait for a falling edge. This is to establish that the FSM will not start in the middle of a data stream. Originally, the time was set to 2 ms. It was decreased to 200 ns after adding in Bluetooth functionality because the BT modules send packets at unequal spacing; sometimes bytes 4 and 5 will be bunched closely to byte 1 of the next round of data, so we shouldn't wait for data to be high too long before looking for a falling edge.

#### **FALLING**

This state transitions into FIRST when serial data goes low.

#### **FIRST**

The name of this state refers to the first bit of a byte, in which the retrieval of the start bit occurs 8 sampling clocks from the falling edge. After 8 sampling clocks, the state transitions to DATA.

#### DATA

In this state, a new bit is read in every 16 sampling clocks. After 8 bits have been collected, this state transitions back to FALLING in preparation for the next byte of data. If after 8 bits have been collected, 5 bytes have been collected in total (the total amount of data sent from the Teeny for this project is 5 bytes), the state transitions to DONE.

#### DONE

In the DONE state, the x coordinate, y coordinate, and button data are reconstructed from the bitstream according to its endianness.

## Flash (Lydia)

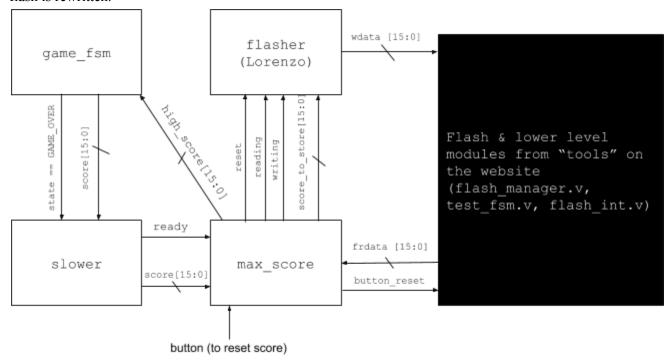

Flash memory is used in this project to store a high score that persists through shutdowns. On startup, the system is designed to read the high score from flash and store it in a register. Every time the user enters game over in the current power-on, if the user has gained a new high score, the register value is replaced and the flash is rewritten.

## Reading and Writing

In order to read and write to the flash, I used Lorenzo's modules from the 6.111 website and passed in signals from a max\_score module, which determines when to read and write from flash. Reading and writing

are the two signals which trigger their corresponding events when asserted in Lorenzo's module. The state machine for the max score module is as follows:

#### **STARTUP**

Reading is asserted and state immediately transitions to CHECK.

#### **CHECK**

Stay in this state if flash is busy; if flash is not busy, store the data coming from flash in a register and transition to IDLE.

#### **IDLE**

If a new high score has been achieved at game over, assert reset signals for one clock cycle, store the new high score in our register, put the new high score as data to be written to flash, and transition to RESET. Our project also supports the ability to reset the high score to 0, where all the signals are the same, except write data and the register are set to 0 and the events are triggered by a button press.

#### RESET

Reset signals are de-asserted. As soon as the flash is not busy, we transition to the STORE state and assert writing.

#### **STORE**

As soon as the flash is not busy, transition back to IDLE. The new score has now been written into flash.

## Interface to game

All the flash modules are timed with a 27 mhz clock, while all the game modules are timed with a 65 mhz clock. Because we need to pass signals from the game to the flash modules, all the game signals pass through 3 registers at 27 mhz before being used by the max score module.

## Sound effects (Joint)

module sfx (input clk, input apple\_slice, input orange\_slice, input peach\_slice, input bomb\_slice, input [1:0] lost life, input busy, input [1:0] state in, output reg sound);

This module generates the sound effects associated with certain events in the game. This is done by asserting high at certain frequencies of choice to an I/O pin which is wired to a piezo buzzer. The module is an FSM where states correspond to different sounds, Each state corresponds to a different sound, and each sound or state is only played for a certain amount of time before expiring back to an IDLE state and waiting for a new trigger. State transitions also determine play order in a logical fashion. For example, swiping a bomb is not mutually exclusive to receiving a high score, so both sounds should be played if both events occur. This can be done by adding conditions into the different states based on what can happen (i.e. if a bomb is hit and a new high score is achieved, the state transitions from BOMB to HIGH\_SCORE to IDLE, instead of directly returning to IDLE after BOMB). The sounds are the following:

1. Fruit slice: This sound plays upon slicing any fruit.

- 2. Lost life: This sound plays upon losing a life. It uses the fell output from the coordinate generator to see whether the previous number of lives is unequal to the current number of lives (naturally, if they are different, the sound will play). The sound does not play if the lives change from 0 to 3 (when the game is restarted).

- 3. Bomb swipe: This sound plays upon swiping a bomb. It uses the bomb\_slice input to see whether the bomb was slashed.

- 4. High score: This sound plays upon achieving a high score on the "game over" screen. The module uses the busy input to transition into playing a high score sound, because busy is asserted when a new high score is being written into flash.

# Challenges/Difficulties

We ended up changing our timeline substantially based on what would take the most amount of time. The graphics pipeline ended up taking as much time as suspected, but there were important design decisions that had to be made which would determine how modules ended up getting wired together and how signals had to be defined.

## Parabolic motion

The initial problem with graphics that had to be decided was how to generate the coordinates for the motion of the fruit. Our initial conception was that we would use the equations for parabolic motion:

Horizontal distance,

$$x = V_x t$$

Horizontal Velocity,  $V_x = V_{xo}$

Vertical distance,  $y = V_{yo}t - \frac{1}{2}gt^2$

Vertical Velocity,  $V_y = V_{yo} - gt$

(TutorVista, 2018)

This would require us to multiply numbers which is expensive time-wise. This would also require pipelining given the small period of the clock the module uses. Furthermore, we planned to have a "timer" module which would allow us to have small, discrete time intervals to supply to these equations. This is tedious given that iteratively adding does the same task, along with some ternary operators that allow us to determine the direction of motion for the fruit in the game.

## Slice drawing

When I (Nadia) was initially prototyping how to slice fruit for our stretch goal, I did it in a separate project (our compilation time was getting a bit high). The downwards motion after slicing the fruit was generated with the coord\_generator\_slice module that I had written, and the picture used was just an apple. Drawing a

separate rectangular image of uniform color and having that separate from the top half of the apple is easy: draw the top half and when they separate, draw the bottom half as a uniformly-colored rectangle.

However, to use the actual bottom half of the picture, we had to use different image addresses for the top and bottom halves. We thought a quick solution would be to instantiate two ROM modules: one for drawing the top half and one for drawing the bottom half. Of course, that is quite space-inefficient, so we ended up using the ROM module once and then varying the image address based on which part of the fruit the module should be drawing based on the slice input.

## Serial receiver

The serial receiver was modified from lab 5c because of the Bluetooth modules we used. We originally wrote the receiver similarly to lab 5c, where data collection starts at the falling edge for the first start bit and continues until a certain number of bits have been collected. However, adding Bluetooth modules meant that we needed to rewrite the receiver to terminate data collection after a certain number of bytes instead of bits, looping back to wait for a falling edge multiple times instead of just once.

The change wasn't difficult to make; it involved changing a few rules on state transitions, as well as keeping track of the number of bits and bytes stored. Another problem that we encountered, though, had to do with the sporadic nature of the BT module's packets. The data we sent was 5 bytes long; sometimes, byte 5 would be grouped more closely with byte 1 of the next pulse than byte 4 of its own. This meant that we had to decrease the amount of time waiting for data to be high before transitioning to watch for a falling edge (start bit). Otherwise, we might not have caught the start bit of byte 1 for the next pulse.

## Flash memory

Flash memory was frustrating to work with. The original approach involved using our max\_score module to send signals like doread, dowrite, and reset to the flash\_manager module provided on the 6.111 website. However, we ended up using Lorenzo's flash module as an intermediary module in between max\_score and flash\_manager, because his Verilog worked for sure. We didn't know until after using Lorenzo's code that two reset signals needed to be asserted to wipe flash. If we were to improve the game, it would make sense to do away with Lorenzo's module and pass signals directly from max\_score to flash manager, this time asserting both reset signals instead of just one.

## **Potential Improvements**

## Double Dabble

The method we used for generating the score on the screen was "quick and dirty". A nice, methodical way of converting binary into binary-coded decimal is the double dabble algorithm. From the output from a double dabble module, one could index into certain bits and find the ones, tens, and hundreds digit (and so on).

## FIFO for sound effects

One of the challenges of implementing sound effects included the situations where multiple sounds could be triggered. Because of the way sound was implemented, with states corresponding to each sound, it was easy to miss out on a sound if another was triggered. Our current fix introduces extra variables and conditions to the state transitions. To simplify the module, we could create a buffer for state transitions or sound outputs, where each event pushes another set of values onto the queue.

## Rotating fruit slices

Using the CORDIC algorithm, one can calculate the matrix transformations to rotate the halves of the fruit by rapidly changing the coordinates of the different pixels.

## Animated state transitions

When clicking play and replay, there could be some animations or movement on the buttons to make them look clicked. To do this, we could add an extra state in between START and PLAY that triggers on a button press and exits after completing its animation. There could also be some kind of game over animation with a flashing screen or exploding bomb, which would involve a similar fix.

## New project idea

We received a lot of compliments on the text used in our game, and that inspired the idea for a potential next final project - a program where users can sketch out a new font, then save the font and use it to type. This project could use a cursor like the Fruit Ninja project to write fonts, and store the data for each character in flash. It would also involve interfacing with a keyboard, which is not something that we explored in Fruit Ninja.

## Conclusions

We had a lot of fun integrating different concepts and labs from 6.111 into this final project. We were happy to adopt and modify certain parts of labs into our project (i.e. drawing with different image addresses from

lab 3, creating different sounds on a buzzer from lab 4). <u>Here</u> is a video Lydia made to document the process. Below are some thoughts for future students:

The absolute number one thing to keep in mind about not only this project but projects in general is that communication and timing are key. We found that consistently dedicating time to the project allowed for less stress later on, and more slack when needed. Slack can be useful when a certain aspect of a project is taking longer than expected, or for implementing more interesting features, both of which are possible situations.

We, personally, had quite a good history of communication. Though for most of the project, we worked on entirely different aspects, there were a handful of times when we pair-programmed. This helped us spot each other's logical inconsistencies and actually helped us get through bugs we would not have otherwise noticed as quickly. Asking your partner for advice is a good way to ensure that he or she knows what you are doing while giving you new ways of thinking about problems. Although not all project partners will work as closely as we did, it was nice to understand each other's modules for debugging/overall familiarity with all parts of the project.

We would also recommend making the project as modular as possible. This entails making sure there are no internal bugs in a certain aspect of the project, so that it can be integrated with ease. We found that making our modules fool-proof (or as much as we could) helped a lot during integration. Additionally, we would recommend learning how to use the logic analyzer, which we used to debug the serial receiver. We also used the hex display and LEDs a lot - the hex display was especially helpful, but had a lot of timing violations (note for future students).

Finally, ask for help, and do it often. The lovely staff in 6.111 are dedicated to helping you understand what you are doing, and there are many resources to help you debug. However, the prerequisite to this is not procrastinating. Starting early and giving substantial effort at all times will mean that you will run into problems early on, which is exactly what you want. You do not want to run into major design issues or tough bugs when there is much else to be done, but this is a fact of life, and not necessarily something you don't know.

## References

- 1. "CRC-16 Calculation." *6.111 Introduction to Digital Systems Laboratory*. October 2018. http://web.mit.edu/6.111/volume2/www/f2018/index.html

- 2. Rosenberg, B. (1997, October 28). Generation of pseudorandom numbers by a shift register.

Retrieved from

<a href="http://www.cs.miami.edu/home/burt/learning/Csc609.022/random">http://www.cs.miami.edu/home/burt/learning/Csc609.022/random</a> numbers.html</a>

- 3. TutorVista. "Projectile Motion Formula." *TutorVista.com*. 2018. Retrieved from <a href="https://formulas.tutorvista.com/physics/projectile-motion-formula.html">https://formulas.tutorvista.com/physics/projectile-motion-formula.html</a>

# Appendix

#### Game FSM

```

module fruit ninja (beep, audio_reset_b, ac97_sdata_out, ac97_sdata_in, ac97_synch,

ac97 bit clock,

vga out red, vga out green, vga out blue, vga out sync b,

vga out blank b, vga out pixel clock, vga out hsync,

vga out vsync,

tv out ycrcb, tv out reset b, tv out clock, tv out i2c clock,

tv out i2c data, tv out pal ntsc, tv out hsync b,

tv_out_vsync_b, tv_out_blank_b, tv_out_subcar_reset,

tv_in_ycrcb, tv_in_data_valid, tv_in_line_clock1,

tv in line clock2, tv in aef, tv in hff, tv in aff,

tv_in_i2c_clock, tv_in_i2c_data, tv_in_fifo_read,

tv_in_fifo_clock, tv_in_iso, tv_in_reset_b, tv_in_clock,

ram0 data, ram0 address, ram0 adv ld, ram0 clk, ram0 cen b,

ram0 ce b, ram0 oe b, ram0 we b, ram0 bwe b,

ram1_data, ram1_address, ram1_adv_ld, ram1_clk, ram1_cen_b,

ram1 ce b, ram1 oe b, ram1 we b, ram1 bwe b,

clock_feedback_out, clock_feedback_in,

flash data, flash address, flash ce b, flash oe b, flash we b,

flash reset b, flash sts, flash byte b,

rs232 txd, rs232 rxd, rs232 rts, rs232 cts,

mouse clock, mouse data, keyboard clock, keyboard data,

clock 27mhz, clock1, clock2,

disp_blank, disp_data_out, disp_clock, disp_rs, disp_ce_b,

disp reset b, disp data in,

button0, button1, button2, button3, button enter, button right,

button_left, button_down, button_up,

switch,

led.

user1, user2, user3, user4,

daughtercard,

systemace data, systemace address, systemace ce b,

systemace we b, systemace oe b, systemace irq, systemace mpbrdy,

analyzer1 data, analyzer1 clock,

```

```

analyzer2 data, analyzer2 clock,

analyzer3 data, analyzer3 clock,

analyzer4 data, analyzer4 clock);

output beep, audio reset b, ac97 synch, ac97 sdata out;

input ac97 bit clock, ac97 sdata in;

output [7:0] vga out red, vga out green, vga out blue;

output vga out sync b, vga out blank b, vga out pixel clock,

vga out hsync, vga out vsync;

output [9:0] tv out ycrcb;

output tv out reset b, tv out clock, tv out i2c clock, tv out i2c data,

tv_out_pal_ntsc, tv_out_hsync_b, tv_out_vsync_b, tv_out_blank_b,

tv_out_subcar_reset;

input [19:0] tv_in_ycrcb;

input tv in data valid, tv in line clock1, tv in line clock2, tv in aef,

tv in hff, tv in aff;

output tv in i2c clock, tv in fifo read, tv in fifo clock, tv in iso,

tv in reset b, tv in clock;

inout tv in i2c data;

inout [35:0] ram0 data;

output [18:0] ram0 address;

output ram0 adv ld, ram0 clk, ram0 cen b, ram0 ce b, ram0 oe b, ram0 we b;

output [3:0] ram0 bwe b;

inout [35:0] ram1 data;

output [18:0] ram1 address;

output ram1_adv_ld, ram1_clk, ram1_cen_b, ram1_ce_b, ram1_oe_b, ram1_we_b;

output [3:0] ram1 bwe b;

input clock_feedback_in;

output clock feedback out;

inout [15:0] flash data;

output [23:0] flash_address;

output flash_ce_b, flash_oe_b, flash_we_b, flash_reset_b, flash_byte_b;

input flash sts;

output rs232 txd, rs232 rts;

input rs232 rxd, rs232 cts;

input mouse clock, mouse data, keyboard clock, keyboard data;

input clock 27mhz, clock1, clock2;

output disp_blank, disp_clock, disp_rs, disp_ce_b, disp_reset_b;

input disp data in;

output disp data out;

input button0, button1, button2, button3, button_enter, button_right,

button left, button down, button up;

input [7:0] switch;

output [7:0] led;

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

```

```

inout [15:0] systemace data;

output [6:0] systemace address;

output systemace ce b, systemace we b, systemace oe b;

input systemace irq, systemace mpbrdy;

output [15:0] analyzer1_data, analyzer2_data, analyzer3_data,

analyzer4 data;

output analyzer1 clock, analyzer2 clock, analyzer3 clock, analyzer4 clock;

// I/O Assignments

// Audio Input and Output

assign beep= 1'b0;

assign audio reset b = 1'b0;

assign ac97_synch = 1'b0;

assign ac97 sdata out = 1'b0;

// ac97 sdata in is an input

// Video Output

assign tv out vcrcb = 10'h0;

assign tv out reset b = 1'b0;

assign tv out clock = 1'b0;

assign tv out i2c clock = 1'b0;

assign tv out i2c data = 1'b0;

assign tv_out_pal_ntsc = 1'b0;

assign tv out hsync b = 1'b1;

assign tv out vsync b = 1'b1;

assign tv out blank b = 1'b1;

assign tv_out_subcar_reset = 1'b0;

// Video Input

assign tv in i2c clock = 1'b0;

assign tv_in_fifo_read = 1'b0;

assign tv_in_fifo_clock = 1'b0;

assign tv in iso = 1'b0;

assign tv in reset b = 1'b0;

assign tv in clock = 1'b0;

assign tv_in_i2c_data = 1'bZ;

// tw in yercb, tw in data valid, tw in line clock1, tw in line clock2,

// tv in aef, tv in hff, and tv in aff are inputs

// SRAMs

assign ram0 data = 36'hZ;

assign ram0 address = 19'h0;

assign ram0 adv ld = 1'b0;

assign ram0 clk = 1'b0;

assign ram0 cen b = 1'b1;

assign ram0 ce b = 1'b1;

assign ram0 oe b = 1'b1;

assign ram0 we b = 1'b1;

assign ram0_bwe_b = 4'hF;

assign ram1_data = 36'hZ;

assign ram1_address = 19'h0;

assign ram1 adv ld = 1'b0;

assign ram1 clk = 1'b0;

```

```

assign ram1 cen b = 1'b1;

assign ram1 ce b = 1'b1;

assign ram1_oe_b = 1'b1;

assign ram1 we b = 1'b1;

assign ram1 bwe b = 4'hF;

assign clock feedback out = 1'b0;

// clock_feedback_in is an input

// Flash ROM

// assign flash data = 16'hZ;

// assign flash_address = 24'h0;

// assign flash_ce_b = 1'b1;

// assign flash oe b = 1'b1;

// assign flash we b = 1'b1;

// assign flash_reset_b = 1'b0;

// assign flash_byte_b = 1'b1;

// flash sts is an input

// RS-232 Interface

assign rs232 txd = 1'b1;

assign rs232 rts = 1'b1;

// rs232 rxd and rs232 cts are inputs

// PS/2 Ports

// mouse clock, mouse data, keyboard clock, and keyboard data are inputs

// LED Displays

assign disp blank = 1'b1;

assign disp clock = 1'b0;

assign disp_rs = 1'b0;

assign disp ce b = 1'b1;

assign disp reset b = 1'b0;

assign disp data out = 1'b0;

// disp_data_in is an input

// Buttons, Switches, and Individual LEDs

//lab3 assign led = 8'hFF;

// button0, button1, button2, button3, button_enter, button_right,

// button_left, button_down, button_up, and switches are inputs

// User I/Os

assign user1 = 32'hZ;

assign user2 = 32'hZ;

assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace data = 16'hZ;

assign systemace address = 7'h0;

assign systemace_ce_b = 1'b1;

assign systemace we b = 1'b1;

assign systemace oe b = 1'b1;

// systemace_irq and systemace_mpbrdy are inputs

// Logic Analyzer

assign analyzer1 data = 16'h0;

assign analyzer1_clock = 1'b1;

```

```

assign analyzer2 data = 16'h0;

assign analyzer2 clock = 1'b1;

assign analyzer3 data = 16'h0;

assign analyzer3 clock = 1'b1;

assign analyzer4 data = 16'h0;

assign analyzer4 clock = 1'b1;

// fruit ninja

//

// use FPGA's digital clock manager to produce a

// 65MHz clock (actually 64.8MHz)

wire clock 65mhz unbuf, clock 65mhz;

DCM vclk1(.CLKIN(clock 27mhz),.CLKFX(clock 65mhz unbuf));

// synthesis attribute CLKFX DIVIDE of vclk1 is 10

// synthesis attribute CLKFX MULTIPLY of vclk1 is 24

// synthesis attribute CLK FEEDBACK of vclk1 is NONE

// synthesis attribute CLKIN PERIOD of vclk1 is 37

BUFG vclk2(.O(clock 65mhz),.I(clock 65mhz unbuf));

// power-on reset generation

wire power on reset; // remain high for first 16 clocks

SRL16 reset sr (.D(1'b0), .CLK(clock 65mhz), .Q(power on reset),

.AO(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1));

defparam reset sr.INIT = 16'hFFFF;

// ENTER button is user reset

wire reset, user reset;

debounce

db1(.reset(power on reset),.clock(clock 65mhz),.noisy(~button enter),.clean(user reset));

assign reset = user_reset | power_on_reset;

// generate basic XVGA video signals

wire [10:0] hcount;

wire [9:0] vcount;

wire hsync, vsync, blank;

xvga xvga1(.vclock(clock 65mhz),.hcount(hcount),.vcount(vcount),

.hsync(hsync),.vsync(vsync),.blank(blank));

reg data1, data2, data3;

wire game state;

// feed XVGA signals to fruit ninja game

wire [23:0] pixel;

// scorekeeping

wire [7:0] ultimate score;

wire [15:0] score;

// Sounds

wire [1:0] fell;

wire apple_slice, orange_slice, peach_slice, bomb_slice;

wire [1:0] state;

game_fsm fruit_ninja(.resetbutton(~button_enter), .state_out(state), .vsync(vsync),

.serial data(data3), .vclock(clock 65mhz), .reset(reset), .ultimate score(ultimate score),

.hcount(hcount), .vcount(vcount) ,.pixel(pixel), .game_state(game_state), .highscore(score[7:0]),

```

```

.fell out(fell), .apple slice(apple slice), .orange slice(orange slice),

.peach slice(peach slice), .bomb slice(bomb slice));

reg [23:0] rgb;

reg b, hs, vs;

always @(posedge clock 65mhz) begin

data1 <= user2[0];

data2 <= data1;

data3 <= data2;

hs <= hsync;

vs <= vsync;

b <= blank;

rgb <= pixel;

end

// VGA Output. In order to meet the setup and hold times of the

// AD7125, we send it \simclock 65mhz.

assign vga out red = rgb[23:16];

assign vga out green = rgb[15:8];

assign vga out blue = rgb[7:0];

assign vga out sync b = 1'b1;

// not used

assign vga out blank b = ~b;

assign vga out pixel clock = ~clock 65mhz;

assign vga out hsync = hs;

assign vga out vsync = vs;

wire [639:0] dots;

wire writemode;

wire [15:0] wdata;

wire dowrite;

wire [22:0] raddr;

wire [15:0] frdata;

wire doread;

wire busy;

wire [11:0] fsmstate;

wire [4:0] state out;

wire [15:0] score_to_store;

wire writing;

wire reading;

wire flash reset;

wire up reset;

wire ready;

wire [15:0] current_score;

flash manager flash(.clock(clock 27mhz), .reset(flash reset), .dots(dots), .writemode(writemode),

.wdata(wdata), .dowrite(dowrite), .raddr(raddr), .frdata(frdata), .doread(doread), .busy(busy),

.flash_data(flash_data), .flash_address(flash_address),

.flash_ce_b(flash_ce_b),.flash_oe_b(flash_oe_b), .flash_we_b(flash_we_b),

.flash reset b(flash reset b), .flash sts(flash sts), .flash byte b(flash byte b),

.fsmstate(fsmstate));

{\tt flasher \ my\_flash \ (.clk(clock\_27mhz), \ .busy(busy), \ .fsmstate(fsmstate), \ .dots(dots),}

.writing(writing),.reading(reading), .wdata(wdata), .writemode(writemode), .dowrite(dowrite),

.raddr(raddr), .doread(doread), .score_to_store(score_to_store), .up(up_reset));

slower slow(.clk(clock_27mhz), .r_in(game_state), .c_in(ultimate_score), .r(ready),

.c(current score));

```

```

max score my max (.current score(current score), .score from flash(frdata), .clk(clock 27mhz),

.ready(ready), .busy(busy), .reset(flash reset), .writing(writing), .reading(reading),

.up_reset(up_reset),.score(score), .score_to_store(score_to_store), .state_out(state_out),

.reset score(!button up));

wire r;

sfx sounds(.state_in(state), .clk(clock_65mhz), .apple_slice(apple_slice),

.orange_slice(orange_slice), .peach_slice(peach_slice), .bomb_slice(bomb_slice),

.busy(busy), .sound(user4[0]), .lost life(fell), .r(r));

assign led[7] = \sim r;

assign led[6] = ~busy;

assign led[5] = ~game state;

assign led[4:0] = 5'b11111;

endmodule

module slower (input clk,

input r in,

input [6:0] c in,

output reg r,

output reg [6:0] c);

reg a, b, d;

reg [15:0] one;

reg [15:0] two;

reg [15:0] three;

always @ (posedge clk) begin

a <= r in;

b <= a;

d <= b;

one <= c in;

two <= one;

three <= two;

r <= d;

c <= three;

end

endmodule

// xvga: Generate XVGA display signals (1024 x 768 @ 60Hz)

//

module xvga(input vclock,

output reg [10:0] hcount,

// pixel number on current line

output reg [9:0] vcount, // line number

output reg vsync,hsync,blank);

// horizontal: 1344 pixels total

// display 1024 pixels per line

reg hblank, vblank;

wire hsyncon, hsyncoff, hreset, hblankon;

assign hblankon = (hcount == 1023);

assign hsyncon = (hcount == 1047);

assign hsyncoff = (hcount == 1183);

assign hreset = (hcount == 1343);

// vertical: 806 lines total

```

```

// display 768 lines

wire vsyncon, vsyncoff, vreset, vblankon;

assign vblankon = hreset & (vcount == 767);

assign vsyncon = hreset & (vcount == 776);

assign vsyncoff = hreset & (vcount == 782);

assign vreset = hreset & (vcount == 805);

// sync and blanking

wire next hblank, next vblank;

assign next hblank = hreset ? 0 : hblankon ? 1 : hblank;

assign next vblank = vreset ? 0 : vblankon ? 1 : vblank;

always @(posedge vclock) begin

hcount <= hreset ? 0 : hcount + 1;

hblank <= next hblank;</pre>

hsync <= hsyncon ? 0 : hsyncoff ? 1 : hsync; // active low</pre>

vcount <= hreset ? (vreset ? 0 : vcount + 1) : vcount;</pre>

vblank <= next vblank;</pre>

vsync <= vsyncon ? 0 : vsyncoff ? 1 : vsync; // active low</pre>

blank <= next vblank | (next hblank & ~hreset);</pre>

end

endmodule

// game fsm: the main game FSM

module game fsm (

input [7:0] highscore,

input vclock,

// 65MHz clock

input vsync,

input serial data,

// 1 to initialize module

input reset,

input [10:0] hcount, // horizontal index of current pixel (0..1023)

input [9:0] vcount, // vertical index of current pixel (0..767) output [23:0] pixel, // game's pixel // r=23:16, g=15:8, b=7:0

output [7:0] ultimate score,

output game state,

output apple slice,

output orange slice,

output peach slice,

output bomb slice,

output [1:0] fell out,

output [1:0] state out,

input resetbutton);

wire [15:0] yeet; wire data;

// apple wires

wire [4:0] yvel; wire [9:0] xcostart; wire backwards;

wire [23:0] apple pixel; wire [9:0] apple x; wire [9:0] apple y;

// orange wires

wire [4:0] yvell; wire [9:0] xcostart1; wire backwards1;

wire [23:0] orange_pixel; wire [9:0] orange_x; wire [9:0] orange_y;

// bomb wires

```

```

wire [4:0] yvel2; wire [9:0] xcostart2; wire backwards2;

wire [23:0] bomb pixel; wire [9:0] bomb x; wire [9:0] bomb y;

// peach wires

wire [4:0] yvel3; wire [9:0] xcostart3; wire backwards3;

wire [23:0] peach pixel; wire [9:0] peach_x; wire [9:0] peach_y;

// other stuff lol

wire [23:0] game pixel;

wire overlap;

reg [1:0] state = 0;

parameter START = 0;

parameter PLAY = 1;

parameter GAME_OVER = 2;

assign state out = state;

// Random number generation

randombitsqenerator randos (.clk(vsync), .data(data), .randomnumber(yeet));

lookuptable appletable (.clk(vsync), .randomnumber(yeet[14:12]), .yvel1(yvel),

.xcostart1(xcostart), .backwards1(backwards));

lookuptable orangetable (.clk(vsync), .randomnumber(yeet[2:0]), .yvel1(yvel1),

.xcostart1(xcostart1), .backwards1(backwards1));

lookuptablebomb bombtable (.clk(vsync), .randomnumber(yeet[8:6]), .yvel1(yvel2),

.xcostart1(xcostart2), .backwards1(backwards2));

lookuptable peachtable (.clk(vsync), .randomnumber(yeet[3:1]), .yvel1(yvel3),

.xcostart1(xcostart3), .backwards1(backwards3));

// Coordinates

reg ready;

wire [2:0] apple fell; wire active apple; wire [7:0] apple score; wire applenew; wire

applesliced; wire [4:0] yvelocity apple;

coord_generator apple_coords(.yvelocity(yvelocity_apple), .new(applenew),

.score(apple_score), .active(yeet[0]), .activeconst(active_apple), .rdy(ready),

.slice(applesliced), .vsync(vsync), .yvel(yvel), .xcostart(xcostart),

.backwards(backwards), .x coord(apple x), .y coord(apple y), .fell(apple fell));

wire [2:0] orange fell; wire active orange; wire [7:0] orange score; wire orangenew; wire

orangesliced; wire [4:0] yvelocity orange;

coord generator orange coords (.yvelocity (yvelocity orange), .new (orangenew),

.score(orange score), .active(yeet[1]), .activeconst(active orange),

.rdy(ready), .slice(orangesliced), .vsync(vsync), .yvel(yvel1), .xcostart(xcostart1),

.backwards(backwards1), .x coord(orange x), .y coord(orange y), .fell(orange fell));

wire [2:0] bomb fell; wire active bomb; wire [3:0] bomb score;

coord generator bomb coords(.score(bomb score), .active(yeet[2]),

.activeconst(active bomb), .rdy(ready), .slice(0), .vsync(vsync), .yvel(yvel2),

.xcostart(xcostart2), .backwards(backwards2), .x coord(bomb x), .y coord(bomb y),

.fell(bomb_fell));

wire [2:0] peach fell; wire active peach; wire [7:0] peach score; wire peachnew; wire

peachsliced; wire [4:0] yvelocity peach;

coord_generator peach_coords(.yvelocity(yvelocity_peach), .new(peachnew),

.score(peach_score), .active(yeet[5]), .activeconst(active_peach), .rdy(ready),

.slice(peachsliced), .vsync(vsync), .yvel(yvel3), .xcostart(xcostart3),

.backwards(backwards3), .x_coord(peach_x), .y_coord(peach_y), .fell(peach_fell));

```

```

assign ultimate score = apple score + orange score + peach score;

// Fruit & bombs

wire [9:0] apple x2, peach x2, orange x2;

wire [9:0] orange y2, apple y2, peach y2;

apple appley(.active(active apple), .slice(applesliced), .pixel clk(vclock),

.hcount(hcount), .xslice(apple x2), .yslice(apple y2), .vcount(vcount), .x(apple x),

.y(apple y), .pixel(apple pixel));

orange orangey(.active(active_orange), .slice(orangesliced), .pixel_clk(vclock),

.hcount(hcount), .vcount(vcount), .x(orange x), .y(orange y), .xslice(orange x2),

.yslice(orange_y2), .pixel(orange_pixel));

bomb bomby(.active(active_bomb), .slice(0), .pixel_clk(vclock), .hcount(hcount),

.vcount(vcount), .x(bomb_x), .y(bomb_y), .pixel(bomb_pixel));

peach peachy(.active(active peach), .slice(peachsliced), .pixel clk(vclock),

.hcount(hcount), .vcount(vcount), .x(peach x), .y(peach y), .xslice(peach x2),

.yslice(peach y2), .pixel(peach pixel));

// Flying slices

coord_generator_slice apple_slice_coords (.yvel(0), .begincalc(applesliced),

.vsync(vsync), .new(applenew), .backwards(~backwards),

.xcostart(apple_x), .ycostart(apple_y + 75), .x_coord(apple_x2), .y_coord(apple_y2));

coord generator slice orange slice coords (.yvel(0), .begincalc(orangesliced),

.vsync(vsync), .new(orangenew), .backwards(~backwards1),

.xcostart(orange_x), .ycostart(orange_y + 75), .x_coord(orange_x2), .y_coord(orange_y2));

coord generator slice peach slice coords (.yvel(0), .begincalc(peachsliced),

.vsync(vsync), .new(peachnew), .backwards(~backwards3),

.xcostart(peach_x), .ycostart(peach_y + 75), .x_coord(peach_x2), .y_coord(peach_y2));

assign apple slice = applesliced && (state == PLAY);

assign peach slice = peachsliced && (state == PLAY);

assign orange_slice = orangesliced && (state == PLAY);

assign fell_out = apple_fell + orange_fell + peach_fell;

// Lives

wire [23:0] pixel life1; reg display life1;

blob life1 (.color(24'hFF FF FF), .x(100), .y(100), .clk(vclock), .hcount(hcount),

.vcount(vcount), .display(display life1), .pixel(pixel life1));

wire [23:0] pixel life2; reg display life2;

\verb|blob| life2| (.color(24'hFF_FF_FF), .x(170), .y(100), .clk(vclock), .hcount(hcount), \\

.vcount(vcount), .display(display life2), .pixel(pixel_life2));

wire [23:0] pixel life3; reg display life3;

blob life3 (.color(24'hFF FF FF), .x(240), .y(100), .clk(vclock),.hcount(hcount),

.vcount(vcount), .display(display life3), .pixel(pixel life3));

// Cursor

wire [23:0] cursor pixel;

wire [15:0] cursor x;

wire [15:0] cursor y;

wire [7:0] button;

cursor coords generator (.serial data(serial data), .clk(vclock), .x coord(cursor x),

.y_coord(cursor_y), .button(button));

```

```

blob #(.WIDTH(10), .HEIGHT(10)) cursor (.color(24'hFF FF 00), .clk(vclock),

.x(cursor x[10:0]), .y(cursor y[9:0]), .hcount(hcount), .vcount(vcount), .display(1),

.pixel(cursor pixel));

// Slice management

slice dealer slicey (.peachactive(active peach), .appleactive(active apple),

.orangeactive(active orange), .clk(vclock), .apple new(applenew), .orange new(orangenew),

.peach_new(peachnew), .applepix(apple_pixel), .cursorpix(cursor_pixel),

.orangepix(orange_pixel), .peachpix(peach_pixel), .applesliced(applesliced),

.orangesliced(orangesliced), .peachsliced(peachsliced));

// Background

wire [23:0] bg pixel;

bg background(.vsync(vsync), .clk(vclock), .pixel(bg pixel));

// Start and end screens

wire [23:0] start pixel;

wire [23:0] logo pixel;

wire [23:0] play_pixel;

logo blob logo picture (.pixel clk(vclock), .x(362), .y(200), .hcount(hcount),

.vcount(vcount), .pixel(logo pixel));

play blob play text(.pixel clk(vclock), .x(424), .y(400), .hcount(hcount),

.vcount(vcount), .pixel(play pixel));

assign start pixel = play pixel | logo pixel;

wire [23:0] end pixel;

wire [23:0] replay_pixel;

wire [23:0] score pixel;

wire [23:0] high score pixel;

replay_blob replay_button(.pixel_clk(vclock), .x(297), .y(244), .hcount(hcount),

.vcount(vcount), .pixel(replay_pixel));

score blob score text (.pixel clk(vclock), .x(297), .y(350), .hcount(hcount),

.vcount(vcount), .pixel(score pixel));

hi blob high score (.pixel clk(vclock), .x(297), .y(425), .hcount(hcount),

.vcount(vcount), .pixel(high score pixel));

// number scores

wire [23:0] top left 1; reg display 1; reg [9:0] x1; reg [8:0] y1;

blob #(.WIDTH(10), .HEIGHT(44)) s 10(.clk(vclock), .display(display 1),

.color(24'hff_ff_ff), .x(x1), .y(y1), .hcount(hcount), .vcount(vcount),

.pixel(top left 1));

wire [23:0] top 1; reg display 2; reg [9:0] x2; reg [8:0] y2;

\verb|blob| \# (.WIDTH(44), .HEIGHT(10)) s_11 (.clk(vclock), .display(display_2), \\

. \verb|color|(24'hFF_FF_FF)|, ... (x2)|, ... (y2)|, ... (hcount(hcount))|, ... (vcount(vcount))|, ... (vcount(vcoun

wire [23:0] top right 1; reg display 3; reg [9:0] x3; reg [8:0] y3;

blob #(.WIDTH(10), .HEIGHT(44)) s_12(.clk(vclock), .display(display_3),

.color(24'hff_Ff_Ff), .x(x3), .y(y3), .hcount(hcount), .vcount(vcount),

.pixel(top right 1));

wire [23:0] bottom left 1; reg display 4; reg [9:0] x4; reg [8:0] y4;

blob #(.WIDTH(10), .HEIGHT(44)) s_13(.clk(vclock), .display(display_4),

```

```

.color(24'hff ff ff), .x(x4), .y(y4), .hcount(hcount), .vcount(vcount),

.pixel(bottom left 1));

wire [23:0] bottom right 1; reg display 5; reg [9:0] x5; reg [8:0] y5;

blob #(.WIDTH(10), .HEIGHT(54)) s 14(.clk(vclock), .display(display 5),

.color(24'hff Ff Ff), .x(x5), .y(y5), .hcount(hcount), .vcount(vcount),

.pixel(bottom right 1));

wire [23:0] middle_1; reg display_6; reg [9:0] x6; reg [8:0] y6;

blob #(.WIDTH(44), .HEIGHT(10)) s_15(.clk(vclock), .display(display_6),

.color(24'hff ff ff), .x(x6), .y(y6), .hcount(hcount), .vcount(vcount), .pixel(middle 1));

wire [23:0] bottom_1; reg display_7; reg [9:0] x7; reg [8:0] y7;

blob #(.WIDTH(44), .HEIGHT(10)) s_16(.clk(vclock), .display(display_7),

. \verb|color|(24'hFF_FF_FF|) , .x(x7), .y(y7), .hcount(hcount), .vcount(vcount), .pixel(bottom 1)); \\

wire [23:0] top left 2; reg display 8; reg [9:0] x8; reg [8:0] y8;

blob #(.WIDTH(10), .HEIGHT(44)) s_20(.clk(vclock),.display(display_8),

.color(24'hFF_FF_FF), .x(x8), .y(y8), .hcount(hcount), .vcount(vcount),

.pixel(top_left_2));

wire [23:0] top 2; reg display 9; reg [9:0] x9; reg [8:0] y9;

blob #(.WIDTH(44), .HEIGHT(10)) s 21(.clk(vclock),.display(display 9),

.color(24'hff Ff Ff), .x(x9), .y(y9), .hcount(hcount), .vcount(vcount), .pixel(top 2));

wire [23:0] top right 2; reg display 10; reg [9:0] x10; reg [8:0] y10;

blob #(.WIDTH(10), .HEIGHT(44)) s 22(.clk(vclock),.display(display 10),

.color(24'hff Ff Ff), .x(x10), .y(y10), .hcount(hcount), .vcount(vcount),

.pixel(top right 2));

wire [23:0] bottom left 2; reg display 11; reg [9:0] x11; reg [8:0] y11;

blob #(.WIDTH(10), .HEIGHT(44)) s 23(.clk(vclock),.display(display 11),

.color(24'hff_ff_ff), .x(x11), .y(y11), .hcount(hcount), .vcount(vcount),

.pixel(bottom left 2));

wire [23:0] bottom right 2; reg display 12; reg [9:0] x12; reg [8:0] y12;

blob #(.WIDTH(10), .HEIGHT(54)) s 24(.clk(vclock),.display(display 12),

.color(24'hFF_FF_FF), .x(x12), .y(y12), .hcount(hcount), .vcount(vcount),

.pixel(bottom right 2));

wire [23:0] middle 2; reg display 13; reg [9:0] x13; reg [8:0] y13;

blob #(.WIDTH(44), .HEIGHT(10)) s_25(.clk(vclock), .display(display_13),

.color(24'hff_ff_ff), .x(x13), .y(y13), .hcount(hcount), .vcount(vcount),

.pixel(middle 2));

wire [23:0] bottom 2; reg display 14; reg [9:0] x14; reg [8:0] y14;

blob #(.WIDTH(44), .HEIGHT(10)) s 26(.clk(vclock), .display(display 14),

.color(24'hFF_FF_FF), .x(x14), .y(y14), .hcount(hcount), .vcount(vcount),

.pixel(bottom 2));

// high score instantiations

wire [23:0] top left 3; reg display 15;

blob #(.WIDTH(10), .HEIGHT(44)) s 30(.clk(vclock), .display(display 15),

.color(24'hff ff ff), .x(x1+60+65), .y(y1+78), .hcount(hcount), .vcount(vcount),

.pixel(top_left_3));

wire [23:0] top 3; reg display 16;

blob #(.WIDTH(44), .HEIGHT(10)) s 31(.clk(vclock), .display(display 16),

.color(24'hff ff ff), .x(x2 + 60 + 65), .y(y2 + 78), .hcount(hcount), .vcount(vcount),

.pixel(top 3));

wire [23:0] top right 3; reg display 17;

blob #(.WIDTH(10), .HEIGHT(44)) s 32(.clk(vclock), .display(display 17),

.color(24'hff ff ff), .x(x3 + 60 + 65), .y(y3 + 78), .hcount(hcount), .vcount(vcount),

.pixel(top_right_3));

wire [23:0] bottom_left_3; reg display_18;

blob #(.WIDTH(10), .HEIGHT(44)) s 33(.clk(vclock), .display(display 18),

. \texttt{color}(24'\texttt{hFF}\_\texttt{FF}\_\texttt{FF}), \ .x(x4 + 60 + 65), \ .y(y4 + 78), \ .\texttt{hcount}(\texttt{hcount}), \ .\texttt{vcount}(\texttt{vcount}),

.pixel(bottom_left_3));

wire [23:0] bottom_right_3; reg display_19;

blob #(.WIDTH(10), .HEIGHT(54)) s 34(.clk(vclock), .display(display 19),

.color(24'hFF_FF_FF), .x(x5+60+65), .y(y5+78), .hcount(hcount), .vcount(vcount),

```

```

.pixel(bottom right 3));

wire [23:0] middle 3; reg display 20;

blob #(.WIDTH(44), .HEIGHT(10)) s_35(.clk(vclock), .display(display_20),

.color(24'hff ff ff), .x(x6 + 60 + 65), .y(y6 + 78), .hcount(hcount), .vcount(vcount),

.pixel(middle 3));

wire [23:0] bottom 3; reg display 21;

blob #(.WIDTH(44), .HEIGHT(10)) s_36(.clk(vclock), .display(display_21),

.color(24'hff ff ff), x(x7 + 60 + 65), y(y7 + 78), .hcount(hcount), .vcount(vcount),

.pixel(bottom 3));

wire [23:0] top left 4; reg display 22;

blob #(.WIDTH(10), .HEIGHT(44)) s_40(.clk(vclock),.display(display_22),

. \verb|color| (24'hff_ff_ff_ff)|, .x(x8+60+65)|, .y(y8+78)|, .hcount(hcount)|, .vcount(vcount)|, .hcount(hcount)|, .hcoun

.pixel(top left 4));

wire [23:0] top_4; reg display_23;

blob #(.WIDTH(44), .HEIGHT(10)) s_41(.clk(vclock),.display(display_23),

. \verb|color|(24'hFF_FF_FF|), .x(x9 + 60 + 65), .y(y9 + 78), .hcount(hcount), .vcount(vcount), \\

.pixel(top 4));

wire [23:0] top right 4; reg display 24;

blob #(.WIDTH(10), .HEIGHT(44)) s 42(.clk(vclock),.display(display 24),

.color(24'hFF FF FF), .x(x10 + 60 + 65), .y(y10 + 78), .hcount(hcount), .vcount(vcount),

.pixel(top right 4));

wire [23:0] bottom left 4; reg display 25;

blob #(.WIDTH(10), .HEIGHT(44)) s 43(.clk(vclock),.display(display 25),

.color(24'hFF FF FF), .x(x11 + 60 + 65), .y(y11 + 78), .hcount(hcount), .vcount(vcount),

.pixel(bottom left 4));

wire [23:0] bottom_right_4; reg display 26;

blob #(.WIDTH(10), .HEIGHT(54)) s 44(.clk(vclock),.display(display 26),

.color(24'hFF FF FF), .x(x12 + 60 + 65), .y(y12 + 78), .hcount(hcount), .vcount(vcount),

.pixel(bottom right 4));

wire [23:0] middle_4; reg display_27;

blob #(.WIDTH(44), .HEIGHT(10)) s_45(.clk(vclock), .display(display_27),

. \verb|color|(24'hFF_FF_FF|), ... (x13 + 60 + 65), ... (y13 + 78), ... (hcount(hcount), ... vcount(vcount), ... (x13 + 60 + 65), ... (y13 + 78), ... (hcount(hcount), ... (hcount), ... (hcount(hcount), ... (hcount(hcount)

.pixel(middle 4));

wire [23:0] bottom_4; reg display_28;

blob #(.WIDTH(44), .HEIGHT(10)) s_46(.clk(vclock), .display(display_28),

.color(24'hFF FF FF), .x(x14 + 60 + 65), .y(y14 + 78), .hcount(hcount), .vcount(vcount),

.pixel(bottom 4));

reg [7:0] scoreboard; reg [7:0] hiscore;

reg [7:0] subtractor; reg [7:0] subtractorhi;

wire [23:0] score; wire [23:0] highestscore;

assign score = top left 1 | top 1 | top right 1 | bottom left 1 | bottom right 1 |

middle 1 | bottom 1 |top left 2 | top 2 | top right 2 | bottom left 2 | bottom right 2 |

middle 2 | bottom 2;

assign highestscore = top left 3 | top 3 | top right 3 | bottom left 3 | bottom right 3 |

middle 3 | bottom 3 | top left 4 | top 4 | top right 4 | bottom left 4 | bottom right 4 |

middle 4 | bottom 4;

assign end pixel = score pixel | score | replay pixel | high score pixel | highestscore;

wire play overlap = cursor x > 424 && cursor x < 589 && cursor y > 400 && cursor y < 442;

wire replay overlap = cursor x > 297 && cursor x < 718 && cursor y > 244 && cursor y <

314;

// Game State Machine

reg old up; reg oldresetbutton;

```

```

32

always @(posedge vclock) begin

hiscore <= highscore;

scoreboard <= ultimate score;</pre>

if (scoreboard < 10) subtractor <= 0; else if (scoreboard >= 10 && scoreboard <

20)

subtractor <= 10;

else if (scoreboard >= 20 && scoreboard < 30) subtractor <= 20;

else if (scoreboard >= 30 && scoreboard < 40) subtractor <= 30;

else if (scoreboard >= 40 && scoreboard < 50) subtractor <= 40;

else if (scoreboard >= 50 && scoreboard < 60) subtractor <= 50;

else if (scoreboard >= 60 && scoreboard < 70) subtractor <= 60;

else if (scoreboard >= 70 && scoreboard < 80) subtractor <= 70;

else if (scoreboard >= 80 && scoreboard < 90) subtractor <= 80;

else if (scoreboard >= 90 && scoreboard < 150) subtractor <= 90;

case (scoreboard - subtractor)

0: begin display 6 <= 0; display 1 <= 1; display 2 <= 1; display 3 <= 1; display 4

<= 1; display 5 <= 1; display 7 <= 1; end

1: begin display 6 <= 0; display 1 <= 0; display 2 <= 0; display 3 <= 1; display 4

<= 0; display 5 <= 1; display 7 <= 0; end

2: begin display 6 <= 1; display 1 <= 0; display 2 <= 1; display 3 <= 1; display 4

<= 1; display 5 <= 0; display 7 <= 1; end

3: begin display 6 <= 1; display 1 <= 0; display 2 <= 1; display 3 <= 1; display 4

<= 0; display_5 <= 1; display_7 <= 1; end

4: begin display 6 <= 1; display 1 <= 1; display 2 <= 0; display 3 <= 1; display 4

<= 0; display 5 <= 1; display 7 <= 0; end

5: begin display 6 <= 1; display 1 <= 1; display 2 <= 1; display 3 <= 0; display 4

<= 0; display 5 <= 1; display 7 <= 1; end

6: begin display_6 <= 1; display_1 <= 1; display_2 <= 1; display_3 <= 0; display_4

<= 1; display 5 <= 1; display 7 <= 1; end

7: begin display 6 <= 0; display 1 <= 1; display 2 <= 1; display 3 <= 1; display 4

<= 0; display_5 <= 1; display_7 <= 0; end

8: begin display 6 <= 1; display 1 <= 1; display 2 <= 1; display 3 <= 1; display 4

<= 1; display 5 <= 1; display 7 <= 1; end

9: begin display_6 <= 1; display_1 <= 1; display_2 <= 1; display_3 <= 1; display_4

<= 0; display_5 <= 1; display_7 <= 0; end

default: begin display 6 \le 1; display 1 \le 1; display 2 \le 1; display 3 \le 1;

display 4 <= 0; display 5 <= 1; display 7 <= 0; end

endcase

if(scoreboard < 10) begin

display 13 <= 0; display 8 <= 1; display 9 <= 1; display 10 <= 1; display 11 <= 1;

display 12 <= 1; display 14 <= 1; end

else if (scoreboard >= 10 && scoreboard < 20) begin display 13 <= 0;

display 8 <= 0; display 9 <= 0; display 10 <= 1; display 11 <= 0; display 12 <= 1;

display 14 <= 0; end

else if (scoreboard \geq 20 && scoreboard < 30) begin display 13 < 1; display 8 <

0; display 9 <= 1; display 10 <= 1; display 11 <= 1; display 12 <= 0; display 14 <= 1; end

else if (scoreboard >= 30 && scoreboard < 40) begin display 13 <= 1; display 8 <=

0; display 9 <= 1; display 10 <= 1; display 11 <= 0; display 12 <= 1; display 14 <= 1; end

1; display 9 <= 0; display 10 <= 1; display 11 <= 0; display 12 <= 1; display 14 <= 0; end

else if (scoreboard >= 50 && scoreboard < 60) begin display 13 <= 1; display 8 <=

1; display_9 \le 1; display_{10} \le 0; display_{11} \le 0; display_{12} \le 1; display_{14} \le 1; end

else if (scoreboard >= 60 && scoreboard < 70)begin display_13 <= 1; display_8 <=

1; display_9 \le 1; display_{10} \le 0; display_{11} \le 1; display_{12} \le 1; display_{14} \le 1; end

```

else if (scoreboard  $\geq$  70 && scoreboard < 80) begin display 13 < 0; display 8 <1;  $display_9 \le 1$ ;  $display_{10} \le 1$ ;  $display_{11} \le 0$ ;  $display_{12} \le 1$ ;  $display_{14} \le 0$ ; end

```

else if (scoreboard >= 80 && scoreboard < 90) begin display 13 <= 1; display 8 <=

1; display_9 \le 1; display_{10} \le 1; display_{11} \le 1; display_{12} \le 1; display_{14} \le 1; end

else if (scoreboard >= 90 && scoreboard < 150) begin display 13 <= 1; display 8 <=

1; display 9 <= 1; display 10 <= 1; display 11 <= 0; display 12 <= 1; display 14 <= 0; end

if (hiscore < 10) subtractorhi <= 0; else if (hiscore >= 10 && hiscore < 20)

subtractorhi <= 10; else if (hiscore>= 20 && hiscore < 30) subtractorhi <= 20;

else if (hiscore >= 30 && hiscore < 40) subtractorhi <= 30; else if (hiscore >= 40

&& hiscore < 50) subtractorhi <= 40;

else if (hiscore >= 50 && hiscore < 60) subtractorhi <= 50; else if (hiscore >= 60

&& hiscore < 70) subtractorhi <= 60;

else if (hiscore >= 70 \&\& hiscore < 80) subtractorhi <= 70; else if (hiscore >= 80

&& hiscore < 90) subtractorhi <= 80;

else if (hiscore >= 90 && hiscore < 150) subtractorhi <= 90;

case (hiscore - subtractorhi)

0: begin display_20 <= 0; display_15 <= 1; display_16 <= 1; display_17 <=

1; display 18 <= 1; display 19 <= 1; display 21 <= 1; end

1: begin display 20 <= 0; display 15 <= 0; display 16 <= 0; display 17 <=

1; display 18 <= 0; display 19 <= 1; display 21 <= 0; end

2: begin display 20 <= 1; display 15 <= 0; display 16 <= 1; display 17 <=

1; display 18 <= 1; display 19<= 0; display 21 <= 1; end

3: begin display 20 <= 1; display 15 <= 0; display 16 <= 1; display 17 <=

1; display 18 <= 0; display 19 <= 1; display 21 <= 1; end

4: begin display_20 <= 1; display_15 <= 1; display_16 <= 0; display_17 <=

1; display_18 <= 0; display_19 <= 1; display_21 <= 0; end

5: begin display_20 <= 1; display_15 <= 1; display_16 <= 1; display_17 <=

0; display 18 <= 0; display 19 <= 1; display 21 <= 1; end

6: begin display 20 <= 1; display 15 <= 1; display 16 <= 1; display 17 <=

0; display_18 <= 1; display_19 <= 1; display_21 <= 1; end

7: begin display_20 <= 0; display_15 <= 1; display_16 <= 1; display_17 <=

1; display 18 <= 0; display 19 <= 1; display 21 <= 0; end

8: begin display_20 <= 1; display_15 <= 1; display_16 <= 1; display_17 <=

1; display_18 <= 1; display_19 <= 1; display_21 <= 1; end

9: begin display_20 <= 1; display_15 <= 1; display_16 <= 1; display_17 <=

1; display 18 <= 0; display 19 <= 1; display 21<= 0; end

default: begin display_20 <= 1; display_15 <= 1; display_16 <= 1;</pre>

display_17 <= 1; display_18 <= 0; display_19 <= 1; display_21 <= 0; end</pre>

endcase

if(hiscore < 10) begin display 27 \le 0; display 22 \le 1; display 23 \le 1;

display 24 <= 1; display 25 <= 1; display 26 <= 1; display 28 <= 1; end

else if (hiscore >= 10 && hiscore < 20) begin display 27 <= 0; display 22 <= 0;

display 23 <= 0; display 24 <= 1; display 25 <= 0; display 26 <= 1; display 28 <= 0; end

else if (hiscore >= 20 && hiscore < 30) begin display 27 <= 1; display 22 <= 0;

display 23 <= 1; display 24 <= 1; display 25 <= 1; display 26 <= 0; display 28 <= 1; end

else if (hiscore \geq 30 && hiscore < 40) begin display 27 <= 1; display 22 <= 0;

display 23 <= 1; display 24 <= 1; display 25 <= 0; display 26 <= 1; display 28 <= 1; end

else if (hiscore >= 40 && hiscore < 50) begin display 27 <= 1; display 22 <= 1;

display_23 <= 0; display_24 <= 1; display_25 <= 0; display_26 <= 1; display_28 <= 0; end

else if (hiscore >= 50 && hiscore < 60) begin display 27 <= 1; display 22 <= 1;

display 23 <= 1; display 24 <= 0; display 25 <= 0; display 26 <= 1; display 28 <= 1; end

else if (hiscore>= 60 && hiscore < 70)begin display_27 <= 1; display_22 <= 1;

display_23 <= 1; display_24 <= 0; display_25 <= 1; display_26 <= 1; display_28 <= 1; end

else if (hiscore \geq 70 && hiscore < 80) begin display_27 < 0; display_22 < 1;

\verb|display_23| <= 1; \verb|display_24| <= 1; \verb|display_25| <= 0; \verb|display_26| <= 1; \verb|display_28| <= 0; \verb|end| = 0; \verb|display_26| <= 1; \verb|display_28| <= 0; \verb|end| = 0; \verb|display_28| <= 0;

else if (hiscore >= 80 && hiscore < 90) begin display_27 <= 1; display_22 <= 1;

display_23 <= 1; display_24 <= 1; display_25 <= 1; display_26 <= 1; display_28 <= 1; end

else if (hiscore \geq 90 && hiscore < 150) begin display 27 < 1; display 22 < 1;

```

display\_23 <= 1; display\_24 <= 1; display\_25 <= 0; display\_26 <= 1; display\_28 <= 0; end

```

old up <= button[0];

oldresetbutton <= resetbutton;

case (state)

START: if (button[0] && ~old up && play overlap) begin

state <= PLAY;

display life3 <= 1;

display life2 <= 1;

display life1 <= 1;

end

else begin

state <= state;

ready <= 0;

end

PLAY: if (apple fell + orange fell + peach fell>= 3 || ((|cursor pixel &&

|bomb pixel) && active bomb)) begin

ready <= 0;

state <= GAME OVER; end

else if (resetbutton && ~oldresetbutton)

state <= START;

else begin

x1 <= 900; y1 <= 100; x2 <= 900; y2 <= 100; x3 <= 934; y3 <= 100; x4

<= 900; y4 <= 134; x5 <= 934; y5 <= 134; x6 <= 900; y6 <= 134; x7 <= 900; y7 <=

178;x8 <= 850; y8 <= 100; x9 <= 850; y9 <= 100; x10 <= 884; y10 <= 100; x11 <=

850; y11 <= 134; x12 <= 884; y12 <= 134; x13 <= 850; y13 <= 134; x14 <= 850; y14

<= 178;

case (apple fell + orange fell + peach fell)

0: begin display life3 <= 1; display life2 <= 1; display life1 <= 1; end

1: begin display_life3 <= 0; display_life2 <= 1; display_life1 <= 1; end

2: begin display life3 <= 0; display life2 <= 0; display life1 <= 1; end

3: begin display life3 <= 0; display life2 <= 0; display life1 <= 0; end

default : begin

display_life3 <= 1; display_life2 <= 1; display_life1 <= 1;</pre>

endcase

ready <= 1;

state <= state;</pre>

GAME OVER: if ((button[0] && ~old up && replay overlap)) begin

state <= PLAY;

end

else if (resetbutton && ~oldresetbutton) state <= START;

else begin

x1 <= 572; y1 <= 325; x2 <= 572; y2 <= 325; x3 <= 606; y3 <=

325; x4 <= 572; y4 <= 359; x5 <= 606; y5 <= 359; x6 <= 572; y6 <= 359; x7 <= 572; y7 <=

403; x8 <= 512; y8 <= 325; x9 <= 512; y9 <= 325; x10 <= 546; y10 <= 325; x11 <= 512; y11

<= 359; x12 <= 546; y12 <= 359; x13 <= 512; y13 <= 359; x14 <= 512; y14 <= 403;

state <= state;

ready \leq 0;

end

default: state <= START;</pre>

endcase

end

wire [23:0] fruit pixel;

wire bomb_first;

wire apple first;

wire peach first;

```

```

assign bomb first = ((|bomb pixel) && (|orange pixel)) || ((|bomb pixel) &&

(|apple pixel)) || ((|bomb pixel) && (|peach pixel));

assign apple first = (|apple pixel) && (|orange pixel) || (|apple pixel) &&

(|peach pixel);

assign peach first = (|peach pixel) && (|orange pixel);

assign fruit pixel = bomb first ? bomb pixel : apple first ? apple pixel : peach first?

peach pixel: apple pixel | orange pixel | bomb pixel | peach pixel;

assign game pixel = ((state == PLAY) ? fruit pixel | pixel lifel | pixel life2 |

pixel_life3 | cursor_pixel | score : (state == START) ? start_pixel | cursor pixel :

end pixel | cursor pixel);

assign overlap = ((|game pixel) && (|bg pixel));

assign pixel = overlap ? game pixel : bg pixel;

assign game_state = (state == GAME_OVER);

assign bomb slice = (|cursor pixel && |bomb pixel) && active bomb && (state == PLAY);

endmodule

Lookup Tables

module lookuptable (input clk, input [2:0] randomnumber,

output reg [4:0] yvel1, output reg backwards1, output reg [9:0] xcostart1);

always@(posedge clk) begin

case (randomnumber)

3'b00: begin yvel1 <= 16; xcostart1 <= 100; backwards1 <= 1; end