## DSPDude

Why

Re-programmable audio <u>Digital Signal Processor</u>

How

Valentina Chamorro & Yanni Coroneos

Demo

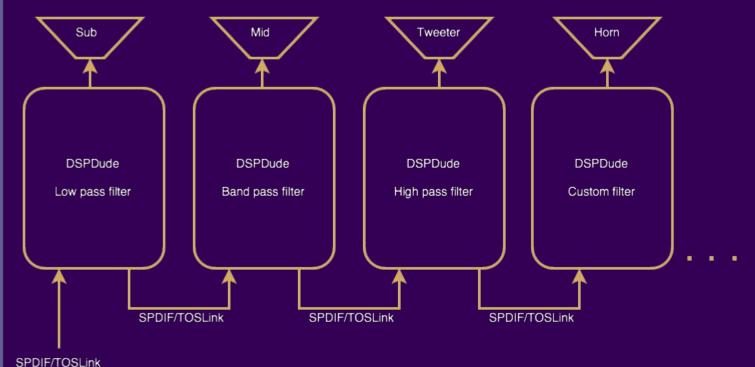

- daisy-chainable

- interchangeable filters via sdcard

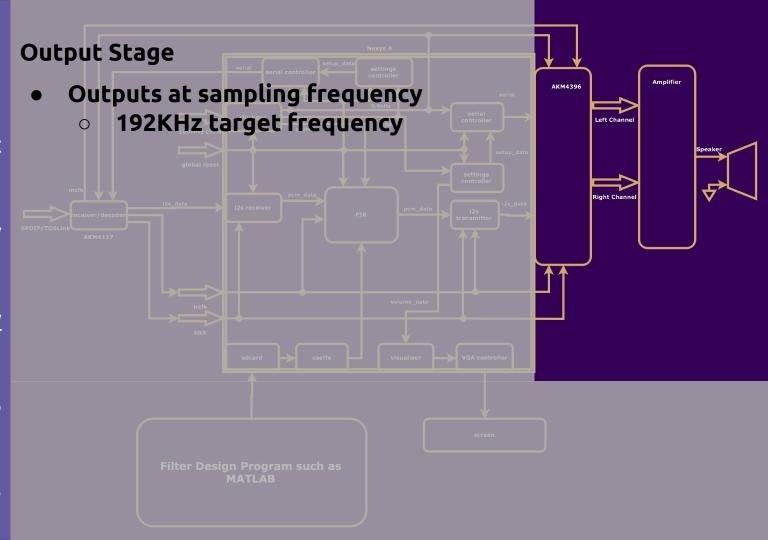

- high-quality 24bit, 192KHz, dual-channel output

- isolated communications over fiber-optic

<u>What</u>

Why

How

Demo

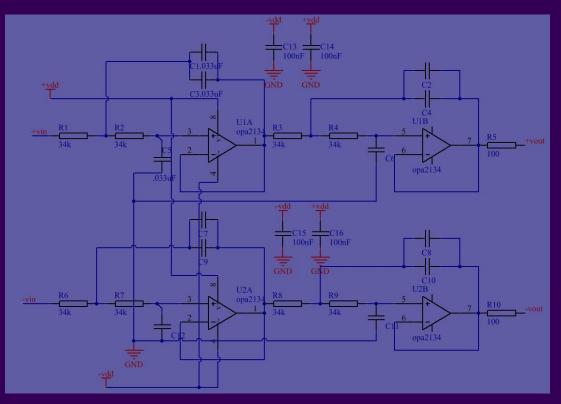

## Why Not Analog Filters?

- **Why**

- analog filters are not reconfigurable

All passives must be recalculated

- analog filters are big and expensive

- o Different circuit for every filter

- we can reasonably get higher order filters with an fpga

- Just need faster clock and more FIR coefficients <u>OR</u> more slices

How

Demo

### 4th Order Analog Filter

Good luck

What

Why

How

Demo

Why

<u>How</u>

Demo

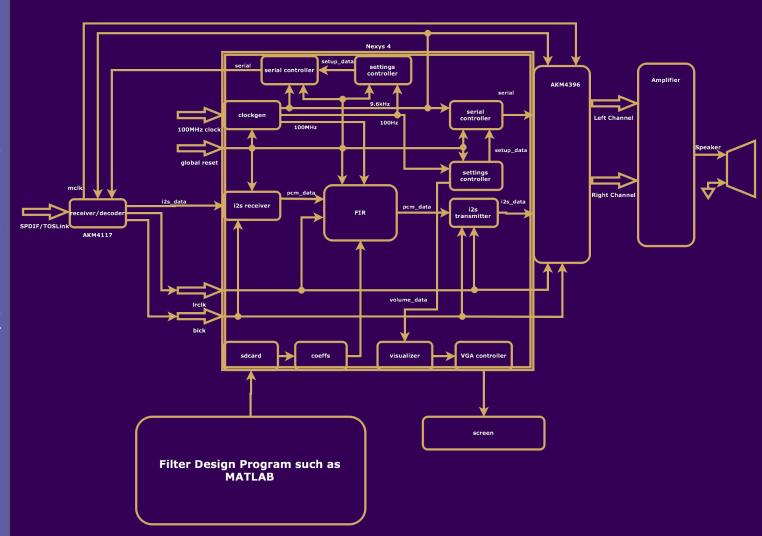

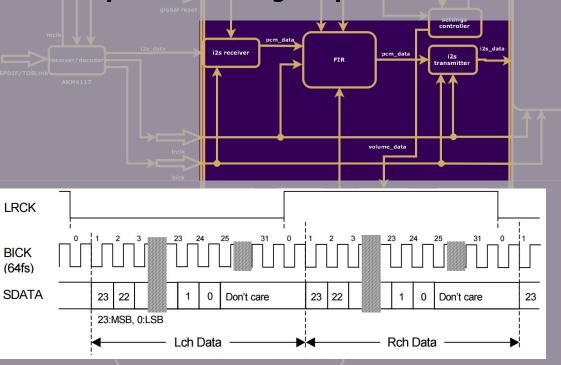

Input Stage SPDIF/TOSLink **AK4117 decodes SPDIF to i2s** What Clock Data AKM4117 1 0 0 1 1 0 1 0 0 Encoded (BMC) **LRCK BICK** (64fs) **SDATA** 23 22 0 Don't care 23 22 Don't care 23 23:MSB, 0:LSB Lch Data -Rch Data

Why

<u>How</u>

Demo

Why

<u>How</u>

Demo

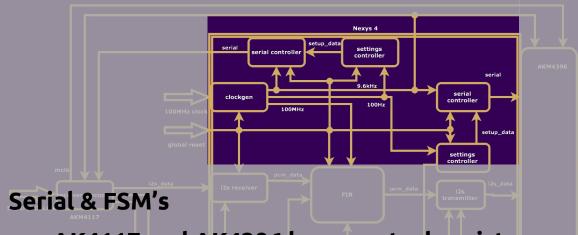

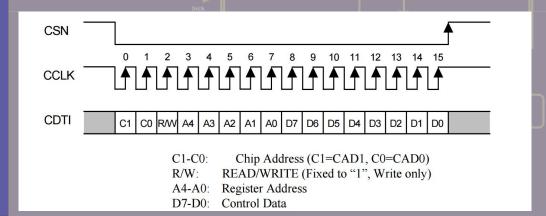

- AK4117 and AK4396 have control registers

- Programmed with 16bit SPI

#### i2s & FIR

- Output new 24bit sample every LRCLK cycle

100MHz/192KHz => 520 MAC's

- i2s tx/rx converts signed pcm ⇔ i2s

Why

What

<u>How</u>

Demo

**VGA Visualization** Settings controller for AK4396 sends volume data Visualize volume on VGA screen

What

Why

<u>How</u>

Demo

Why

<u>How</u>

Demo

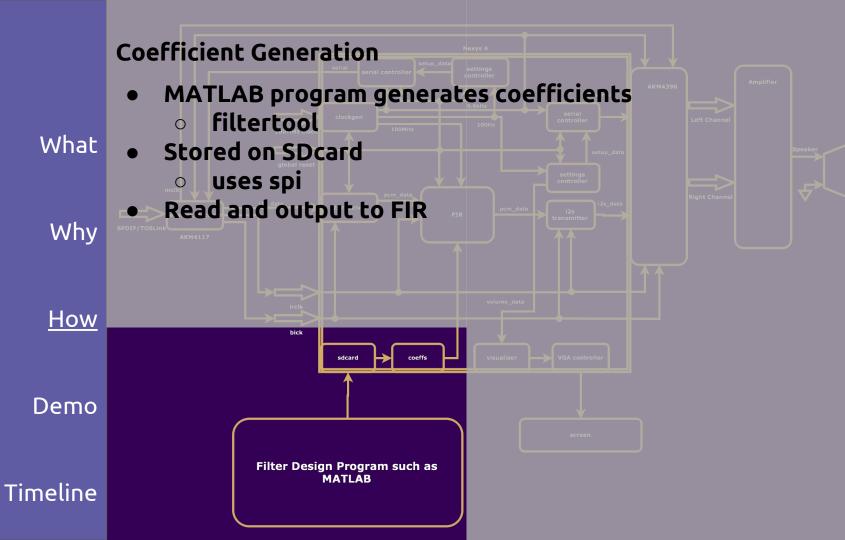

## Generating Coefficients

How to generate FIR coefficients in MATLAB

Why

What

How

<u>Demo</u>

## Timeline

What

Why

How

Demo

<u>Timeline</u>

|                                            |            |           |           | <u> </u>   |            |            |           |

|--------------------------------------------|------------|-----------|-----------|------------|------------|------------|-----------|

|                                            | 10/25/2015 | 11/1/2015 | 11/8/2015 | 11/15/2015 | 11/22/2015 | 11/29/2015 | 12/6/2015 |

| clock gen module                           |            |           |           |            |            |            |           |

| serial controller module                   |            |           |           |            |            |            |           |

| i2s transmitter module                     |            |           |           |            |            |            |           |

| settings controller module                 |            |           |           |            |            |            |           |

| codec outputs sound                        |            |           |           |            |            |            |           |

| generate fir coefficients                  |            |           |           |            |            |            |           |

| r/w coefficients to sdcard                 |            |           |           |            |            |            |           |

| i2s receiver module                        |            |           |           |            |            |            |           |

| fir module                                 |            |           |           |            |            |            |           |

| interface amplifier and speakers with fpga |            |           |           |            |            |            |           |

| volume control                             |            |           |           |            |            |            |           |

| vga controller module                      |            |           |           |            |            |            |           |

| check off                                  |            |           |           |            |            |            |           |

# Questions?