# Music Visualization with Audio Beat-Matching

Final Report Maggie Reagan and Liz Schell

#### **Table of Contents**

- 1. Introduction and Motivation

- 2. Implementation Overview

- 3. Audio Block Modules

- 3.1 Filterbank

- 3.2 AudioProcessingUnit

- 3.3 Peakpicker

- 3.4 Peakfinder

- 4. Audio Block Obstacles

- 4.1 Bugs and Fixes

- 4.2 Testing and Debugging Methods

- 5. Visual Block Modules

- 5.1 final\_project

- 5.2 graphics\_rotation

- 5.2.1 coordinate\_controller

- 5.2.2 rotation

- 5.2.3 translation

- 5.2.4 Obstacles with rotation

- 5.3 image\_init

- 5.3.1 moving\_circles

- 5.4 color\_shft

- 5.5 vram\_display

- 6. Final Product

Appendix A: Verilog Source code

#### 1. Introduction and Motivation

The goal for this project is to implement music visualization on a computer monitor using audio beat detection for real-time music playing. Most commercially available applications for this purpose are implemented in software, and are also limited in the visuals they provide. Hardware implementations that exist for this purpose are entirely custom and are even more visually limited; the most common music visualization is done with LED strips. This project would offer a hardware implementation for music beat detection and a more interesting and visually pleasing visualization than currently exists on the market.

We chose this project because we enjoy music and thought that it would be interesting to implement a colorful and unique visualization to go with our favorite music. In order for this project to be useful for a party or social event, we wanted to be able to process a song in real time or as close to real time as possible. We decided to go with an algorithm that takes a 2.2 second sample of a song to start generating the tempo and phase, to allow for beat detection as low as 60 bpm with some wiggle room. As new music samples come in, we will keep calculating the phase and tempo with the new data to keep up with changing tempos.

The development of the audio processing section of this project was done by Liz, and the development of the visualization section was done by Maggie. Therefore, the sections of this paper describing the design details and debugging process of these sections have been written by the person who worked on that section of the project.

# 2. Implementation Overview

Our project has two major parts: audio beat detection and visual generator. The beat detection is based on an algorithm described in a paper from the Media Lab ("Tempo and beat analysis of acoustic musical signals" by Eric D. Scheirer in 1997). It starts by smoothing the audio signal to make the beats stand out more and then convolving that with various comb filters to determine which tempo the music matches. The beat detection output will be used as an input to a visual display generator that will have several stages. The visual generator creates a series of expanding nested circles originating from the center and corners of the screen, that change in time with the beat of the song. The circles appear to expand until reaching the corners of the screen, at which they reappear in the center of the screen. The speed at which this expansion is performed is correlated with the tempo of the music.

# 3. Audio Block Implementation

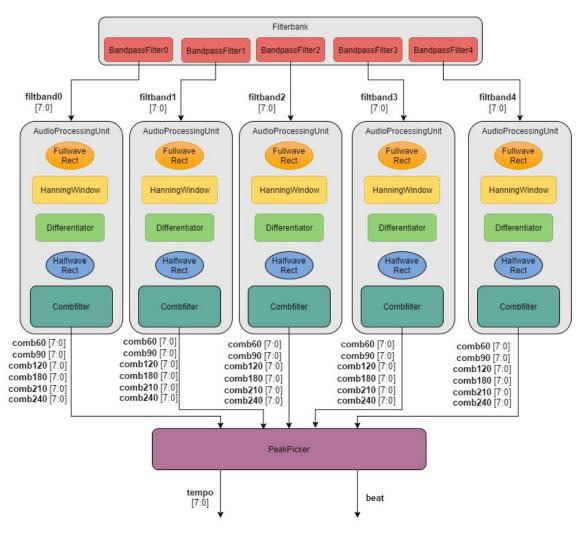

Figure 1: Audio Processing Block Diagram

The purpose of the audio block is to process the input audio and output the tempo and phase of the audio to the visual block. The frequency tells the visual block what the tempo of the music is, and the phase is represented by a signal "beat", which is high when the beat happens and low otherwise. This will allow the visualization to be synced up with the music. The full block diagram for the Audio Block is shown in Figure 1.

#### 3.1 Filterbank

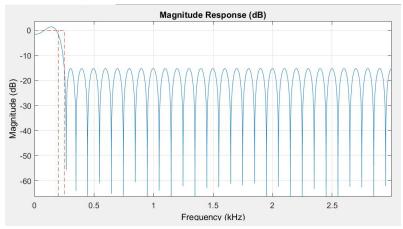

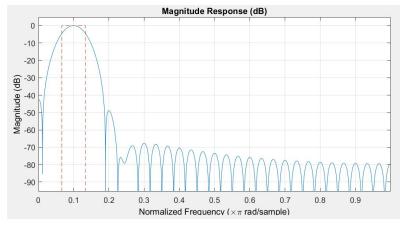

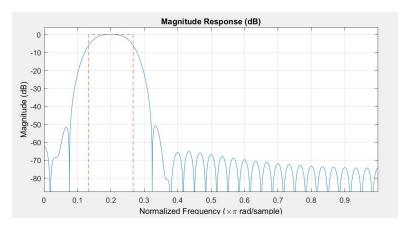

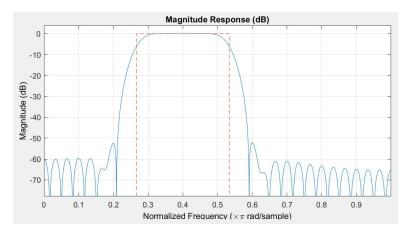

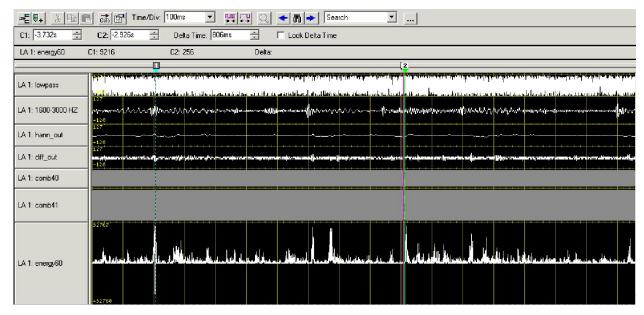

To achieve these goals, the audio input from the ac97 module is first low passed to 3000 Hz and then sampled at 6000 Hz. The low passed signal is shown in the first row of logic analyzer outputs in Figure 8. Next, this signal is split up into five different frequency bands (0-200,

200-400, 400-800, 800-1600, 1600-3200 Hz) by the frequency filterbank so that they can be processed separately. The frequency responses for each of these filters are shown in Figures 2-6. Each of these different bands is sent to its own audio processing unit. Figure 8 also shows the output from the highest frequency band, filtband4.

Figure 2: Frequency Response of 200 Hz Low Pass Filter

Figure 3: Frequency Response of 200-400 Hz Bandpass Filter

Figure 4: Frequency Response of 400-800 Hz Bandpass Filter

Figure 5: Frequency Response of 800-1600 Hz Bandpass Filter

Figure 6: Frequency Response of 1600-3200 Hz Bandpass Filter

#### 3.2 AudioProcessingUnit

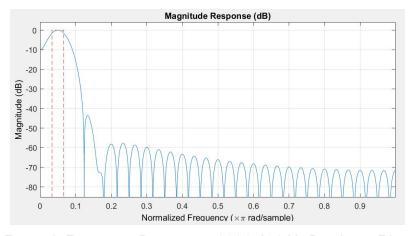

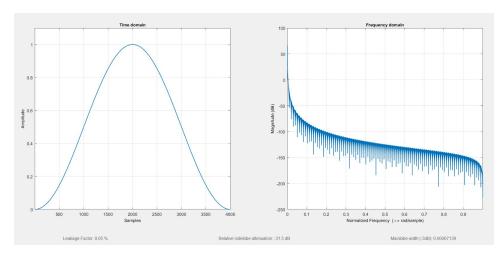

The audio processing unit contains an envelope extractor, a differentiator, a half-wave rectifier, and then a comb filter. The envelope extractor is implemented with a full-wave rectifier and then a Hann window, which low passes the signal to around 20 Hz. The Hann window that was used is shown in Figure 7. This window filter smooths the signal to accentuate the amplitude of the sound. The output of this Hann window for the filtband4 signal is shown as hann\_out in Figure 8. After the envelope is extracted, the signal is differentiated and passed through a half-wave rectifier. This isolates the large positive jumps in amplitude that tend to happen at the beats. The differentiated signal is shown as diff\_out in Figure 8. Once the audio has been processed to bring out the beats of the song, the comb filters act as resonators for different possible frequencies of the audio. This implementation tested the input audio for 60, 90, 120, 180, 210, and 240 bpm. With the sampling rate of 6000 Hz, this required impulses spaced by 6000, 4000, 3000, 2000, 1714, and 1500 samples, respectively. The comb filter is implemented with an instantiation of the bram module that stores the input at each sample. Between samples, it cycles through the different addresses that are needed to tap out the

correct samples for the different comb filters. The samples for a given frequency comb filter are summed and passed on to the peakpicker module.

Figure 7: Hann Window in Time and Frequency Domain

## 3.3 Peakpicker

The peakpicker module receives 30 different signals, which correspond to the six different tempo comb filter outputs for each of the five frequency bands. After the comb filters, the peakpicker module squares the comb filter outputs for a given tempo from all of the five frequency bands and adds those together to find the energy for a given sample at a given tempo. These byte energies are then summed over time to find the total energy of the song at 60 bpm or one of the other tempos. These different summed energies are compared to determine which tempo is the fundamental tempo of the audio. This will be the tempo whose comb filter outputs have the highest energy. The phase can be determined by looking at the energy of the individual samples that are coming in for the selected tempo. These single byte energies can be compared to a predetermined threshold to determine when the beats lined up with the comb filter. This will show when the beat happened with some phase lag between when the audio sample was taken in and when it arrived at this stage of the system.

Figure 8: Signals from different stages of the system

#### 3.4 Peakfinder

The Peakpicker module was not functional in time for the project check-off and demo. In order to make the project more functional, I decided to try a different approach at sending information from the Audio Block to the Visual Block. This module cannot determine the fundamental tempo of the song, however it can detect pulses of high energy in the song, which correlate with beats or high amplitudes of sound. This module calculates the byte energy in the same way as the Peakpicker, but depends on the fundamental tempo being input by the user. Given this input tempo, the Peakfinder can look at the byte energies coming from the comb filters of a given tempo, for example 120 bpm, and sets the beat signal high whenever this energy is above a certain threshold energy.

#### 4. Audio Block Obstacles

#### 4.1 Bugs and Fixes

One of the more difficult obstacles of this project was designing the filters. The filters suggested in the paper that this design is based on are sixth order elliptic filters. However, implementing FIR filters is easier, so I decided to try that. Initially, I tried making 31 tap FIR filters, and these filters didn't work for a number of reasons. One reason was that they didn't have enough taps to effectively filter the frequencies that I was trying to filter. The lowest filterband has a cutoff of 200 Hz, which is very small compared to the sampling rate of 6000 Hz. An FIR filter order of at least 60 is needed to filter frequencies this low. Unfortunately just increasing all of my bandpass filters to 61 tap didn't completely fix the problem. The signals appeared to be passing the correct frequencies. However, there was clipping, and the signals

looked like the peaks of the wave were transposed to the bottom of the signal. I discovered that the other problem was that I had forgotten to low pass my incoming audio at 3 kHz before sampling it at 6 kHz. This was introducing aliasing into the signals. This aliasing was fixed by including a 3 kHz low pass filter between the audio input from the ac97 and the one-eighth downsampling that happens as the signal is fed into the filterbank.

Similarly, when I first implemented the low pass Hann window, I also did not make it with enough coefficients. Since the purpose of the Hann window is to act as a low pass filter and find the envelope of the signal, it needs to have a cutoff frequency of around 10 Hz. In order to achieve this low of a cutoff frequency, the filter needs 4800 coefficients. Since the system samples at 6000 Hz and uses a 27 MHz clock, there are 4500 clock cycles between samples which limits the number of coefficients that the filter can have. I decided to use 4000 coefficients which low passed with a cutoff frequency of about 20 Hz. Once I started using filters with so many coefficients, it became impractical to write out the code for the case statement with over 4000 lines. Instead, I wrote a python script to read the coefficients from a file and format them into the case statement.

With these filters of higher orders, there are some considerations that need to be made. When we made the 31 tap FIR filter for lab 5, we had an 8 bit input and an 18 bit accumulator, because the coefficients were all scaled up by 2<sup>10</sup>. However, with more coefficients, it can become necessary to have a larger accumulator. Without this, the signals clip, because of overflow. It took me several tries to determine how wide the output of the Hann window needed to be in order to see as much of the wave as possible without clipping. I started by calculating the maximum number of bits that could be filled by multiplying the number of coefficients by the highest possible coefficient by the highest possible input. This proved to be much higher than any of the outputs, because many of the beginning and end coefficients are zero or numbers under ten and the maximum possible coefficient is 1024. I found the correct width for the accumulator by shifting the window of eight bits that were displayed on the logic analyzer until the signal's amplitude was as large as possible without clipping.

The comb filter module also presented many problems during development. I implemented the comb filter by convolving the signal over time with evenly spaced impulses. My first idea involved using a shift register to store the past samples so that they could be accessed again at the right time. I thought that this would be easier than using bram, because I wouldn't have to shift the address around to access the samples when I needed them. However, because over two seconds of audio are needed to get 3 impulses at 60 bpm, I needed an 8 bit wide shift register with 13200 registers. Unfortunately, Verilog doesn't allow partial declarations of 2D arrays, and so I couldn't easily assign the past 13199 bytes to the next registers with one line. Next, I tried to use a for loop to assign the byte samples one-by-one to their next registers. That attempt produced an error saying that iterations of greater than 10000 could not be performed. After this, I decided to change tactics and implement the comb filter with bram which introduced its own new set of bugs and difficulties.

I spent about four entire days debugging the comb filter module. During those four days, I found many potential bugs, but I kept getting the same results. All of my comb filters for a given frequency bands kept outputting the same exact signal. Eventually, I decided to change how I wrote to memory. Originally, I was assigning the input to memin and then just pulsing write enable when it was time to write the new input to memory. To fix the problem, I changed memin to a register instead of a wire and set memin to the input at the same time as I set write enable high. I still don't understand exactly why connecting the input to memin and pulsing write enable doesn't work, but I assume it must be a clocking issue where memin is unstable, because it's a wire instead of a reg.

## 4.1 Testing and Debugging Methods

During early development, I used simulations to in order to have a proof of concept and determine if my modules were working as expected. However, simulations rarely react the same way as implementation on the labkit. Almost all of the debugging was done with actual audio input on the labkit. I displayed the signals on the logic analyser as I stepped through the different stages of the audio block to determine that each module was reacting correctly. These tests were done at different volumes and with different songs in order to get a better understand of the capabilities of the system.

#### 5. Visual Block Modules

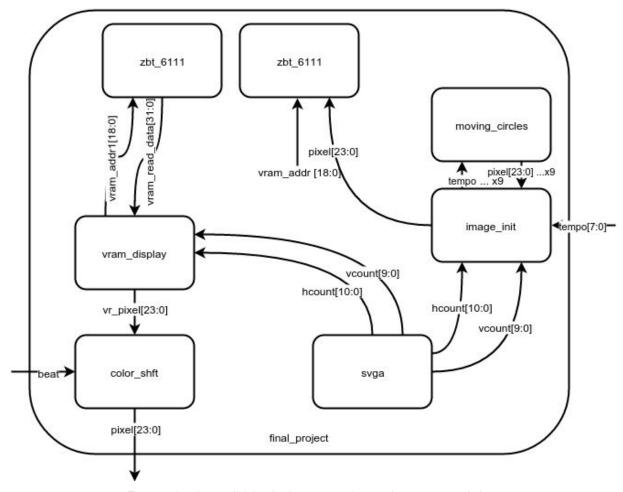

Figure 9 is an overall block diagram of the music visualization part of the project. All of the modules were clocked at a 40 MHz clock cycle generated by the ramclock module, a TA-provided module, which was necessary to use the ZBT memory banks.

Figure 9: Overall block diagram of visualization modules

# 5.1 final\_project

The top-level module of the project, final\_project, contained all of the other visual modules as well as the arbitration between the ZBT SRAM modules, and the connection between the beat detection aspect of the project and the visualization aspect of the project. The arbitration between the ZBTs was such that while the current ZBT was being displayed via the TA-supplied vram\_display module, the next ZBT was being written to with the next image to be displayed. The ZBT being displayed from would switch every vsync, or frame refresh, and the next image would be again written to the rendering ZBT which had been previously displayed. In the first form of our project, I had originally been connecting the data from the ZBTs together as well; that is, in addition to the read data of the current ZBT memory bank being displayed, it

was also being written to the rendering ZBT at a different location given by the graphics\_location module. This form of ZBT switching was successfully implemented; however, due to timing issues between the signals which will be explained further later on, this did not end up in the final form of our project.

In addition, the top-level module connected the music beat detection part of the project to the visualization part of the project. While connecting the tempo to the visualization blocks was easy, in that tempo was a continuous value output from the audio modules, the beat detection was less so due to the signals being clocked at different speeds. This was solved by a finite state machine which set two states, beat and reset, and switched to the beat state on the beat and only switched to reset state after the vsync had occurred. This was necessary due to the fact that we wanted to catch the beat signal before the frame updated, since they would not be in sync and we wanted to display a color change at the approximate beat time.

# **5.2** graphics\_rotation

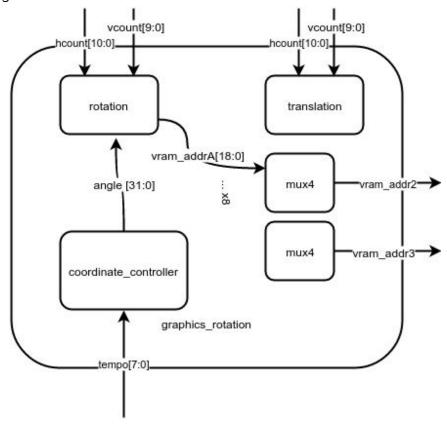

The final form of the project did not contain rotation as originally proposed due to several issues that will be explained in detail in this section. Still, a large amount of time was spent on writing and debugging this aspect of the project, and a switch on the labkit allows us to go into "rotation mode", so it merits an explanation. An overall block diagram for the graphics module is shown in Figure 10.

Figure 10: Rotation graphics block diagram.

The graphics\_rotation module takes in the current vcount and hount given by the syga module, and turns them into forecasted hoount and vocunt values to be given as x and y coordinates to be given to the rotation module. The rotation module computes the new rotated pixel x and y coordinates, x' and y'. This calculation takes 11 clock cycles, which is why the hount and vocunt must be turned into forecasted hount and vocunt values. These x and y outputs are then turned into an address for the pixel data from the non-rotated x and y coordinate to be written to. In creating this address for the rotated pixel data, I also create 6 other addresses which correspond to pixels surrounding the original pixel: the coordinates (x'-1, y'), (x'+1, y'), (x', y'-1), (x', y'+1), (x'+1, y'+1), (x'-1, y'-1). These addresses are split up and given to two four-input muxes, which select the correct address to output given the address count variable. In the original implementation of the project involving rotation, the ZBT ram was switched only every 4 vsync signals, making the frame rate 15 Hz, and allowing the rendering ZBT to be written over multiple times. In writing data to the rotated pixel location as well as the surrounding pixels over multiple syga cycles, I tried to ensure that the rounding issues caused by the fact that pixels cannot be floating point numbers, and that a rotation without floating point numbers would necessarily be inexact and pixels would get dropped, would be mitigated.

# 5.2.1 coordinate\_controller

The coordinate controller module takes in the tempo of the song and outputs the angle by which the image will be rotated. The tempo is mapped directly to an angle ranging from 1 degree to 16 degrees, not due to the lack of ability of the rotation algorithm to handle larger angles, but because if the image rotates by too large an angle the object will appear to "jump" to the new angle rather than move to the new angle.

#### 5.2.2. rotation

In this block, x and y values are given on a 0 to 800, or 0 to 600 scale according to the hount and vount they correspond to. First they are converted to values on a standard axis; that is, values from -400 to 400 and -300 to 300. This was necessary to create rotation about the center of the screen, rather than the top left corner, since the rotation occurs about the origin. Next, the converted x and y coordinates are rotated using the CORDIC rotation algorithm. This algorithm is an iterative algorithm, and basically calculates a rotation based on shifting and addition of x, y, and angle values. The equations for the algorithm are shown below:

$$x_{i+1} = x_i - y_i \cdot d_i \cdot 2^{-i}$$

$$y_{i+1} = y_i + x_i \cdot d_i \cdot 2^{-i}$$

$$z_{i+1} = z_i - d_i \cdot tan(2^{-i})$$

In this algorithm, z is initialized to the angle which you want to rotate by, and x and y are initialized to the non-rotated x and y coordinate values. For each iteration, d is given by the

sign of the current z value. The algorithm is iterated for the number of bits that can be stored for x and y. In my implementation, I implemented this inside of a generated for loop that incremented i once per clock cycle. The multiplication by  $2^{-i}$  can be implemented by a signed right shift by i, meaning that no actual multiplication is used during the iteration. The tangent values of  $2^{-i}$  were stored in a table within the module, as a 32 bit number, representing the rounded value of  $2^{32} \cdot \frac{tan(2^{-i})}{360}$ , to allow for the maximal amount of tangent data to be stored. The reason this module takes 11 clock cycles to complete is that the algorithm must iterate 11 times; this is the maximum size of signed x and y, so it doesn't make sense to calculate further than that. Once the rotated values are calculated, they must be divided by a gain of 1.647. Fortunately, the inverse of this is .6072, which can be approximated to .6074, or a multiplication by 311 and a right shift by 9 bits. The x and y rotated coordinates are then transformed back into positive values on the 0-800 and 0-600 scale, and given as the output.

This module worked well in testing; that is, in simulation when given an x, y value and an angle it would rotate to the correct x' and y' values. However, the actual use of this algorithm to rotate an entire image pixel by pixel did not work for reasons described in section 5.2.3.

# 5.2.3. translation

In the process of testing the integrated visual aspect of these modules, before I implemented the moving circles contingency plan, I discovered it was difficult to tell whether or not the rotating image was staying in the correct place on the screen, and whether or not switching between reading ZBTs was implemented correctly due to the timing issues in the rotation algorithm itself. Therefore the translation module was written to both allow for testing of the arbitration between ZBT modules, and testing of the timing for the vram\_display module. The translation module simply takes in an hount and a vocunt, and writes the data at that address to an address that has moved by some distance. Using this module, I was able to test whether or not writing data from the read data of one ZBT to another would work. I addition, I needed to forecast the hount and vocunt in the vram\_display module by some amount, since the ZBT takes two clock cycles to be read from. I was able to test whether the timing of this was correct by checking that the square blob did not move when I gave it a distance of zero to move; I knew then that I was forecasting the correct amount by hount and vocunt to be read from the ZBT, as if it was off slightly the read data given to the rendering ZBT would be off by some small number of pixels, causing the blob to appear to drift along the screen.

#### **5.2.4.** Obstacles with rotation

The original concept for our project involved rotating nested squares about the center of the screen. While I was able to come up with an image that would do this, the quality of the image was poor due to several reasons. One problem was inherent to the original design idea, and the other was a bug that I was unable to figure out after many hours and days in lab.

This first issue, the one inherent in the design, I had considered beforehand, but hadn't realized it would cause the extent of the issues it did. This was the fact that because I was implementing a rotation of every single pixel on the screen, and the rotation algorithm and Verilog does not allow for floating point pixel values, I would have to round to the nearest neighbor location of the pixel. What this did would cause most of the image to rotate, leaving some pixels behind where they were not overwritten by the background color, and causing pixels of the background color to bleed into the shape as they were not overwritten by the rotated image due to rounding. I knew the rounding would happen to some degree, causing the image to be slightly degraded over time; however, in the implementation I had working this degradation of the image happened extremely quickly, such that the image would not even make it halfway around the screen before disappearing or turning into a shapeless blob.

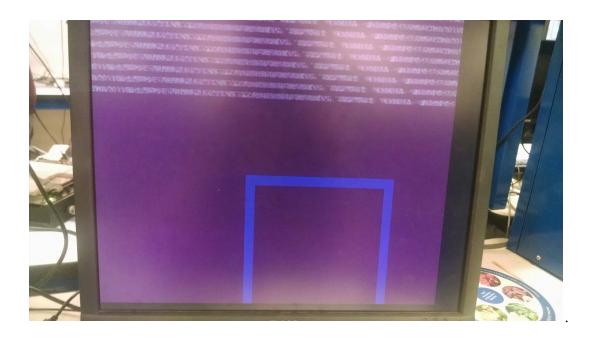

The next problem I had was one of timing. In writing the translation module, originally written to test the switching between ZBTs was working properly, I noticed that grey lines would appear on the top of the screen as the square blob test image moved down the screen. I figured the appearance of these lines had to be a timing issue somewhere which caused either the wrong pixels to be written to the ZBT or the wrong pixels to be read from the ZBT. After many hours of testing, I discovered the issue could be fixed by manipulating the forecasting of hcount and vcount in the vram\_display module; however, the same issue appeared the next day when I recompiled and ran my code. This was the source of much confusion and frustration; after several additional hours of testing I discovered that the timing of the vram\_display had changed between compiles, and that the best was to debug to proper timing constraints (i.e. the forecasting of hcount and vcount) I needed to set the travel distance of the square blob to zero and test different forecasting amounts until the image was able to remain stationary on the screen. Figure 11 below shows what this problem looked like when it occurred

Figure 11: Grey lines caused by timing problems

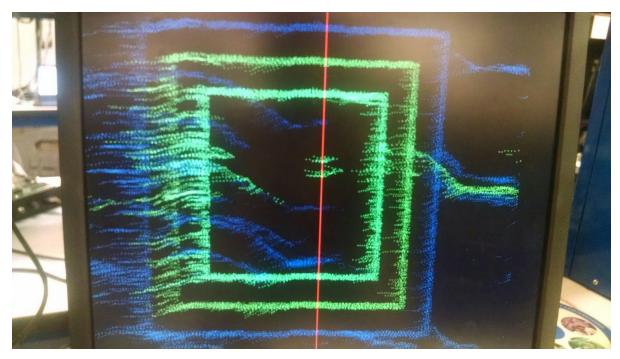

This same method was used in an attempt to debug the timing issues of the rotation module; I would set the angle of rotation to be zero, and adjust the forecasted vocunt and vocunt being sent to the rotation module accordingly until the actual image was stationary. One problem I discovered was that despite modifying both the values sent to the rotation block as well as the values to be displayed via the vram\_display module, I was unable to get the timing exactly right. Figure 12 shows another test image rotated an angle of zero via the rotation algorithm.

Figure 12: Image rotated by zero degrees with timing problems.

As you can see, the timing of the values given to the rotation module were very important; the image appears to be melting when it has incorrect timing. Unfortunately, this was not able to be resolved; changing the forecasting of both the vram\_display coordinates and the coordinates given to the rotation module did have an effect on the image, reducing the melting; however the melting never disappeared completely, and the image would only melt in the other direction (to the right as opposed to the left) when I overcorrected the forecasted hount and vocunt. If I had more time to work on the project, one thing I would like to do would be to discover the source of this issue. I took into account the 11 clock cycles it would take to rotate the x and y coordinate in the rotation module, as well as the time it took to read from the ZBT ram. Obviously there was some other timing problem or other issue in there that I was unable to discover, and would need to be accounted for if implementing my original idea for the visualization.

# 5.3 image\_init

After deciding that I would be unable to perform my original rotation idea to the extent that any image I rotated would be distorted due to the aforementioned issues, I decided instead to have expanding nested circles as my visualization image. This was implemented by initializing several moving\_circle modules in the center and in the corners of the screen; the next image would be loaded to the rendering ZBT by passing hount and vocunt directly through these modules and writing the subsequent pixel value to the ZBT, while the contents of the current ZBT was displayed.

# 5.3.1 moving\_circles

The moving\_circles module takes in an hount and vocunt and checks if the values was within a certain ring in the display, and if so colors that pixel in. The radius for the ring of values expands at every vsync, and is tied to the tempo produced by the audio part of this project, so that a faster tempo means the radius of the circle gets larger at every vsync than it does for a slower tempo.

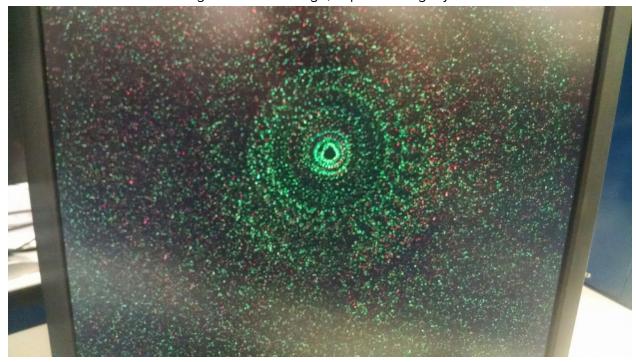

In addition, there is a delay for the circle expansion that can be set, so that I could initialize several of these circles to the same location-- the middle of the screen-- and have them start expanding at different times in order to create the nested circles effect. This was done because I wanted the circles to expand until they reached the edge of the screen, and then reappear in the same place in the center of the screen when the value for the radius overflowed. This image was successfully implemented, and the speed of the circle expansion was easily tied to the tempo value given to me by the audio block, and proportional so that a larger bpm meant a faster expansion. Figures 13-15 display the final image with the moving circles, as well as the "rotation mode."

Figure 13: Final image

Figure 14: Final image, expanded slightly

Figure 15: "Rotation mode"

# 5.4 color\_shft

The color shift is implemented on the pixel values coming from the current ZBT rather than the pixel values being saved in the rendering ZBT. The main input values for this module are the

pixel value and vsync, and the output is the shifted pixel value. In order to achieve a shifting effect that would have multiple shifts-- so that the color would not alternate between two but rather have multiple modes-- I implemented a counter that increments on a pulse signifying a beat given by the top-level module and multiplies each 8-bit reg, green, and blue pixel value by some value relating to this increment, such as the counter squared times three. In doing so, the red, green, and blue pixel values are changed by different amounts, leading to a more interesting color shift.

# 5.5 vram\_display

I used the provided vram\_display module in order to display images from the ZBT, with some modifications. The original module assumed four pixels were being stored in each address; in my implementation I only stored one, so needed to modify the code slightly in order to output just the one pixel every clock cycle. In addition, I forecasted the hount and vocunt values slightly differently due to the differences in my use and the original intended use of the module in relation to timing of other modules.

# **5.6 Testing and Debugging Methods**

While I ran what simulations i was able to on my modules, such as with the rotation module, often I found that testing using the display itself was more informative about the issues I was having; and, since I could not use an actual ZBT in simulation, it made more sense to debug the switching between ZBT rams first and then use the images I was generating for testing. I created the translation module originally as a test module, and it was very helpful for me to use for several issues I was having. For almost all of the visualization debugging, I used the display to try and figure out the problem as opposed to a simulation in ISE.

## **6. Final Product**

The final project we produced was able to listen to a song and detect significant beats in the song, in real time. Using this beat, the image was able to change color in time with the music, creating an interesting and colorful image that could match up with the music. While the tempo was unable to be determined in the audio aspect of the project, the image can change speeds from a series of switches on the FPGA. In addition, although the rotation was not able to be implemented correctly, one can still go into "rotation mode" by the first switch on the labkit. Though the rotation does not work as originally intended, it still does rotate a very distorted image, leading to a color-changing whirlpool-like image that is actually very interesting to look at.

# Appendix A: Verilog source code

```

`default_nettype none

//

// Switch Debounce Module

module debounce (

input wire reset, clock, noisy,

output reg clean

);

reg [18:0] count;

reg new;

always @(posedge clock)

if (reset) begin

count \leq 0;

new <= noisy;

clean <= noisy;</pre>

end

else if (noisy != new) begin

// noisy input changed, restart the .01 sec clock

new <= noisy;

count \leq 0;

end

else if (count == 270000)

// noisy input stable for .01 secs, pass it along!

clean <= new;

else

// waiting for .01 sec to pass

count <= count+1;

endmodule

// bi-directional monaural interface to AC97

module lab5audio (

input wire clock_27mhz,

input wire reset,

input wire [4:0] volume,

output wire [7:0] audio_in_data,

input wire [7:0] audio_out_data,

output wire ready,

```

```

output reg audio_reset_b, // ac97 interface signals

output wire ac97_sdata_out,

input wire ac97_sdata_in,

output wire ac97_synch,

input wire ac97_bit_clock

);

wire [7:0] command_address;

wire [15:0] command_data;

wire command_valid;

wire [19:0] left_in_data, right_in_data;

wire [19:0] left_out_data, right_out_data;

// wait a little before enabling the AC97 codec

reg [9:0] reset_count;

always @(posedge clock_27mhz) begin

if (reset) begin

audio_reset_b = 1'b0;

reset_count = 0;

end else if (reset_count == 1023)

audio_reset_b = 1'b1;

else

reset_count = reset_count+1;

end

wire ac97_ready;

ac97 ac97(.ready(ac97_ready),

.command_address(command_address),

.command_data(command_data),

.command_valid(command_valid),

.left_data(left_out_data), .left_valid(1'b1),

.right_data(right_out_data), .right_valid(1'b1),

.left_in_data(left_in_data), .right_in_data(right_in_data),

.ac97_sdata_out(ac97_sdata_out),

.ac97_sdata_in(ac97_sdata_in),

.ac97_synch(ac97_synch),

.ac97_bit_clock(ac97_bit_clock));

// ready: one cycle pulse synchronous with clock_27mhz

reg [2:0] ready_sync;

always @ (posedge clock_27mhz) ready_sync <= {ready_sync[1:0], ac97_ready};

assign ready = ready_sync[1] & "ready_sync[2];

reg [7:0] out_data;

always @ (posedge clock_27mhz)

if (ready) out_data <= audio_out_data;</pre>

assign audio_in_data = left_in_data[19:12];

assign left_out_data = {out_data, 12'b00000000000};

```

```

assign right_out_data = left_out_data;

// generate repeating sequence of read/writes to AC97 registers

ac97commands cmds(.clock(clock_27mhz), .ready(ready),

.command_address(command_address),

.command_data(command_data),

.command_valid(command_valid),

.volume(volume),

.source(3'b000)); // mic

endmodule

// assemble/disassemble AC97 serial frames

module ac97 (

output reg ready,

input wire [7:0] command_address,

input wire [15:0] command_data,

input wire command_valid,

input wire [19:0] left_data,

input wire left_valid,

input wire [19:0] right_data,

input wire right_valid,

output reg [19:0] left_in_data, right_in_data,

output reg ac97_sdata_out,

input wire ac97_sdata_in,

output reg ac97_synch,

input wire ac97_bit_clock

);

reg [7:0] bit_count;

reg [19:0] I_cmd_addr;

reg [19:0] I_cmd_data;

reg [19:0] l_left_data, l_right_data;

reg l_cmd_v, l_left_v, l_right_v;

initial begin

ready <= 1'b0;

// synthesis attribute init of ready is "0";

ac97_sdata_out <= 1'b0;

// synthesis attribute init of ac97_sdata_out is "0";

ac97\_synch \le 1'b0;

// synthesis attribute init of ac97_synch is "0";

bit_count <= 8'h00;

// synthesis attribute init of bit_count is "0000";

I_cmd_v \le 1'b0;

// synthesis attribute init of l_cmd_v is "0";

I_left_v <= 1'b0;

// synthesis attribute init of I_left_v is "0";

```

```

I_right_v \le 1'b0;

// synthesis attribute init of I_right_v is "0";

left_in_data <= 20'h00000;

// synthesis attribute init of left_in_data is "00000";

right_in_data <= 20'h00000;

// synthesis attribute init of right_in_data is "00000";

end

always @(posedge ac97_bit_clock) begin

// Generate the sync signal

if (bit_count == 255)

ac97_synch <= 1'b1;

if (bit_count == 15)

ac97_synch <= 1'b0;

// Generate the ready signal

if (bit_count == 128)

ready <= 1'b1;

if (bit_count == 2)

ready <= 1'b0;

// Latch user data at the end of each frame. This ensures that the

// first frame after reset will be empty.

if (bit_count == 255) begin

l_cmd_addr <= {command_address, 12'h000};</pre>

I_cmd_data <= {command_data, 4'h0};</pre>

l_cmd_v <= command_valid;</pre>

l_left_data <= left_data;</pre>

l_left_v <= left_valid;</pre>

l_right_data <= right_data;</pre>

l_right_v <= right_valid;</pre>

end

if ((bit_count >= 0) && (bit_count <= 15))

// Slot 0: Tags

case (bit_count[3:0])

4'h0: ac97_sdata_out <= 1'b1; // Frame valid

4'h1: ac97_sdata_out <= I_cmd_v; // Command address valid

4'h2: ac97_sdata_out <= I_cmd_v; // Command data valid

4'h3: ac97_sdata_out <= I_left_v; // Left data valid

4'h4: ac97_sdata_out <= I_right_v; // Right data valid

default: ac97_sdata_out <= 1'b0;</pre>

endcase

else if ((bit_count >= 16) && (bit_count <= 35))

// Slot 1: Command address (8-bits, left justified)

ac97_sdata_out <= I_cmd_v ? I_cmd_addr[35-bit_count] : 1'b0;

else if ((bit_count >= 36) && (bit_count <= 55))

```

```

// Slot 2: Command data (16-bits, left justified)

ac97_sdata_out <= I_cmd_v ? I_cmd_data[55-bit_count] : 1'b0;

else if ((bit_count >= 56) && (bit_count <= 75)) begin

// Slot 3: Left channel

ac97_sdata_out <= I_left_v ? I_left_data[19] : 1'b0;

I_left_data <= { I_left_data[18:0], I_left_data[19] };</pre>

else if ((bit_count >= 76) && (bit_count <= 95))

// Slot 4: Right channel

ac97_sdata_out <= I_right_v ? I_right_data[95-bit_count] : 1'b0;

else

ac97_sdata_out <= 1'b0;

bit_count <= bit_count+1;

end // always @ (posedge ac97_bit_clock)

always @(negedge ac97_bit_clock) begin

if ((bit_count >= 57) && (bit_count <= 76))

// Slot 3: Left channel

left_in_data <= { left_in_data[18:0], ac97_sdata_in };</pre>

else if ((bit_count >= 77) && (bit_count <= 96))

// Slot 4: Right channel

right_in_data <= { right_in_data[18:0], ac97_sdata_in };

end

endmodule

// issue initialization commands to AC97

module ac97commands (

input wire clock,

input wire ready,

output wire [7:0] command_address,

output wire [15:0] command_data,

output reg command_valid,

input wire [4:0] volume,

input wire [2:0] source

);

reg [23:0] command;

reg [3:0] state;

initial begin

command \leq 4'h0;

// synthesis attribute init of command is "0";

command_valid <= 1'b0;

// synthesis attribute init of command_valid is "0";

state <= 16'h0000;

// synthesis attribute init of state is "0000";

end

```

```

assign command_address = command[23:16];

assign command_data = command[15:0];

wire [4:0] vol;

assign vol = 31-volume; // convert to attenuation

always @(posedge clock) begin

if (ready) state <= state+1;</pre>

case (state)

4'h0: // Read ID

begin

command <= 24'h80_000;

command_valid <= 1'b1;

end

4'h1: // Read ID

command <= 24'h80_0000;

4'h3: // headphone volume

command <= { 8'h04, 3'b000, vol, 3'b000, vol };

4'h5: // PCM volume

command <= 24'h18_0808;

4'h6: // Record source select

command <= { 8'h1A, 5'b00000, source, 5'b00000, source};

4'h7: // Record gain = max

command <= 24'h1C_0F0F;

4'h9: // set +20db mic gain

command <= 24'h0E_8048;

4'hA: // Set beep volume

command <= 24'h0A_0000;

4'hB: // PCM out bypass mix1

command <= 24'h20_8000;

default:

command <= 24'h80_0000;

endcase // case(state)

end // always @ (posedge clock)

endmodule // ac97commands

////

//// 6.111 FPGA Labkit -- Template Toplevel Module

//// For Labkit Revision 004

//// Created: October 31, 2004, from revision 003 file

//// Author: Nathan Ickes, 6.111 staff

////

```

```

module final_project (beep, audio_reset_b, ac97_sdata_out, ac97_sdata_in, ac97_synch,

ac97_bit_clock,

vga_out_red, vga_out_green, vga_out_blue, vga_out_sync_b,

vga_out_blank_b, vga_out_pixel_clock, vga_out_hsync,

vga_out_vsync,

tv_out_ycrcb, tv_out_reset_b, tv_out_clock, tv_out_i2c_clock,

tv_out_i2c_data, tv_out_pal_ntsc, tv_out_hsync_b,

tv_out_vsync_b, tv_out_blank_b, tv_out_subcar_reset,

tv_in_ycrcb, tv_in_data_valid, tv_in_line_clock1,

tv_in_line_clock2, tv_in_aef, tv_in_hff, tv_in_aff,

tv_in_i2c_clock, tv_in_i2c_data, tv_in_fifo_read,

tv_in_fifo_clock, tv_in_iso, tv_in_reset_b, tv_in_clock,

ram0_data, ram0_address, ram0_adv_ld, ram0_clk, ram0_cen_b,

ram0_ce_b, ram0_oe_b, ram0_we_b, ram0_bwe_b,

ram1_data, ram1_address, ram1_adv_ld, ram1_clk, ram1_cen_b,

ram1_ce_b, ram1_oe_b, ram1_we_b, ram1_bwe_b,

clock_feedback_out, clock_feedback_in,

flash_data, flash_address, flash_ce_b, flash_oe_b, flash_we_b,

flash_reset_b, flash_sts, flash_byte_b,

rs232_txd, rs232_rxd, rs232_rts, rs232_cts,

mouse_clock, mouse_data, keyboard_clock, keyboard_data,

clock_27mhz, clock1, clock2,

disp_blank, disp_data_out, disp_clock, disp_rs, disp_ce_b,

disp_reset_b, disp_data_in,

button0, button1, button2, button3, button_enter, button_right,

button_left, button_down, button_up,

switch,

led.

user1, user2, user3, user4,

daughtercard,

```

```

systemace_data, systemace_address, systemace_ce_b,

systemace_we_b, systemace_oe_b, systemace_irq, systemace_mpbrdy,

analyzer1_data, analyzer1_clock,

analyzer2_data, analyzer2_clock,

analyzer3_data, analyzer3_clock,

analyzer4_data, analyzer4_clock);

output beep, audio_reset_b, ac97_synch, ac97_sdata_out;

input ac97_bit_clock, ac97_sdata_in;

output [7:0] vga_out_red, vga_out_green, vga_out_blue;

output vga_out_sync_b, vga_out_blank_b, vga_out_pixel_clock,

vga_out_hsync, vga_out_vsync;

output [9:0] tv_out_ycrcb;

output tv_out_reset_b, tv_out_clock, tv_out_i2c_clock, tv_out_i2c_data,

tv_out_pal_ntsc, tv_out_hsync_b, tv_out_vsync_b, tv_out_blank_b,

tv_out_subcar_reset;

input [19:0] tv_in_ycrcb;

input tv_in_data_valid, tv_in_line_clock1, tv_in_line_clock2, tv_in_aef,

tv_in_hff, tv_in_aff;

output tv_in_i2c_clock, tv_in_fifo_read, tv_in_fifo_clock, tv_in_iso,

tv_in_reset_b, tv_in_clock;

inout tv_in_i2c_data;

inout [35:0] ram0_data;

output [18:0] ram0_address;

output ram0_adv_ld, ram0_clk, ram0_cen_b, ram0_ce_b, ram0_oe_b, ram0_we_b;

output [3:0] ram0_bwe_b;

inout [35:0] ram1_data;

output [18:0] ram1_address;

output ram1_adv_ld, ram1_clk, ram1_cen_b, ram1_ce_b, ram1_oe_b, ram1_we_b;

output [3:0] ram1_bwe_b;

input clock_feedback_in;

output clock_feedback_out;

inout [15:0] flash_data;

output [23:0] flash_address;

output flash_ce_b, flash_oe_b, flash_we_b, flash_reset_b, flash_byte_b;

input flash_sts;

output rs232_txd, rs232_rts;

input rs232_rxd, rs232_cts;

```

```

input mouse_clock, mouse_data, keyboard_clock, keyboard_data;

input clock_27mhz, clock1, clock2;

output disp_blank, disp_clock, disp_rs, disp_ce_b, disp_reset_b;

input disp_data_in;

output disp_data_out;

input button0, button1, button2, button3, button_enter, button_right,

button_left, button_down, button_up;

input [7:0] switch;

output [7:0] led;

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

inout [15:0] systemace_data;

output [6:0] systemace_address;

output systemace_ce_b, systemace_we_b, systemace_oe_b;

input systemace_irq, systemace_mpbrdy;

output [15:0] analyzer1_data, analyzer2_data, analyzer3_data,

analyzer4_data;

output analyzer1_clock, analyzer2_clock, analyzer3_clock, analyzer4_clock;

// I/O Assignments

// Audio Input and Output

assign beep= 1'b0;

//lab5 assign audio_reset_b = 1'b0;

//lab5 assign ac97_synch = 1'b0;

//lab5 assign ac97_sdata_out = 1'b0;

// ac97_sdata_in is an input

// VGA Output

// assign vga_out_red = 10'h0;

// assign vga_out_green = 10'h0;

// assign vga_out_blue = 10'h0;

// assign vga_out_sync_b = 1'b1;

// assign vga_out_blank_b = 1'b1;

// assign vga_out_pixel_clock = 1'b0;

// assign vga_out_hsync = 1'b0;

```

```

// assign vga_out_vsync = 1'b0;

// Video Output

assign tv_out_ycrcb = 10'h0;

assign tv_out_reset_b = 1'b0;

assign tv_out_clock = 1'b0;

assign tv_out_i2c_clock = 1'b0;

assign tv_out_i2c_data = 1'b0;

assign tv_out_pal_ntsc = 1'b0;

assign tv_out_hsync_b = 1'b1;

assign tv_out_vsync_b = 1'b1;

assign tv_out_blank_b = 1'b1;

assign tv_out_subcar_reset = 1'b0;

// Video Input

assign tv_in_i2c_clock = 1'b0;

assign tv_in_fifo_read = 1'b0;

assign tv_in_fifo_clock = 1'b0;

assign tv_in_iso = 1'b0;

assign tv_in_reset_b = 1'b0;

assign tv_in_clock = 1'b0;

assign tv_in_i2c_data = 1'bZ;

// tv_in_ycrcb, tv_in_data_valid, tv_in_line_clock1, tv_in_line_clock2,

// tv_in_aef, tv_in_hff, and tv_in_aff are inputs

// SRAMs

/* enable RAM pins */

assign ram0\_ce\_b = 1'b0;

assign ram0_oe_b = 1'b0;

assign ram0_adv_ld = 1'b0;

assign ram0_bwe_b = 4'h0;

assign ram1_data = 36'hZ;

assign ram1_address = 19'h0;*/

assign ram1_adv_ld = 1'b0;

//assign ram1_clk = 1'b0;

//These values has to be set to 0 like ram0 if ram1 is used.

//assign ram1\_cen\_b = 1'b1;

assign ram1_ce_b = 1'b0;

assign ram1_oe_b = 1'b0;

//assign ram1_we_b = 1'b1;

assign ram1_bwe_b = 4'h0;

// assign ram0_data = 36'hZ;

// assign ram0_address = 19'h0;

// assign ram0_adv_ld = 1'b0;

```

```

// assign ram0_clk = 1'b0;

// assign ram0_cen_b = 1'b1;

// assign ram0_ce_b = 1'b1;

// assign ram0_oe_b = 1'b1;

// assign ram0_we_b = 1'b1;

// assign ram0_bwe_b = 4'hF;

// assign ram1_data = 36'hZ;

// assign ram1_address = 19'h0;

// assign ram1_adv_ld = 1'b0;

// assign ram1_clk = 1'b0;

// assign ram1_cen_b = 1'b1;

// assign ram1_ce_b = 1'b1;

// assign ram1_oe_b = 1'b1;

// assign ram1_we_b = 1'b1;

// assign ram1_bwe_b = 4'hF;

// assign clock_feedback_out = 1'b0;

// clock_feedback_in is an input

// Flash ROM

assign flash_data = 16'hZ;

assign flash_address = 24'h0;

assign flash_ce_b = 1'b1;

assign flash_oe_b = 1'b1;

assign flash_we_b = 1'b1;

assign flash_reset_b = 1'b0;

assign flash_byte_b = 1'b1;

// flash_sts is an input

// RS-232 Interface

assign rs232_txd = 1'b1;

assign rs232_rts = 1'b1;

// rs232_rxd and rs232_cts are inputs

// PS/2 Ports

// mouse_clock, mouse_data, keyboard_clock, and keyboard_data are inputs

// LED Displays

assign disp_blank = 1'b1;

assign disp_clock = 1'b0;

assign disp_rs = 1'b0;

assign disp_ce_b = 1'b1;

assign disp_reset_b = 1'b0;

assign disp_data_out = 1'b0;

// disp_data_in is an input

// Buttons, Switches, and Individual LEDs

assign led = 8'hFF;

// button0, button1, button2, button3, button_enter, button_right,

```

```

// button_left, button_down, button_up, and switches are inputs

// User I/Os

//assign user1 = 32'hZ;

assign user2 = 32'hZ;

assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace_data = 16'hZ;

assign systemace_address = 7'h0;

assign systemace_ce_b = 1'b1;

assign systemace_we_b = 1'b1;

assign systemace_oe_b = 1'b1;

// systemace_irq and systemace_mpbrdy are inputs

// Logic Analyzer

//lab5 assign analyzer1_data = 16'h0;

//lab5 assign analyzer1_clock = 1'b1;

//assign analyzer2_data = 16'h0;

//assign analyzer2_clock = 1'b1;

//lab5 assign analyzer3_data = 16'h0;

//lab5 assign analyzer3_clock = 1'b1;

// assign analyzer4_data = 16'h0;

assign analyzer4_clock = 1'b1;

// wire [7:0] from_ac97_data, to_ac97_data;

// wire ready;

// Reset Generation

// A shift register primitive is used to generate an active-high reset

// signal that remains high for 16 clock cycles after configuration finishes

// and the FPGA's internal clocks begin toggling.

//

wire reset;

SRL16 #(.INIT(16'hFFFF)) reset_sr(.D(1'b0), .CLK(clock_27mhz), .Q(reset),

.A0(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1));

wire hard_reset;

debounce

db_reset(.reset(reset),.clock(clock_27mhz),.noisy(button_enter),.clean(hard_reset));

```

```

wire [7:0] from_ac97_data, to_ac97_data;

wire ready;

wire [7:0]volume = 0;

// AC97 driver

lab5audio a(clock_27mhz, reset, volume, from_ac97_data, to_ac97_data, ready,

audio_reset_b, ac97_sdata_out, ac97_sdata_in,

ac97_synch, ac97_bit_clock);

// ZBT clock

wire clk;

wire clock_40mhz_unbuf,clock_40mhz;

DCM vclk1(.CLKIN(clock_27mhz),.CLKFX(clock_40mhz_unbuf));

// synthesis attribute CLKFX_DIVIDE of vclk1 is 2

// synthesis attribute CLKFX_MULTIPLY of vclk1 is 3

// synthesis attribute CLK_FEEDBACK of vclk1 is NONE

// synthesis attribute CLKIN_PERIOD of vclk1 is 37

BUFG vclk2(.O(clock_40mhz),.I(clock_40mhz_unbuf));

wire locked;

//assign clock_feedback_out = 0; // gph 2011-Nov-10

ramclock1 rc(.ref_clock(clock_40mhz), .fpga_clock(clk),

.ram0_clock(ram0_clk),

.ram1_clock(ram1_clk), //uncomment if ram1 is used

.clock_feedback_in(clock_feedback_in),

.clock_feedback_out(clock_feedback_out),

.locked(locked));

// Enter button reset

wire reset1,user_reset1;

// power-on reset generation

wire power_on_reset1; // remain high for first 16 clocks

SRL16 reset_sr1 (.D(1'b0), .CLK(clk), .Q(power_on_reset1),

.A0(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1));

defparam reset_sr.INIT = 16'hFFFF;

// ENTER button is user reset

debounce db1(power_on_reset1, clk, ~button_enter, user_reset1);

assign reset1 = user_reset1 | power_on_reset1;

///my code////

//declare connections

wire signed [17:0]lowpassed;

wire signed [7:0]filtband0;

```

```

wire signed [7:0]filtband2;

wire signed [7:0]filtband3;

wire signed [7:0]filtband4;

wire signed [7:0]filtband5;

wire signed [7:0]comb00;

wire signed [7:0]comb01;

wire signed [7:0]comb02;

wire signed [7:0]comb03;

wire signed [7:0]comb04;

wire signed [7:0]comb05;

wire signed [7:0]comb10;

wire signed [7:0]comb11;

wire signed [7:0]comb12;

wire signed [7:0]comb13;

wire signed [7:0]comb14;

wire signed [7:0]comb15;

wire signed [7:0]comb20;

wire signed [7:0]comb21;

wire signed [7:0]comb22;

wire signed [7:0]comb23;

wire signed [7:0]comb24;

wire signed [7:0]comb25;

wire signed [7:0]comb30;

wire signed [7:0]comb31;

wire signed [7:0]comb32;

wire signed [7:0]comb33;

wire signed [7:0]comb34;

wire signed [7:0]comb35;

wire signed [7:0]comb40;

wire signed [7:0]comb41;

wire signed [7:0]comb42;

wire signed [7:0]comb43;

wire signed [7:0]comb44;

wire signed [7:0]comb45;

wire [7:0]tempo;

wire beat;

wire sixk_ready;

wire signed [7:0]fw_rect_band0;

wire signed [7:0]hann_out0;

wire signed [7:0]diff_out0;

wire signed [7:0]hw_rect_band0;

wire signed [7:0]fw_rect_band1;

wire signed [7:0]hann_out1;

wire signed [7:0]diff_out1;

wire signed [7:0]hw_rect_band1;

wire signed [7:0]fw_rect_band2;

```

wire signed [7:0]filtband1;

```

wire signed [7:0]hann_out2;

wire signed [7:0]diff_out2;

wire signed [7:0]hw_rect_band2;

wire signed [7:0]fw_rect_band3;

wire signed [7:0]hann_out3;

wire signed [7:0]diff_out3;

wire signed [7:0]hw_rect_band3;

wire signed [7:0]fw_rect_band;

wire signed [7:0]hann_out;

wire signed [7:0]diff_out;

wire signed [7:0]hw_rect_band;

wire [15:0]eng60;

wire [15:0]eng90;

wire [15:0]eng120;

wire [15:0]eng180;

wire [15:0]eng210;

wire [15:0]eng240;

// output useful things to the logic analyzer connectors

assign analyzer3_clock = clock_27mhz;

assign analyzer3_data = {filtband0,hann_out};

assign analyzer1_clock = ready;

assign analyzer1_data = {diff_out,7'd0,beat};

//assign analyzer4_clock = sixk_ready;

assign analyzer4_data = {eng60};

assign analyzer2_clock = sixk_ready;

assign analyzer2_data = {eng120};

//lowpass audio by half of sampling frequency as it comes in

lowpass3k

LP(.clock(clock_27mhz),.reset(hard_reset),.ready(ready),.x(from_ac97_data),.y(lowpassed));

//sample audio input and split into frequency bands

Filterbank

fbank1(.clk(clock_27mhz),.reset(hard_reset),.ready(ready),.sixk_ready(sixk_ready),.x(lowpassed[1

7:10]),

.band0(filtband0),.band1(filtband1),.band2(filtband2),.band3(filtband3),.band4(filtband4));

//process audio in freq bands

AudioProcessingUnit

APU0(.clk(clock_27mhz),.reset(hard_reset),.ready(sixk_ready),.bandx(filtband0),

.comb60(comb00),.comb90(comb01),.comb120(comb02),.comb180(comb03),.comb210(comb04

),.comb240(comb05),

.hann_clip(hann_out0),.diff_out(diff_out0),.fw_rect_band(fw_rect_band0),.hw_rect_band(hw_re

ct_band0));

```

AudioProcessingUnit

APU1(.clk(clock\_27mhz),.reset(hard\_reset),.ready(sixk\_ready),.bandx(filtband1),

.comb60(comb10),.comb90(comb11),.comb120(comb12),.comb180(comb13),.comb210(comb14),.c omb240(comb15),

.hann\_clip(hann\_out1),.diff\_out(diff\_out1),.fw\_rect\_band(fw\_rect\_band1),.hw\_rect\_band(hw\_rect\_band1));

AudioProcessingUnit

APU2(.clk(clock\_27mhz),.reset(hard\_reset),.ready(sixk\_ready),.bandx(filtband2),

.comb60(comb20),.comb90(comb21),.comb120(comb22),.comb180(comb23),.comb210(comb24),.comb240(comb25),

.hann\_clip(hann\_out2),.diff\_out(diff\_out2),.fw\_rect\_band(fw\_rect\_band2),.hw\_rect\_band(hw\_rect\_band2));

AudioProcessingUnit

APU3(.clk(clock\_27mhz),.reset(hard\_reset),.ready(sixk\_ready),.bandx(filtband3),

.comb60(comb30),.comb90(comb31),.comb120(comb32),.comb180(comb33),.comb210(comb34),.comb240(comb35),

.hann\_clip(hann\_out3),.diff\_out(diff\_out3),.fw\_rect\_band(fw\_rect\_band3),.hw\_rect\_band(hw\_rect\_band3));

AudioProcessingUnit

APU4(.clk(clock\_27mhz),.reset(hard\_reset),.ready(sixk\_ready),.bandx(filtband4),

.comb60(comb40),.comb90(comb41),.comb120(comb42),.comb180(comb43),.comb210(comb44),.comb240(comb45),

.hann\_clip(hann\_out),.diff\_out(diff\_out),.fw\_rect\_band(fw\_rect\_band),.hw\_rect\_band(hw\_rect\_band));

// //find which tempo has highest energy Peakfinder peakfinder1(.clk(clock\_27mhz),.ready(sixk\_ready),.reset(hard\_reset),

.comb00(comb00),.comb01(comb01),.comb02(comb02),.comb03(comb03),.comb04(comb04),.comb05(comb05),

.comb10(comb10),.comb11(comb11),.comb12(comb12),.comb13(comb13),.comb14(comb14),.comb15 (comb15),

.comb20(comb20),.comb21(comb21),.comb22(comb22),.comb23(comb23),.comb24(comb24),.comb25(comb25),

.comb30(comb30),.comb31(comb31),.comb32(comb32),.comb33(comb33),.comb34(comb34),.comb35(comb35),

```

.comb40(comb40),.comb41(comb41),.comb42(comb42),.comb43(comb43),.comb44(comb44),.co

mb45(comb45),

.energy60(eng60),.energy90(eng90),.energy120(eng120),.energy180(eng180),

.energy210(eng210),.energy240(eng240),.tempo(tempo),.beat(beat));

// generate basic SVGA video signals

wire [10:0] hcount;

wire [9:0] vcount;

wire hsync,vsync,blank;

svga1 svga1(clk,hcount,vcount,hsync,vsync,blank);

// wire up to ZBT ram

wire [35:0] vram_write_data, vram_write_data_init, vram_write_data1;

wire [35:0] vram0_read_data, vram1_read_data, vram_read_data;

wire [18:0] vram_addr, vram0_addr, vram1_addr, vram_addr0, vram_addr3, vram_addr2;

wire

vram_we, vram0_we, vram1_we;

reg we_render;

reg currentram;

reg init;

reg [2:0] addr_count;

wire ram0_clk_not_used;

wire [31:0] angle;

wire [11:0] x_rot;

wire [10:0] y_rot;

wire [11:0] x_trans;

wire [10:0] y_trans;

wire [11:0] x_in;

wire [10:0] y_in;

// generate pixel value from reading ZBT memory

wire [23:0] vr_pixel;

wire [23:0]

circle_pixel;

wire [18:0] vram_addr1;

wire [23:0] pixel_out;

reg circle = 1;

wire [7:0] temp = switch[7:0];

wire [18:0] vram_addr_init = {hcount[10:0] + vcount[9:0]*800};

assign vram_addr0 = currentram ? vram_addr2 : vram_addr3;

wire [18:0] write_addr = circle ? vram_addr_init : vram_addr0;

```

```

assign vram0_addr = "init? vram_addr_init: (currentram? write_addr: vram_addr1);

assign vram0_we = currentram ? 1: we_render;

assign vram1_addr = ~currentram ? write_addr : vram_addr1;

assign vram1_we = currentram ? we_render : 1;

assign vram_read_data = currentram ? vram1_read_data : vram0_read_data;

assign vram_write_data1 = vram_read_data;

zbt_6111 zbt0(clk, 1'b1, vram0_we, vram0_addr,

vram_write_data, vram0_read_data,

ram0_clk_not_used, //to get good timing, don't connect ram_clk to zbt_6111

ram0_we_b, ram0_address, ram0_data, ram0_cen_b);

wire ram1_clk_not_used;

zbt_6111 zbt1(clk, 1'b1, vram1_we, vram1_addr,

vram_write_data, vram1_read_data,

ram1_clk_not_used, //to get good timing, don't connect ram_clk to zbt_6111

ram1_we_b, ram1_address, ram1_data, ram1_cen_b);

graphics_rotation g1(.clk(clk),.reset(reset1), .circle(circle),.addr_count(addr_count),

.hcount(hcount), .vcount(vcount),

.tempo(temp), .vram_addr2(vram_addr2), .vram_addr3(vram_addr3));

image_init im0(.clk(clk), .tempo(temp), .circle(circle),.hcount(hcount), .vcount(vcount),

.vsync(vsync),.pixel(circle_pixel));

assign vram_write_data = (circle ? circle_pixel : vram_write_data1);

vram_display1 vd1(reset1,clk, ~init, hcount,vcount,vr_pixel,

vram_addr1,vram_read_data);

always@(posedge clk) begin

we_render <= "init ? 1: 0;

end

req shift = 0;

color_shft color(.reset(reset1), .shft(shift), .vr(vr_pixel), .pixel(pixel_out));

reg beat_state;

parameter RESET = 0;

parameter BEAT = 1;

reg old_vsync;

```

```

reg vs_pulse;

always@(posedge clk) begin

old_vsync <= vsync;</pre>

vs_pulse <= !old_vsync && vsync;

case(beat_state)

RESET: if (beat) beat_state <= BEAT;

BEAT: if (vs_pulse) beat_state <= RESET;

endcase

end

reg [9:0] count= 0;

reg reset_circ = 0;

reg [8:0] max\_tempo = 300;

reg [9:0] col_count = 0;

always@(posedge vsync) begin

if (reset1 | (reset_circ != circle)) begin

init <= 0;

shift \le 0;

currentram <= 0;

addr_count <= 0;

reset_circ <= 0;

col_count <= 0; end

else begin

init <= 1;

currentram <= ~currentram;

if (count< temp) begin

count <= count + 1;

if (count == temp) begin

count \leq 0;

end

if (beat_state==BEAT) shift <= 1;</pre>

if (beat_state==RESET) shift <= 0;</pre>

addr_count <= addr_count+1;</pre>

end

circle <= switch[0] ? 1 : 0;

reset_circ <= circle;

end

reg b,hs,vs;

always @(posedge clk)

begin

```

```

b <= blank;

hs <= hsync;

vs <= vsync;

end

// VGA Output. In order to meet the setup and hold times of the

// AD7125, we send it ^{\sim}clk.

assign vga_out_red = pixel_out[23:16];

assign vga_out_green = pixel_out[15:8];

assign vga_out_blue = pixel_out[7:0];

assign vga_out_sync_b = 1'b1; // not used

assign vga_out_pixel_clock = "clk;

assign vga_out_blank_b = "b;

assign vga_out_hsync = hs;

assign vga_out_vsync = vs;

endmodule

module svga1(vclock,hcount,vcount,hsync,vsync,blank);

input vclock;

output [10:0] hcount;

output [9:0] vcount;

output

vsync;

output

hsync;

output

blank;

reg

hsync,vsync,hblank,vblank,blank;

reg [10:0]

hcount; // pixel number on current line

reg [9:0] vcount;

// line number

// horizontal: 1056 pixels total

// display 800 pixels per line

hsyncon,hsyncoff,hreset,hblankon;

assign hblankon = (hcount == 799);

assign hsyncon = (hcount == 839);

assign hsyncoff = (hcount == 967);

assign hreset = (hcount == 1055);

// vertical: 628 lines total

// display 600 lines

wire vsyncon, vsyncoff, vreset, vblankon;

assign vblankon = hreset & (vcount == 599);

assign vsyncon = hreset & (vcount == 600);

assign vsyncoff = hreset & (vcount == 604);

assign vreset = hreset & (vcount == 627);

// sync and blanking

```

```

wire

next_hblank,next_vblank;

assign next_hblank = hreset ? 0 : hblankon ? 1 : hblank;

assign next_vblank = vreset ? 0 : vblankon ? 1 : vblank;

always @(posedge vclock) begin

hcount <= hreset ? 0 : hcount + 1;

hblank <= next_hblank;

hsync <= hsyncon ? 0 : hsyncoff ? 1 : hsync; // active low

vcount <= hreset ? (vreset ? 0 : vcount + 1) : vcount;</pre>

vblank <= next_vblank;</pre>

vsync <= vsyncon ? 0 : vsyncoff ? 1 : vsync; // active low</pre>

blank <= next_vblank | (next_hblank & ~hreset);</pre>

end

endmodule

module vram_display1(reset,clk, init, hcount,vcount,vr_pixel,

vram_addr,vram_read_data);

input reset, clk;

input [10:0] hcount;

input [9:0] vcount;

input init;

output [23:0] vr_pixel;

output [18:0] vram_addr;

input [35:0] vram_read_data;

//forecast hcount & vcount 2 clock cycle ahead to get data from ZBT

wire [10:0] hcount_f = (hcount >= 1054) ? (hcount - 1054) : (hcount + 2);

wire [9:0] vcount_f = (hcount >= 1054) ? ((vcount == 627) ? 0 : vcount+1) : vcount;

wire [18:0]

vram_addr = {hcount_f[10:0] + vcount_f[9:0]*800};

hc4 = hcount[1:0];

wire [1:0]

reg [23:0]

vr_pixel;

vr_data_latched;

reg [35:0]

reg [35:0]

last_vr_data;

always @(posedge clk)

vr_pixel <= vram_read_data[23:0];</pre>

endmodule // vram_display

module ramclock1(ref_clock, fpga_clock, ram0_clock, ram1_clock,

clock_feedback_in, clock_feedback_out, locked);

input ref_clock;

// Reference clock input

```

```

output fpga_clock;

// Output clock to drive FPGA logic

output ram0_clock, ram1_clock; // Output clocks for each RAM chip

// Output to feedback trace

input clock_feedback_in;

output clock_feedback_out;

// Input from feedback trace

output locked;

// Indicates that clock outputs are stable

wire ref_clk, fpga_clk, ram_clk, fb_clk, lock1, lock2, dcm_reset, ram_clock;

//To force ISE to compile the ramclock, this line has to be removed.

//IBUFG ref_buf (.O(ref_clk), .l(ref_clock));

assign ref_clk = ref_clock;

BUFG int_buf (.O(fpga_clock), .l(fpga_clk));

DCM int_dcm (.CLKFB(fpga_clock),

.CLKIN(ref_clk),

.RST(dcm_reset),

.CLKO(fpga_clk),

.LOCKED(lock1));

// synthesis attribute DLL_FREQUENCY_MODE of int_dcm is "LOW"

// synthesis attribute DUTY_CYCLE_CORRECTION of int_dcm is "TRUE"

// synthesis attribute STARTUP_WAIT of int_dcm is "FALSE"

// synthesis attribute DFS_FREQUENCY_MODE of int_dcm is "LOW"

// synthesis attribute CLK_FEEDBACK of int_dcm is "1X"

// synthesis attribute CLKOUT_PHASE_SHIFT of int_dcm is "NONE"

// synthesis attribute PHASE_SHIFT of int_dcm is 0

BUFG ext_buf (.O(ram_clock), .I(ram_clk));

IBUFG fb_buf (.O(fb_clk), .l(clock_feedback_in));

DCM ext_dcm (.CLKFB(fb_clk),

.CLKIN(ref_clk),

.RST(dcm_reset),

.CLK0(ram_clk),

.LOCKED(lock2));

// synthesis attribute DLL_FREQUENCY_MODE of ext_dcm is "LOW"

// synthesis attribute DUTY_CYCLE_CORRECTION of ext_dcm is "TRUE"

// synthesis attribute STARTUP_WAIT of ext_dcm is "FALSE"

// synthesis attribute DFS_FREQUENCY_MODE of ext_dcm is "LOW"

// synthesis attribute CLK_FEEDBACK of ext_dcm is "1X"

// synthesis attribute CLKOUT_PHASE_SHIFT of ext_dcm is "NONE"

// synthesis attribute PHASE_SHIFT of ext_dcm is 0

SRL16 dcm_rst_sr (.D(1'b0), .CLK(ref_clk), .Q(dcm_reset),

```

```

.A0(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1));

// synthesis attribute init of dcm_rst_sr is "000F";

OFDDRRSE ddr_reg0 (.Q(ram0_clock), .C0(ram_clock), .C1(^ram_clock),

.CE (1'b1), .D0(1'b1), .D1(1'b0), .R(1'b0), .S(1'b0));

OFDDRRSE ddr_reg1 (.Q(ram1_clock), .C0(ram_clock), .C1(^ram_clock),

.CE (1'b1), .D0(1'b1), .D1(1'b0), .R(1'b0), .S(1'b0));

OFDDRRSE ddr_req2 (.Q(clock_feedback_out), .C0(ram_clock), .C1(~ram_clock),

.CE (1'b1), .D0(1'b1), .D1(1'b0), .R(1'b0), .S(1'b0));

assign locked = lock1 && lock2;

endmodule

//Audio Processing unit

module AudioProcessingUnit

(input clk, reset, ready,

input signed [7:0]bandx,

output signed [7:0]comb60,comb90,comb120,comb180,comb210,comb240,

output signed [7:0] hann_clip,diff_out,fw_rect_band,hw_rect_band);

//define signals

wire signed [27:0]hann_out;

//

wire signed [7:0]diff_out;

//

wire signed [7:0]fw_rect_band;

//

wire signed [7:0]hw_rect_band;

assign hann_clip = hann_out[21:14];

//full wave rectify to make positive

assign fw_rect_band = (bandx>0)?bandx:(-bandx);

//low pass filter to get envelope

hannfilter

HannWindow1(.clk(clk),.reset(reset),.ready(ready),.x(fw_rect_band),.y(hann_out));

//differentiate to find sudden jumps

Differentiator diff1(.clk(clk),.reset(reset),.ready(ready),.x(hann_clip),.y(diff_out));

//half wave rectify to only get positive jumps

assign hw_rect_band = (diff_out>0)?diff_out:(8'd0);

//comb signal for different tempos

CombFilter comb1(.clk(clk),.reset(reset),.ready(ready),.x(hw_rect_band),

.comb60(comb60),.comb90(comb90),.comb120(comb120),.comb180(comb180),.comb210(comb

210),.comb240(comb240));

endmodule

```

```

module band0coeffs(

input wire [5:0] index,

output reg signed [9:0] coeff

);

// lowpass 200 Hz

// tools will turn this into a 61x10 ROM

always @(index)

case (index)

5'd0: coeff = 10'sd84;

5'd1: coeff = -10'sd9;

5'd2: coeff = -10'sd10;

5'd3: coeff = -10'sd11;

5'd4: coeff = -10'sd12;

5'd5: coeff = -10'sd14;

5'd6: coeff = -10'sd16;

5'd7: coeff = -10'sd18:

5'd8: coeff = -10'sd19;

5'd9: coeff = -10'sd21;

5'd10: coeff = -10'sd21;

5'd11: coeff = -10'sd21;

5'd12: coeff = -10'sd20;

5'd13: coeff = -10'sd18;

5'd14: coeff = -10'sd15;

5'd15: coeff = -10'sd11;

5'd16: coeff = -10'sd6:

5'd17: coeff = 10'sd0;

5'd18: coeff = 10'sd6:

5'd19: coeff = 10'sd13;

5'd20: coeff = 10'sd21;

5'd21: coeff = 10'sd29;

5'd22: coeff = 10'sd37;

5'd23: coeff = 10'sd45;

5'd24: coeff = 10'sd52;

5'd25: coeff = 10'sd59;

5'd26: coeff = 10'sd65;

5'd27: coeff = 10'sd70;

5'd28: coeff = 10'sd73;

5'd29: coeff = 10'sd75;

5'd30: coeff = 10'sd76;

5'd31: coeff = 10'sd75;

5'd32: coeff = 10'sd73;

5'd33: coeff = 10'sd70;

5'd34: coeff = 10'sd65:

5'd35: coeff = 10'sd59;

5'd36: coeff = 10'sd52;

5'd37: coeff = 10'sd45;

5'd38: coeff = 10'sd37;

```

5'd39: coeff = 10'sd29;

```

5'd40: coeff = 10'sd21;

5'd41: coeff = 10'sd13;

5'd42: coeff = 10'sd6;

5'd43: coeff = 10'sd0;

5'd44: coeff = -10'sd6;

5'd45: coeff = -10'sd11;

5'd46: coeff = -10'sd15;

5'd47: coeff = -10'sd18;

5'd48: coeff = -10'sd20;

5'd49: coeff = -10'sd21;

5'd50: coeff = -10'sd21;

5'd51: coeff = -10'sd21;

5'd52: coeff = -10'sd19;

5'd53: coeff = -10'sd18;

5'd54: coeff = -10'sd16;

5'd55: coeff = -10'sd14;

5'd56: coeff = -10'sd12;

5'd57: coeff = -10'sd11;

5'd58: coeff = -10'sd10;

5'd59: coeff = -10'sd9;

5'd60: coeff = 10'sd84;

default: coeff = 10'hXXX;

endcase

endmodule

module band1coeffs(

input wire [5:0] index,

output reg signed [9:0] coeff

);

// bandpass 200 to 400 Hz

// tools will turn this into a 61x10 ROM

always @(index)

case (index)

5'd0: coeff = 10'sd0;

5'd1: coeff = -10'sd1;

5'd2: coeff = -10'sd1;

5'd3: coeff = -10'sd2;

5'd4: coeff = -10'sd3;

5'd5: coeff = -10'sd5;

5'd6: coeff = -10'sd7;

5'd7: coeff = -10'sd9;

5'd8: coeff = -10'sd12;

5'd9: coeff = -10'sd15;

5'd10: coeff = -10'sd17;

5'd11: coeff = -10'sd20;

5'd12: coeff = -10'sd22;

5'd13: coeff = -10'sd23;

```

```

5'd14: coeff = -10'sd24;

```

$$5'd15: coeff = -10'sd23;$$

$$5'd16: coeff = -10'sd21;$$

$$5'd18: coeff = -10'sd13;$$

$$5'd19: coeff = -10'sd7;$$

$$5'd21: coeff = 10'sd8;$$

$$5'd22: coeff = 10'sd17;$$

$$5'd31: coeff = 10'sd67;$$

$$5'd32: coeff = 10'sd63;$$

$$5'd34$$

: coeff =  $10'sd52$ ;

$$5'd35: coeff = 10'sd44;$$

$$5'd37: coeff = 10'sd26;$$

$$5'd38: coeff = 10'sd17;$$

$$5'd41: coeff = -10'sd7;$$

- 5'd43: coeff = -10'sd18;

- 5'd44: coeff = -10'sd21;

- 5'd45: coeff = -10'sd23;

- 5'd46: coeff = -10'sd24;

- 3 440. COEII 10 3424

- 5'd47: coeff = -10'sd23;

- 5'd48: coeff = -10'sd22;

- 5'd49: coeff = -10'sd20;

- 5'd50: coeff = -10'sd17;

- 5'd51: coeff = -10'sd15;

- 5'd52: coeff = -10'sd12;

- 5'd53: coeff = -10'sd9;

- 5'd54: coeff = -10'sd7;

- 5'd55: coeff = -10'sd5;

- 5'd56: coeff = -10'sd3;

- 5'd57: coeff = -10'sd2;

- 5'd58: coeff = -10'sd1;

- 5 450, 65 401 14

- 5'd59: coeff = -10'sd1; 5'd60: coeff = 10'sd0;

- default: coeff = 10'hXXX;

## endcase endmodule

```

module band2coeffs(

input wire [5:0] index,

output reg signed [9:0] coeff

);

// bandpass 400 to 800 Hz

// tools will turn this into a 61x10 ROM

always @(index)

case (index)

5'd0: coeff = 10'sd0;

5'd1: coeff = 10'sd0;

5'd2: coeff = 10'sd0;

5'd3: coeff = -10'sd1;

5'd4: coeff = 10'sd0:

5'd5: coeff = 10'sd0;

5'd6: coeff = 10'sd1;

5'd7: coeff = 10'sd3;

5'd8: coeff = 10'sd5;

5'd9: coeff = 10'sd8;

5'd10: coeff = 10'sd10;

5'd11: coeff = 10'sd12;

5'd12: coeff = 10'sd13;

5'd13: coeff = 10'sd12:

5'd14: coeff = 10'sd7;

5'd15: coeff = 10'sd0;

5'd16: coeff = -10'sd10;

5'd17: coeff = -10'sd22;

5'd18: coeff = -10'sd34;

5'd19: coeff = -10'sd44;

5'd20: coeff = -10'sd52;

5'd21: coeff = -10'sd54;

5'd22: coeff = -10'sd49;

5'd23: coeff = -10'sd38;

5'd24: coeff = -10'sd21;

5'd25: coeff = 10'sd0;

5'd26: coeff = 10'sd23;

5'd27: coeff = 10'sd46;

5'd28: coeff = 10'sd64;

5'd29: coeff = 10'sd77;

5'd30: coeff = 10'sd81;

5'd31: coeff = 10'sd77;

```

5'd32: coeff = 10'sd64; 5'd33: coeff = 10'sd46; 5'd34: coeff = 10'sd23; 5'd35: coeff = 10'sd0; 5'd36: coeff = -10'sd21;

```

5'd37: coeff = -10'sd38;

5'd38: coeff = -10'sd49;

5'd39: coeff = -10'sd54;

5'd40: coeff = -10'sd52;

5'd41: coeff = -10'sd44;

5'd42: coeff = -10'sd34;

5'd43: coeff = -10'sd22;

5'd44: coeff = -10'sd10;

5'd45: coeff = 10'sd0;

5'd46: coeff = 10'sd7;

5'd47: coeff = 10'sd12;

5'd48: coeff = 10'sd13;

5'd49: coeff = 10'sd12;

5'd50: coeff = 10'sd10;

5'd51: coeff = 10'sd8;

5'd52: coeff = 10'sd5:

5'd53: coeff = 10'sd3;

5'd54: coeff = 10'sd1;

5'd55: coeff = 10'sd0;

5'd56: coeff = 10'sd0;

5'd57: coeff = -10'sd1;

5'd58: coeff = 10'sd0;

5'd59: coeff = 10'sd0;

5'd60: coeff = 10'sd0;

default: coeff = 10'hXXX;

endcase

endmodule

module band3coeffs(

input wire [5:0] index,

output reg signed [9:0] coeff

// bandpass 800 to 1600 Hz

// tools will turn this into a 61x10 ROM

always @(index)

case (index)

5'd0: coeff = 10'sd0;

5'd1: coeff = 10'sd0;

5'd2: coeff = 10'sd0;

5'd3: coeff = 10'sd0;

5'd4: coeff = 10'sd2;

5'd5: coeff = 10'sd3;

5'd6: coeff = 10'sd3:

5'd7: coeff = 10'sd2;

5'd8: coeff = -10'sd2;

5'd9: coeff = -10'sd6;

5'd10: coeff = -10'sd9;

5'd11: coeff = -10'sd7;

```

);

```

5'd12: coeff = -10'sd3;

```

- 5'd13: coeff = 10'sd2;

- 5'd14: coeff = 10'sd3;

- 5'd15: coeff = 10'sd0;

- 5'd16: coeff = -10'sd5;

- 5'd17: coeff = -10'sd4;

- 5'd18: coeff = 10'sd7;

- 5'd19: coeff = 10'sd26;

- 5'd20: coeff = 10'sd43;

- 5'd21: coeff = 10'sd45;

- 5'd22: coeff = 10'sd21;

- 5'd23: coeff = -10'sd25;

- 5'd24: coeff = -10'sd76;

- 5'd25: coeff = -10'sd106;

- 5'd26: coeff = -10'sd94;

- 5'd27: coeff = -10'sd38;

- 5'd28: coeff = 10'sd40;

- 5'd29: coeff = 10'sd109;

- 5'd30: coeff = 10'sd136;

- 5'd31: coeff = 10'sd109;

- 5'd32: coeff = 10'sd40;

- 5'd33: coeff = -10'sd38;

- 5'd34: coeff = -10'sd94;

- 5'd35: coeff = -10'sd106;

- 5'd36: coeff = -10'sd76:

- 5'd37: coeff = -10'sd25;

- 5'd38: coeff = 10'sd21;

- 5'd39: coeff = 10'sd45;

- 5'd40: coeff = 10'sd43;

- 5'd41: coeff = 10'sd26;

- 5'd42: coeff = 10'sd7;

- 5'd43: coeff = -10'sd4;

- 5'd44: coeff = -10'sd5;

- 5'd45: coeff = 10'sd0:

- 5'd46: coeff = 10'sd3;

- 5'd47: coeff = 10'sd2:

- 5'd48: coeff = -10'sd3;

- 5'd49: coeff = -10'sd7;

- 5'd50: coeff = -10'sd9;

- 5'd51: coeff = -10'sd6;

- 5'd52: coeff = -10'sd2;

- 3 d32. coen 10 3d2

- 5'd53: coeff = 10'sd2;

- 5'd54: coeff = 10'sd3;

- 5'd55: coeff = 10'sd3;

- 5'd56: coeff = 10'sd2;

- 5'd57: coeff = 10'sd0;

- 5'd58: coeff = 10'sd0;

- 5'd59: coeff = 10'sd0;

```

5'd60: coeff = 10'sd0;

default: coeff = 10'hXXX;

endcase

endmodule

module band4coeffs(

input wire [5:0] index,

output reg signed [9:0] coeff

);

// bandpass 1600 to 3200 Hz

// tools will turn this into a 61x10 ROM

always @(index)

case (index)

5'd0: coeff = 10'sd0;

5'd1: coeff = 10'sd0;

5'd2: coeff = 10'sd1:

5'd3: coeff = 10'sd2;

5'd4: coeff = -10'sd1;

5'd5: coeff = -10'sd3;

5'd6: coeff = -10'sd1;

5'd7: coeff = 10'sd1;

5'd8: coeff = -10'sd1;

5'd9: coeff = 10'sd2;

5'd10: coeff = 10'sd9;

5'd11: coeff = 10'sd4:

5'd12: coeff = -10'sd11;

5'd13: coeff = -10'sd10;

5'd14: coeff = 10'sd3;

5'd15: coeff = 10'sd0;

5'd16: coeff = -10'sd3;

5'd17: coeff = 10'sd19;

5'd18: coeff = 10'sd29;

5'd19: coeff = -10'sd13;

5'd20: coeff = -10'sd44;

5'd21: coeff = -10'sd11;

5'd22: coeff = 10'sd12:

5'd23: coeff = -10'sd14;

5'd24: coeff = 10'sd18;

5'd25: coeff = 10'sd106;

5'd26: coeff = 10'sd48;

5'd27: coeff = -10'sd164;

5'd28: coeff = -10'sd194;

5'd29: coeff = 10'sd82;

5'd30: coeff = 10'sd274;

5'd31: coeff = 10'sd82;

5'd32: coeff = -10'sd194;

5'd33: coeff = -10'sd164;

5'd34: coeff = 10'sd48;

```

```

5'd35: coeff = 10'sd106;

5'd36: coeff = 10'sd18;

5'd37: coeff = -10'sd14;

5'd38: coeff = 10'sd12;

5'd39: coeff = -10'sd11;

5'd40: coeff = -10'sd44;

5'd41: coeff = -10'sd13;

5'd42: coeff = 10'sd29;

5'd43: coeff = 10'sd19;

5'd44: coeff = -10'sd3;

5'd45: coeff = 10'sd0;

5'd46: coeff = 10'sd3;

5'd47: coeff = -10'sd10;

5'd48: coeff = -10'sd11;

5'd49: coeff = 10'sd4;

5'd50: coeff = 10'sd9:

5'd51: coeff = 10'sd2;

5'd52: coeff = -10'sd1;

5'd53: coeff = 10'sd1;

5'd54: coeff = -10'sd1;

5'd55: coeff = -10'sd3;

5'd56: coeff = -10'sd1;

5'd57: coeff = 10'sd2;

5'd58: coeff = 10'sd1;

5'd59: coeff = 10'sd0:

5'd60: coeff = 10'sd0;

default: coeff = 10'hXXX;

endcase

endmodule

module BandpassFilterO(

input wire clock, reset, ready,

input wire signed [7:0] x,

output reg signed [17:0] y

);

reg signed[17:0]accumulator = 0;

reg [5:0]offset = 0;

reg signed [7:0] sample [61:0];

reg [5:0]index = 0;

req [6:0]counter = 0;

wire signed [9:0]coeff;

bandOcoeffs coeffs(.index(index),.coeff(coeff));

always @(posedge clock)

begin

```

```

if (ready)

begin

offset <= offset + 1;

sample[offset] <= x;</pre>

accumulator <= 0;

index \le 0;

counter <= 0;

end

else if (counter < 61)

begin

accumulator <= accumulator + coeff*sample[offset-index];

index \le index + 1;