## **Musical Feet:**

# A Step-by-Step Approach to Music Generation

Rajeev Nayak Harley Zhang

#### **ABSTRACT**

The goal of this project is to generate random music in real time as a response to the user's walking pace. The music follows Western classical chord progressions, and the tempo and tonality change based on the frequency characteristics of the user's pace. An electromechanical pedometer senses the user's footsteps. The resulting analog signal is converted to a digital signal and sent to digital processing modules. The tempo of the music is controlled by the frequency of the footsteps, and the tonality responds to the level of fluctuation in the frequency. A finite state machine generates a chord progression in real time using these inputs. Based on the chords, an algorithm generates notes for each instrument of a string quartet following Western classical voice leading techniques. String instrument samples are stored and accessed based on the generated pitches, producing digital audio data that is combined and converted to an analog output. The user will be able to hear a pleasing musical strain while walking or running, providing auditory feedback of their pace.

## **Table of Contents**

| 1) Overview                                                        | 1     |

|--------------------------------------------------------------------|-------|

|                                                                    |       |

| 2) Pedometer Input Processing Modules                              | 3     |

| 2.1) Pedometer (Harley)                                            | 3     |

| 2.2) Schmitt Trigger Inverter ADC (Raieev)                         | 3     |

| 2.3) Pedometer Data Filter (Rajeev)  2.4) Tempo Generator (Harley) | 6     |

| 2.4) Tempo Generator (Harley)                                      | <br>4 |

| 2.5) Tonality Generator (Harley)                                   | <br>6 |

| 2.6) Beat Generator (Harley)                                       |       |

| 2.7) Testing of Pedometer Input Processing Modules                 | 0     |

|                                                                    |       |

| 3) Music Composition Modules                                       | 8     |

| 3.1) Random Number Generator (Rajeev)                              | 8     |

| 3.2) Chord Generator (Rajeev)                                      | 9     |

| 3.3) Note Generator (Rajeev)                                       | 11    |

| 3.3.1) "Wait For Chord" State                                      | 12    |

| 3.3.2) Bottom-Up Note Search                                       | 12    |

| 3.3.3) Top-Down Note Search                                        | 14    |

| 3.3.4) "Finish" State                                              |       |

| 3.4) Testing of Music Composition Modules                          | 15    |

| 4) Music Synthesis and Audio Modules                               | 16    |

| 4.1) Instrument Modules                                            |       |

| 4.1.1) String BRAMs (Harley)                                       | 17    |

| 4.1.2) Oscillator (Harley)                                         |       |

| 4.1.3) Envelope Generator (Rajeev)                                 | 18    |

| 4.1.3.1) "Wait For Sample" State                                   | 19    |

| 4.1.3.2) "Adjust Envelope" State                                   | 19    |

| 4.1.3.3) "Apply Envelope" State                                    | 19    |

| 4.1.3.4) "Wait For Mixer" State                                    |       |

| 4.2) Mixer (Rajeev)                                                | 20    |

| 4.3) AC97 Driver (Rajeev)                                          | 20    |

| 4.4) Testing of Music Synthesis and Audio Modules                  | 21    |

| 5) | Video Output Modules                                      | 22             |

|----|-----------------------------------------------------------|----------------|

|    | 5.1) XVGA Module (Harley)                                 | 22             |

|    | 5.2) Music Information Modules (Harley)                   |                |

|    | 5.2.1) String Display Module                              | 22             |

|    | 5.2.2) Cycles-to-Decimal BPM Converter                    | 23             |

|    | 5.2.3) Decimal Digit-to-Character Converter               | 24             |

|    | 5.2.4) Chord-to-Characters Converter                      | 24             |

|    | 5.3) Visualization Modules (Harley)                       | 24             |

|    | 5.3.1) Footprint Modules                                  | 24             |

|    | 5.4) Testing of Video Output Modules                      | 25             |

| 6) | Conclusion                                                | 26             |

| 7) | References                                                | 27             |

| 8) |                                                           | 28             |

|    | 8.1) Pedometer Data Filter                                | 28             |

|    | 8.2) Tempo Generator                                      | 29             |

|    | 8.3) Tonality Generator                                   | 31             |

|    | 8.4) Beat Generator                                       | 33             |

| 9) | Appendix B: Verilog – Music Composition Modules           | 34             |

| ĺ  | 9.1) Random Number Generator                              | 34             |

|    | 9.2) Chord Generator                                      |                |

|    | 9.3) Note Generator                                       |                |

| 10 | ) Appendix C: Verilog – Music Synthesis and Audio Modules | 67             |

|    | 10.1) Violin Module                                       | <del></del> 67 |

|    | 10.2) Viola Module                                        | 69             |

|    | 10.3) Cello Module                                        | ${71}$         |

|    | 10.4) Oscillator                                          | 73             |

|    | 10.5) Envelope Generator                                  |                |

|    | 10.6) Mixer                                               | 70<br>79       |

|    | 10.7) AC97 Driver Modules                                 |                |

|    | 10.1,110,110,1110,1110,110                                |                |

| 11) | Appendix D: Verilog – Video Output Modules                 | 86 |

|-----|------------------------------------------------------------|----|

|     | 11.1) XVGA Module                                          | 86 |

|     | 11.2) Music Information Module                             | 87 |

|     | 11.3) String Display Module                                | 88 |

|     | 11.4) Cycles-to-Decimal BPM Converter                      | 89 |

|     | 11.5) Decimal Digit-to-Character Converter                 | 91 |

|     | 11.6) Chord-to-Characters Converter                        | 92 |

|     | 11.7) Visualization Module                                 | 93 |

|     | 11.8) Left Footprint Module                                | 95 |

|     | 11.9) Right Footprint Module                               | 96 |

| 12) | Appendix E: Verilog – Top Level and Miscellaneous Modules_ | 97 |

|     | 12.1) Debouncer                                            | 97 |

|     | 12.2) Synchronizer                                         | 97 |

|     | 12.3) 32-Bit Counter                                       | 98 |

|     | 12.4) Top Level Module                                     | 99 |

|     |                                                            |    |

## **List of Tables and Figures**

| Figure 1. High-level block diagram of Musical Feet system | 1  |

|-----------------------------------------------------------|----|

| Figure 2. Output waveform of Schmitt trigger inverter     | 3  |

| Figure 3. Circular buffer of tempo generator.             | 5  |

| Figure 4. Diagram of random number generator              | 8  |

| Table 1. Encoding of notes in an octave                   | 9  |

| Table 2. State transition table of chord generator.       | 10 |

| Figure 5. State transition diagram of note generator.     | 11 |

| Table 3. Encoding of notes for string quartet             | 13 |

| Figure 6. Block diagram of violin module.                 | 16 |

| Figure 7. Amplitude envelope of two consecutive notes.    | 18 |

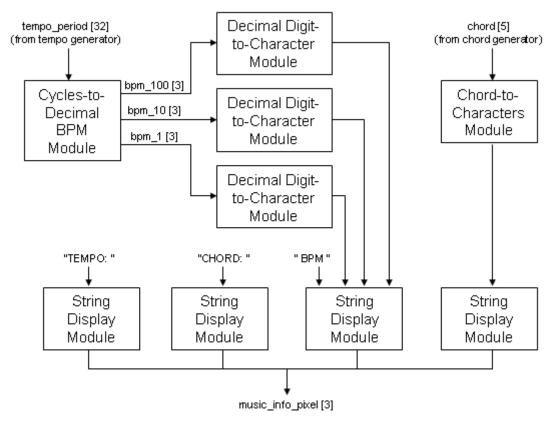

| Figure 8. Block diagram of music information module.      | 23 |

#### 1 Overview

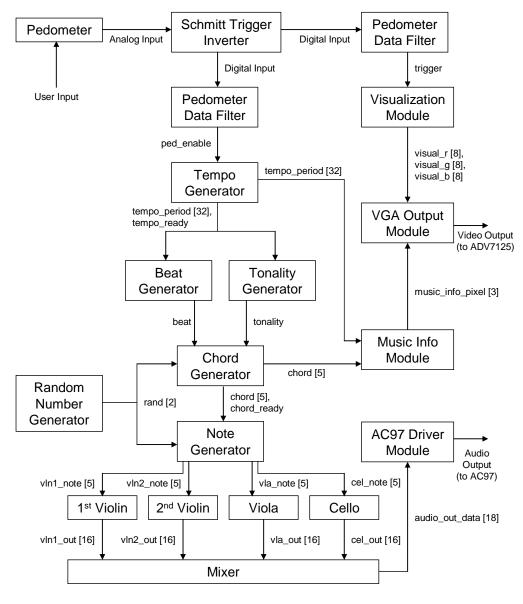

The Musical Feet system generates string quartet music in real time based on input from the user's footsteps. The tempo of the music reflects the user's pace, and the tonality of the music is determined by how much the user's pace fluctuates. This is achieved through a series of digital modules, in addition to analog circuitry at the system inputs and outputs. Figure 1 shows the high-level block diagram of the entire system. These different components can be grouped into four different sections: the pedometer input processing modules, the music composition modules, the music synthesis and audio modules, and the video output modules.

Figure 1. High level block diagram of Musical Feet system. Numbers in brackets indicate bit width of signals.

The pedometer input processing modules take an analog signal produced by a pedometer whenever a footstep is taken and use it to generate a tempo and tonality for the music output. The analog signal from the pedometer is first converted to a digital signal which indicates when each footstep is taken. A tempo period is generated by the tempo generator module to match the interval between the user's successive footsteps. Then, based on these tempo periods, the tonality is determined by the tonality generator module. When the pace is fairly constant, the tonality will be major. Otherwise, the tonality will be minor. The tempo period is also used to produce a beat signal, which enables once every tempo period.

The music composition modules generate the notes for the string quartet based on the tonality and beat inputs from the input processing modules. On every beat, the chord generator module decides on a new chord using the previous chord and the tonality. It produces chord progressions that reflect the Western classical tradition, and it changes the key of the played music as the tonality changes. The note generator uses the chord to assign a note to each of the four instruments in a string quartet: a cello, a viola, and two violins.

The music synthesis and audio modules output the notes produced in the music composition modules as they would be played by a string quartet. Samples of each string of each instrument are stored in block RAMs. Oscillators access these samples at frequencies corresponding to the notes from the music composition modules. The resulting sample waveforms are modulated by an amplitude envelope, imitating the amplitude of a note bowed on a string. Once the amplitude is modulated, the signals from the four instruments are added together in the mixer and sent to the AC97 DAC. From there, the analog signal can be heard through speakers or headphones.

The video output modules display information related to the generated music and the system's input on a 1024x768 XVGA display. In Music Information mode, the video output shows the current tempo of the music in beats per minute and the current chord. In Visualization mode, the video output shows a footprint pattern each time a footstep is asserted. Thus, the video output modules show information from other parts of the Musical Feet system.

The modules of these four parts will be described in further technical detail in the following sections.

## **2** Pedometer Input Processing Modules

The Musical Feet system is controlled through the footsteps of the user. A pedometer worn by the user produces an analog signal each time the user takes a footstep, and this signal is then converted to a digital signal. From this footstep signal, the system generates a tempo and tonality for the music output. The tempo is then converted to a beat signal that determines when new notes will be played. All of the digital pedometer input processing modules are clocked off a 27MHz clock signal produced by the 6.111 Labkit.

#### 2.1 Pedometer

The pedometer used in the Musical Feet system is Walking Advantage 342, by Sportline. Run off a 1.5V battery, it contains a mechanical arm that moves and induces a voltage whenever a step is taken. Wires are soldered onto the ground node and output node of the pedometer's PCB, and then connected onto the breadboard of the 6.111 Labkit for analog-to-digital conversion and filtering. The voltage at the output node is normally about 1.4V, and it drops briefly to about 0V when a step is taken.

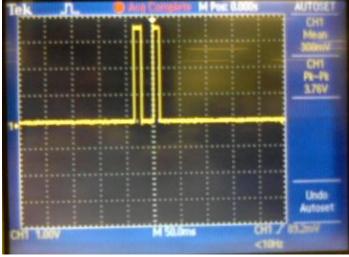

## 2.2 Schmitt Trigger Inverter ADC

To convert the pedometer's analog signal to a digital signal, a Schmitt trigger inverter ADC (54LS14) is used. This chip is powered off a 5V source and compares the input value to its two internal thresholds. If the input is lower than the low threshold, the inverter outputs a high value of about 3.4V. If the input is higher than the high threshold, the inverter outputs a low value of about 0.25V. When the input is between the thresholds, the output maintains its previous value. Thus, the Schmitt trigger inverter asserts high when a step is taken and low otherwise. The output is noisy (Figure 2), so a filter is needed before it can be used by the digital system.

Figure 2. Output waveform of the Schmitt trigger inverter when a step is taken. The noisy analog signal produces a false assertion of the digital signal.

#### 2.3 Pedometer Data Filter

The pedometer data filter removes false assertions of the digital signal produced by the ADC. When a rising edge occurs on this digital signal, the filter outputs a high value. For the next 0.2 seconds, the filter outputs a low value, even if there is a rising edge on the input. Otherwise, while the digital input is low, the output will also be low. This effectively eliminates false assertions because from observation, all false assertions occur within 0.2 seconds of the real assertion. After 0.2 seconds, the pedometer output is low until the next step is taken.

This also has the effect of limiting the speed at which the user can take steps to a rate of 300 steps per minute. For the tempo generation discussed below, this means that the maximum attainable tempo is 300 beats per minute (BPM). This is reasonable as an upper bound, since music generally is not written at higher tempos. Also, this allows sound synthesis effects like vibrato and enveloping to be clearly heard (Section 4.1.3).

## 2.4 Tempo Generator

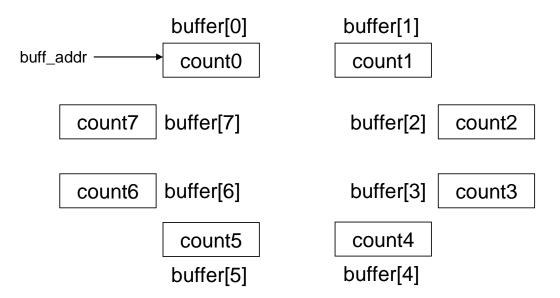

The tempo generator takes the pedometer data filter's output and creates a 32-bit tempo period, measured in numbers of cycles from one beat to the next. The filter's output is high for a single cycle when each footstep is asserted and low otherwise. The tempo generator contains a 32-bit counter. Whenever a footstep is asserted, it stores the value of the count and resets the counter. The count is stored in a circular buffer with eight locations. The current buffer address is also incremented when a footstep is asserted. Since the buffer is circular, whenever a new footstep is taken, the new count overwrites the oldest count (Figure 3, p. 5). On the first footstep, every location in the buffer is initialized with the value of count, which corresponds to the number of cycles that have elapsed between the system start time and the footstep assertion.

To make tempo changes gradual for rapid changes in footstep speeds, the tempo generator takes a weighted average of the previous eight counts. The output tempo period is equal to  $\frac{1}{2}$  times the most recent count, plus  $\frac{1}{4}$  times the next most recent count, and so on with the  $n^{th}$  most recent count weighted  $2^{-n}$  up to n = 8. The tempo generator uses eight clock cycles to add these weighted counts, which are easily produced by bit-shifting to divide by appropriate powers of 2. After computing the tempo period, the tempo\_ready signal is asserted for one cycle, signaling that the output tempo period is valid and ready for use in other modules.

Figure 3(a). Circular buffer of tempo generator after eighth footstep. A new data value, count7, has just been placed in buffer[7], and the buffer address has been incremented to the location of the oldest data value.

Figure 3(b). Circular buffer of tempo generator after ninth footstep. A new data value, count8, has just been placed in buffer[0], and the buffer address has been incremented to the location of the oldest data value.

## 2.5 Tonality Generator

The tonality generator uses the tempo period produced by the tempo generator to determine the tonality of the music output. The tonality output is a single bit, for which 0 corresponds to minor and 1 corresponds to major. The structure of the tonality generator is very similar to that of the tempo generator. Whenever the tempo\_ready signal is asserted, the tonality generator takes the new tempo period and stores the absolute difference between the new tempo period and the previous tempo period. The differences are stored in a circular buffer with eight locations. The buffer address increments each time a new tempo is stored.

Like the tempo generator, the tonality generator takes a weighted average of the data in the buffer. An average value is generated equal to ½ times the most recent count, plus ¼ times the next most recent count, and so on with the n<sup>th</sup> most recent count weighted 2<sup>-n</sup> up to n = 8. This weighted average corresponds to the level of fluctuation in the speed of the user's footsteps. It is compared to a threshold value to produce the tonality output. If the average is less than the threshold, the user's footsteps are occurring at a fairly constant speed, and the tonality of the music is major. Otherwise, the user's footsteps fluctuate significantly, so the tonality is minor. The threshold value was empirically determined to maintain an appropriate balance between major and minor.

#### 2.6 Beat Generator

The beat generator takes in the tempo period from the tempo generator when tempo\_ready is asserted. Using a 32-bit counter, it produces a signal that asserts high for one cycle at a speed that matches the tempo period. The counter resets only when a beat is asserted. The tempo period is in number of cycles per beat, so when the value of the count matches the value of the tempo period, the output beat signal asserts high. If a new tempo period occurs on the input and is less than the current count, a beat is asserted and the counter resets and restarts counting. If the new tempo period is greater than the current count, then the counter continues counting and does not reset.

The initial value of the previous tempo period is set to 32'hFFFFFFF, so if the system is turned on and no footsteps are ever taken, music will play with the corresponding tempo, which has a period of 32'hFFFFFFF / 27MHz = 159 seconds. Thus, with no footsteps applied to the system input, the notes of the audio output still change, but only once per 159 seconds.

## 2.7 Testing of Pedometer Input Processing Modules

The tempo generator was tested by hooking up its input to a signal derived from a button on the 6.111 Labkit and its output to the Labkit's hexadecimal LED display. A module modified the debounced button signal to only assert high on the cycle that the button was pressed. When the button was pressed at a rate of once per second, the displayed output was close to 27000000, which is the number of cycles of the clock signal per second. Then, when the rate of button presses was suddenly changed to a constant faster speed, the displayed output gradually approached the number of cycles corresponding to the new speed. Also, the hex display showed the output of a counter that incremented whenever the tempo\_ready signal was asserted. As expected, the counter incremented each time the button was pressed.

The tonality generator was wired to receive the outputs of the tempo generator. Its tonality output and also its weighted average of tempo differences were wired to the hex display. The button was pressed at varying intervals to check that the tonality value matched the comparison value of the weighted average and the threshold.

The beat generator was then wired to receive the outputs of the tempo generator. A counter that incremented whenever the beat signal asserted high was wired to the hex display. The counter was found to increment at a rate corresponding to various tempo periods.

The pedometer and analog circuitry were initially tested apart from the digital modules. The appropriate spots to solder wire onto the pedometer PCB were identified using a multimeter and oscilloscope. The wires were soldered in locations where they interfered least with the mechanical components of the pedometer. The pedometer was clipped onto various regions of the body to find where it detected steps most accurately. This was found to be at the front center of the user's pants, where it could pick up on the motion of both legs.

The ADC was then wired up and the pedometer signal was wired to its input. Originally, an operational amplifier had been used as a comparator to produce a digital signal based on a single threshold reference voltage. This was replaced by a Schmitt trigger inverter, which produces a less noisy output signal because it uses two thresholds. However, after examining the inverter's output on the oscilloscope, the digital signal was still found to be false asserting high less than 0.2 seconds after the initial assertion. A pedometer data filter was added, producing a clean output signal.

Finally, the input of the tempo generator module was changed from the Labkit button to the output of the pedometer data filter. Whenever a step was taken, the hex display showed that the outputs of the input processing modules were behaving as desired.

## **3 Music Composition Modules**

The role of the music composition modules is to generate notes in real time for a string quartet based on the output of the pedometer input processing modules. The chord generator is responsible for figuring out the next chord that the quartet should play using the tonality it receives from the tonality generator. The note generator then figures out the next note that each instrument plays based on the new chord. The decisions made in the music composition had to involve some randomness, or else the music would have been entirely predictable and boring. In order to achieve this, the decisions made by the two composition modules take into account the value of a 2-bit number that comes from a random number generator. Altogether, these three modules handle all of the real-time music composition in the system.

#### 3.1 Random Number Generator

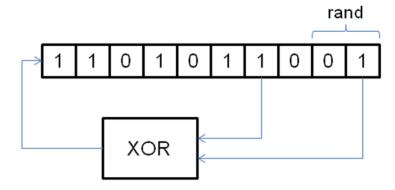

The random number generator is implemented as a 10-bit Fibonacci linear feedback shift register (LFSR), with the low-order 2 bits as the output. Essentially, this is a 1023-state FSM, where each state corresponds to a distinct nonzero 10-bit number. The LFSR transitions to a new number at every clock cycle by shifting its previous number to the right by one bit. The new high-order bit is determined by two bits in the previous number called the taps. In a 10-bit LFSR, the optimal taps are bit 0 and bit 3. This means that at each cycle, the new high-order bit equals the XOR of the previous bits 0 and 3. This allows the LFSR to cycle through all 1023 nonzero values of the 10-bit number. The LFSR is depicted in Figure 4 below.

The LFSR value is initialized with a random seed generated by the random number generator module. A 10-bit counter in the module increments at each clock cycle, starting at the system reset. Every time the user reset is enabled, the value of the counter is used as a new seed for the LFSR. However, if the value of the seed is 0, the LFSR is seeded with 1 instead. This is required because if the LFSR is initialized with a value of 0, every subsequent value of the LFSR will also be 0. By assuring that the seed is not 0, the LFSR is guaranteed to enter its 1023-number cycle.

Figure 4. Diagram of random number generator. This is a 10-bit Fibonacci linear feedback shift register, and the two low-order bits are used as the "rand" output.

#### 3.2 Chord Generator

The chord generator uses the tonality and random number outputs to determine the next chord based on the previous chord. The module is implemented as an FSM, where each state corresponds to a certain chord. There are six states: S\_I, S\_IV, S\_V, S\_i, S\_iv, S\_v. The first three of those states correspond to the major key tonic, subdominant, and dominant chords, respectively. Similarly, the last three correspond to the minor key tonic, subdominant, and dominant chords. The tonic note of the current key of the music is stored internally in the chord generator as a 4-bit number. The value of the note is encoded using values shown in Table 1 below. The key and the state of the FSM are used to determine the chord.

Table 1: Encoding of notes in an octave.

| Value | Note |

|-------|------|

| 0     | A    |

| 1     | A#   |

| 2     | В    |

| 3     | С    |

| 4     | C#   |

| 5     | D    |

| 6     | D#   |

| 7     | Е    |

| 8     | F    |

| 9     | F#   |

| 10    | G    |

| 11    | G#   |

The chord generator FSM transitions each time the beat output is enabled by the beat generator. The transitions from chord to chord are dictated by standard Western classical chord progressions. If the tonality of the music is major, the FSM will continue to transition between the S\_I, S\_IV, and S\_V states, and the key will remain the same. If the tonality is minor, the FSM will transition between the S\_i, S\_iv, and S\_v states, and the key will remain the same. However, if the tonality changes, the FSM will transition from a major key state to a minor key state or vice versa. During this transition, the value of the key may change. Some of the chord transitions allow the tonic note of the key to stay the same, with just the tonality of the key changing. However, other transitions only make sense when the key changes to a completely different tonic note. These transitions also conform to the Western classical tradition. The FSM transition table is shown on the next page in Table 2.

Table 2: State transition table of chord generator.

| <b>Current State</b> | tonality | rand[0] | rand[1] | Next State | chord[3:0] |

|----------------------|----------|---------|---------|------------|------------|

| S_I                  | 0        | 0       | -       | S_iv       | key        |

| S_I                  | 0        | 1       | 0       | S_i        | key        |

| S_I                  | 0        | 1       | 1       | S_v        | key        |

| S_I                  | 1        | 0       | _       | S_I        | key        |

| S_I                  | 1        | 1       | 0       | S_IV       | key        |

| S_I                  | 1        | 1       | 1       | S_V        | key        |

| S_IV                 | 0        | 0       | _       | S_i        | key + 5    |

| S_IV                 | 0        | 1       | _       | S_v        | key + 5    |

| S_IV                 | 1        | 0       | _       | S_V        | key + 5    |

| S_IV                 | 1        | 1       | 0       | S_IV       | key + 5    |

| S_IV                 | 1        | 1       | 1       | S_I        | key + 5    |

| S_V                  | 0        | 0       |         | S_i        | key + 7    |

| S_V                  | 0        | 1       | _       | S_v        | key + 7    |

| S_V                  | 1        | 0       | _       | S_V        | key + 7    |

| S_V                  | 1        | 1       | _       | S_I        | key + 7    |

| S_i                  | 0        | 0       |         | S_i        | key        |

| S_i                  | 0        | 1       | 0       | S_iv       | key        |

| S_i                  | 0        | 1       | 1       | S_v        | key        |

| S_i                  | 1        | 0       | _       | S_V        | key        |

| S_i                  | 1        | 1       | 0       | S_IV       | key        |

| S_i                  | 1        | 1       | 1       | S_I        | key        |

| S_iv                 | 0        | 0       | _       | S_v        | key + 5    |

| S_iv                 | 0        | 1       | 0       | S_iv       | key + 5    |

| S_iv                 | 0        | 1       | 1       | S_i        | key + 5    |

| S_iv                 | 1        | 0       | -       | S_V        | key + 5    |

| S_iv                 | 1        | 1       |         | S_I        | key + 5    |

| S_v                  | 0        | 0       | -       | S_v        | key + 7    |

| S_v                  | 0        | 1       | _       | S_i        | key + 7    |

| S_v                  | 1        | 0       | -       | S_V        | key + 7    |

| S_v                  | 1        | 1       |         | S_I        | key + 7    |

Once the FSM is done transitioning, the value of the chord is outputted. The high-order bit of the output indicates the tonality of the chord. This is set to 1 only if the current state is S\_I, S\_IV, S\_V, or S\_v, because they are all major chords. Otherwise, it is set to 0. The lower four bits of the output indicate the root note of the chord. This is easily calculated using the key and the state. The root note of a tonic chord is the tonic note of the key, so chord[3:0] equals the value of key when the state is either S\_I or S\_i. The root of a subdominant chord is 5 half steps above the tonic note, so chord[3:0] equals the value of key plus 5 when the state is either S\_IV or S\_iv. Finally, the root of a dominant chord is 7 half steps above the tonic note, so chord[3:0] equals the value of key plus 7 when the state is either S\_V or S\_v. When the new chord is calculated, the chord generator enables the chord\_ready signal for one cycle and starts waiting for the next beat assertion.

#### 3.3 Note Generator

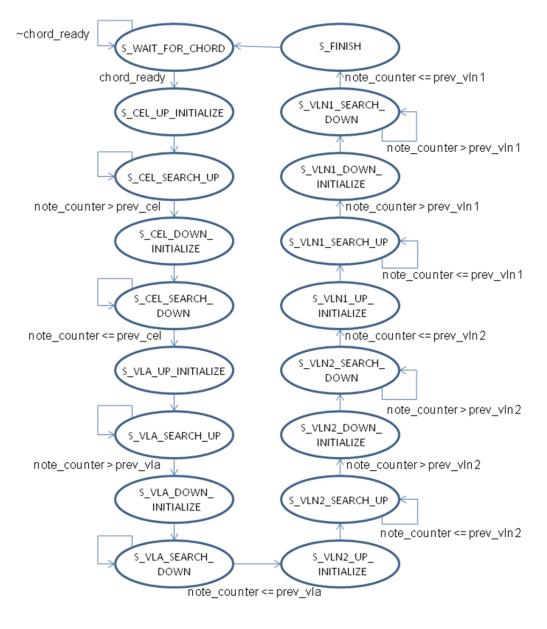

The note generator calculates the notes that the instruments in the string quartet need to play based on the chord it receives from the chord generator. It makes sure that all of the notes of the chord are played so that the chord sounds full. It takes into consideration the previous notes played by the instruments as well, following standard Western classical voice leading techniques that make chord transitions sound smooth. It also adds some randomness in the choice of notes while maintaining these properties. It achieves this by searching for each instrument's note in succession before outputting all four notes. The note generator is implemented as an FSM, where each state involves a different stage of the note computation algorithm. The state transition diagram is depicted in Figure 5 below.

Figure 5. State transition diagram of note generator.

#### 3.3.1 "Wait For Chord" State

The initial state of the FSM is the "wait for chord" state, in which the note generator remains idle, waiting for the next chord from the chord generator. When the chord\_ready signal is enabled, the FSM transitions to the next state.

#### 3.3.2 Bottom-Up Note Search

The next state initializes the note generator for the bottom-up cello note search. Each instrument's note search involves a bottom-up search and a top-down search. Each of these searches finds a number of candidate notes that could be assigned to the instrument. Once the search is over, the random number generator output is used to decide which of the candidates to assign to the instrument. The goal of the bottom-up cello note search is to find the nearest note lower than the previous cello note that fits into the new chord and meets an additional constraint. In order for a chord to sound full, the cello note has to play one of the bottom two notes in the chord: the root or the third. If the cello plays the top note in the chord, the fifth, the sound of the chord will be altered. Also, the bottom-up search checks to see if the previous cello note meets these criteria as well.

The bottom-up note search is performed using a 6-bit register called the note counter. The note counter stores the note that is currently being considered as a candidate in the note search. The note generator considers all of the notes from the bottom of the cello to the top of the violin, a range which spans multiple octaves. This means that the value of the note cannot be represented by the 4-bit encoding used in the chord generator. Instead, a 6-bit encoding is used, which is shown in Table 3 on the next page. The lowest note that a cello can play is C2 and the highest note that the violin is allowed to play in our system is C6. The encoding starts with A2 for simplicity, since the 4-bit octave encoding started with A.

In the cello bottom-up search, the note counter is initialized to the lowest note on the cello that fits in the current chord. The note counter increases after each clock cycle. This increase is determined by a minor FSM in the note generator module. This FSM keeps track of the type of note in the chord that the note counter is currently storing: the root, the third, or the fifth. If the note counter currently has the root of the chord, on the next clock cycle its value will be increased to the third of the chord. If it has the third of the chord, its value will be increased to the fifth of the chord. If it has the fifth of the chord, its value will be increased to the next root of the chord, which will be an octave above the previous root of the chord. For example, in an A major chord, all A's (A2, A3, A4, A5, and A6) are roots of the chord, all C#'s (C#2, C#3, C#4, and C#5) are thirds of the chord, and all E's (E2, E3, E4, and E5) are fifths of the chord.

Table 3: Encoding of notes for string quartet.

| Value | Note | Value | Note |

|-------|------|-------|------|

| 0     | A2   | 26    | B4   |

| 1     | A#2  | 27    | C4   |

| 2     | B2   | 28    | C#4  |

| 3     | C2   | 29    | D4   |

| 4     | C#2  | 30    | D#4  |

| 5     | D2   | 31    | E4   |

| 6     | D#2  | 32    | F4   |

| 7     | E2   | 33    | F#4  |

| 8     | F2   | 34    | G4   |

| 9     | F#2  | 35    | G#4  |

| 10    | G2   | 36    | A5   |

| 11    | G#2  | 37    | A#5  |

| 12    | A3   | 38    | B5   |

| 13    | A#3  | 39    | C5   |

| 14    | В3   | 40    | C#5  |

| 15    | C3   | 41    | D5   |

| 16    | C#3  | 42    | D#5  |

| 17    | D3   | 43    | E5   |

| 18    | D#3  | 44    | F5   |

| 19    | E3   | 45    | F#5  |

| 20    | F3   | 46    | G5   |

| 21    | F#3  | 47    | G#5  |

| 22    | G3   | 48    | A6   |

| 23    | G#3  | 49    | A#6  |

| 24    | A4   | 50    | В6   |

| 25    | A#4  | 51    | C6   |

As the note counter increments through notes in the chord, the bottom-up cello note search algorithm checks if they are either the root or the third of the chord. If a note fits the criteria, it is stored in a temporary register called lower\_note. Also, the note type (root or third, in this case), is stored in a temporary register called lower\_note\_type. When the note counter exceeds the previous cello note value, the bottom-up search stops. This ensures that the value stored in the lower\_note register is the nearest note lower than the previous note that fits the criteria. If the note counter also finds that the previous cello note fits the criteria, it stores the note type in a register called same\_note\_type.

#### 3.3.3 Top-Down Note Search

Once these notes are found, the bottom-up search ends and the top-down search begins. Once again, the note counter is initialized with a note value, this time the highest possible note on the cello that fits into the current chord. Instead of increasing at each clock cycle, the note counter decreases during the top-down search. When a note fits the criteria, it is stored in the higher\_note register and its type is stored in the higher\_note\_type register. After the note counter drops below the previous cello note, the top-down search is over, and the algorithm chooses the new cello note. During the two searches, the algorithm could have found anywhere between one and three candidates for the new cello note; some subset of the lower note, same note, and higher note. At the end of the top down search, the note generator module uses the random number generator output to select one of the found candidates to be the next cello note.

So far, the search has adhered to standard voice leading procedures, as the new note is guaranteed to be in close proximity to the previous note. However, the filling in of the chord has not been achieved yet. In order to do this, the module keeps track of which note types have been assigned at the end of each top-down search. In the viola, violin 2, and violin 1 note searches, the previous note types are taken into account. Just like the cello had the special criterion (it could not be the fifth of the chord), the successive note searches determine their criteria based on the previously chosen notes. By the end, two of the instruments should be playing the root of the chord, one should be playing the third, and one should be playing the fifth.

#### 3.3.4 "Finish" State

The other three note searches proceed exactly as the cello note search, and once they are all done, the FSM transitions into the "finish" state for one clock cycle. In this state, it stores all of the note values so that they can be used as the previous values in the next note search. In addition, each of the note values is scaled by a certain value. This needs to happen because the modules in the audio synthesis section of the system use a different note indexing. Since each instrument is handled by a separate module in the synthesis section, the note encoding starts at the lowest note for each instrument. Therefore, the scaling is performed by subtracting the value of the lowest note for each instrument on the absolute scale defined in Table 3.

## 3.4 Testing of Music Composition Modules

The music composition modules were heavily tested using the 64-bit hexadecimal display on the 6.111 Labkit. The random number generator was tested quickly and easily by feeding the output to the display. The chord generator was also tested easily by outputting the state of the FSM and the current chord output onto the display while controlling the tonality with a switch and generating a beat every 3 seconds using a clock divider. However, difficulties arose while testing the complicated note generator module.

The note generator module behaved very erratically when it was first built. The hexadecimal display was also used to test this module by showing the value of each instrument's note in addition to the chord that came from the chord generator. The values of the notes were checked against the value of the chord to make sure that they corresponded. However, sometimes the notes behaved oddly. The instruments would often get stuck on the same four notes, no matter how much the chord changed. Also, the notes would sometimes cycle between a couple values, completely ignoring the changes in the chord.

After running into these problems over and over again, the decision was made to completely revamp the note generator. In fact, the current iteration of the note generator is drastically different from the version that was initially tested. In the old version, the note counter was never initialized more than once. It only performed a single bottom-up search, assigning the values of all four notes quickly. However, this made the logic extremely complicated and convoluted, which probably caused all of the errors. In the end, the decision was made to ignore the speed and efficiency of the module and focus on correctness and understandability. The note search logic is quite complicated, especially in a hardware implementation, so making the algorithm understandable is extremely important. Also, speed and efficiency were not as important as expected, because the extra 30 or so clock cycles that the new note generator takes to run are not noticeable to the human eye or ear. Once the note generator was remade from scratch, all of the erratic behavior was gone and it behaved perfectly, completing the music composition modules.

## 4 Music Synthesis and Audio Modules

The output audio of the Musical Feet system takes the form of a string quartet consisting of two violins, a viola, and a cello playing the notes produced by the Music Composition Modules. High-level modules for each instrument contain BRAMs to store sound samples, oscillators to select the correct pitches, and envelope generators to add sound effects to make the sounds more similar to real string instruments. The digital audio signals are then combined in a mixer and sent to an AC97 driver module. They are then converted into an analog signal through the AC97 DAC and sent to speakers or headphones to be played as sound. All of the music synthesis and audio modules are clocked off a 27MHz clock signal produced by the 6.111 Labkit.

#### 4.1 Instrument Modules

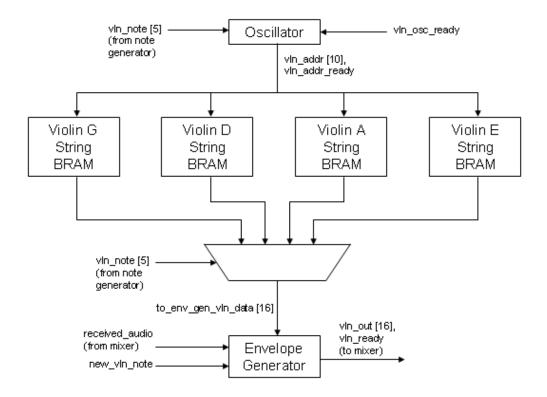

The Musical Feet system contains three different instruments: the violin, viola, and cello. Each has its own high-level module that contains various submodules. The high-level modules differ from each other in the sound samples stored in their BRAMs. These three modules each take in a note from the note generator and output corresponding digital audio signals to the mixer. Figure 6 shows a block diagram of the violin module. The viola and cello modules have identical structures.

Figure 6. Block diagram of violin module. The viola and cello modules are identical to the violin module except they have their appropriate BRAMs and signal names.

#### 4.1.1 String BRAMs

The string BRAMs each contain 16-bit wide samples of an open string played on a string instrument. Each high-level instrument module contains four different BRAMs, corresponding to the four open strings of each instrument. The samples were obtained from the Internet in the form of .aiff and .wav files (References, p. 27). The .aiff files were converted to .wav files. The .wav files were then processed in MATLAB to isolate single periods of the audio waveforms. The data from these single periods were then converted into .coe files that initialize the string BRAMs. There are a total of nine different BRAMs, since the viola's three higher strings have the same pitches as the violin's lower three strings. The viola and violin are similar enough in timbre that this sharing of strings is valid. The .wav files were sampled at 44.1kHz, so the high-level instrument modules get new sample data from the BRAMs every 612 cycles of the 27MHz clock (27MHz / 44.1kHz = 612). The appropriate BRAM is selected by the high-level instrument modules based on the selected note and the output data of the BRAM is then sent to the envelope generator module.

#### 4.1.2 Oscillator

The oscillator determines the rate at which the address of the BRAMs should be incremented, thereby controlling the pitch of the output audio waveform. Since there are twelve half-steps in each octave for Western music, the frequency of any note is  $2^{(1/12)}$  times the frequency of the note that is one half-step lower. Based on the note given by the note generator, the oscillator picks the appropriate power of  $2^{(1/12)}$ , accurate to ten binary decimal places, as the increment interval. On the next cycle, the interval is added to the internal address value. The actual address is outputted as the whole number part of the internal address value. Thus, the BRAM is accessed at the frequency that will produce audio data matching the input note's pitch.

Additional logic in the oscillator makes the address loop back to the beginning of the BRAM when the corresponding BRAM's maximum depth is reached. The oscillator also has an addr\_ready signal that asserts when the oscillator has the next BRAM address.

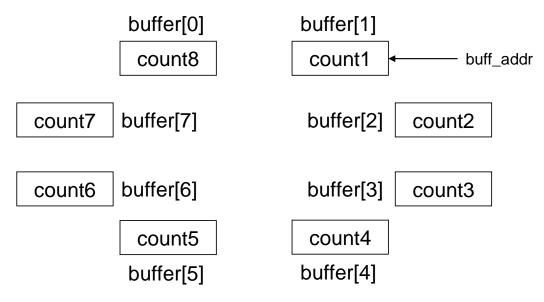

#### 4.1.3 Envelope Generator

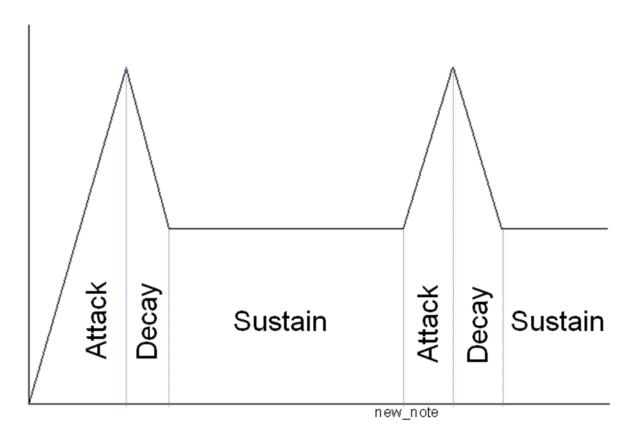

The envelope generator reads each sample from the BRAM and modulates its amplitude in order to make the output waveform sound like a bowed string. It achieves this by applying an ADSR (attack, decay, sustain, and release) envelope on the BRAM sample waveform. When a note is initially played with a bow, the bow hits the string and the amplitude of the note increases rapidly. This is called the attack phase. Immediately after the attack, the amplitude of the note quickly decays to a steady amplitude. As the bow continues to run across the string, this amplitude is held fairly constant. This is called the sustain phase. Finally, when the bow is taken off the string, the note releases and the amplitude falls back down to zero. The envelope generator multiplies the BRAM samples by different values, creating this envelope. However, there is no release phase, since the four instruments never stop playing in the Musical Feet System. A graph of the amplitude envelope applied to two consecutive notes is shown in Figure 7 below.

Figure 7. Amplitude envelope of two consecutive notes.

The envelope generator module is implemented using two FSM's. One controls the top-level behavior of the module, and the other keeps track of the envelope state: attack, decay, or sustain. The states of the top-level FSM will be discussed in detail.

#### 4.1.3.1 "Wait For Sample" State

The initial state of the FSM is the "wait for sample" state. In this state, the envelope generator waits for the oscillator to assert its ready signal. When the oscillator indicates that the new address is ready, the envelope generator reads the next sample out of the BRAM. It also checks the new\_note output of the instrument module. This indicates whether the new sample corresponds to a new pitch. If so, the envelope returns to the attack phase in order to attack the new note. After this, the FSM transitions to the next state.

#### 4.1.3.2 "Adjust Envelope" State

In the "adjust envelope" state, the envelope generator decides whether it needs to transition to a new envelope state. During the attack and decay phases, the module uses a counter to keep track of how much time has passed. These two phases both have fixed lengths, so the module checks if the timer has reached the appropriate length. If so, the envelope state transitions, either from attack to decay or from decay to sustain. If the envelope is in the sustain state, it will stay there until the new\_note signal is asserted. After the transition is decided, the FSM transitions again.

#### 4.1.3.3 "Apply Envelope" State

In the "apply envelope" state, the sample is actually scaled to the appropriate value. Depending on the envelope state, the scaling is calculated differently. In the attack state, the sample is multiplied by the value of the envelope timer and shifted right by 15 bits. Since the largest possible value of the envelope timer is  $2^{15}$ , the largest possible value of this scaling is 1. In the decay state, the sample is multiplied by the attack height ( $2^{15}$ ) minus the value of the timer and then shifted by 15 bits. After the scaling is done in both of these cases, the envelope timer is incremented.

The sustain state does not utilize the envelope timer, but it uses its own timer to add vibrato to the envelope. Vibrato is created when a string instrument player rolls his finger back and forth across the string, making both the frequency and amplitude of the pitch rapidly fluctuate. The vibrato applied in this module only causes the amplitude to fluctuate, and it is employed during the sustain phase. The sample is scaled by the attack height minus the decay height plus the value of the vibrato timer, and then it is shifted by 15 bits. After this, the vibrato timer is either incremented or decremented, depending on the vibrato direction. When the vibrato timer reaches its maximum value, the vibrato direction changes to down, and when the vibrato timer reaches 0, the direction changes to up. This causes the amplitude of the note to rapidly fluctuate up and down during the sustain phase. Note that this fluctuation is not depicted in Figure 7.

Once the sample is scaled, the FSM transitions to its final state.

#### 4.1.3.4 "Wait For Mixer" State

At this point, the envelope generator has successfully scaled the sample, so it sends out a ready signal to the mixer, which combines the signals sent by each of the four envelope generators. Once the mixer receives all four signals, it sends a received\_audio signal back to each envelope generator. When the envelope generator receives this signal, it transitions back to the "wait for sample" state.

#### 4.2 Mixer

The mixer module receives the scaled instrument samples from the four envelope generators and combines them into one signal to send to the AC97 DAC. It does this by simply adding together the four samples it receives. Once it receives ready signals from all four envelope generators, it starts adding up the samples. Since each sample is 16 bits wide, the mixer takes one clock cycle to add each one. If all four were added in the same clock cycle, timing constraints would be violated. Once all four signals are added, the mixer sends the received\_audio signal to each envelope generator and sends the combined 18-bit signal to the AC97 DAC.

#### 4.3 AC97 Driver

The AC97 driver converts the 18-bit digital audio signal sent by the mixer into an analog signal that can be outputted through speakers or headphones. The module is extremely similar to the 8-bit AC97 driver written by the 6.111 staff. There are only two minor changes. First, the AC97 input handling has been removed, since the Musical Feet system only has to provide the output. Second, the 8-bit signal that was padded with 12 zeros and set as the audio\_out\_data is now an 18-bit signal padded with 2 zeros. The same audio\_out\_data is still sent to both the left and right speakers.

## 4.4 Testing of Music Synthesis and Audio Modules

The testing of these modules was more difficult than other modules because they were all closely interdependent. They were first written and wired together, and then tested as a unit. There were two problems that became apparent during this testing.

At first, sound only came out when fewer than four instruments were sending their output signals into the mixer. This was caused by a timing constraint violation in the mixer, as there was not enough time in a single clock cycle to add four 16-bit numbers together. To fix this, the addition was split up into four clock cycles, adding one number per cycle. Afterwards, all four instruments could be heard at the same time.

Once all four pitches could be heard, it was apparent that the pitches deviated from the correct frequencies by a noticeable amount. This caused imperfect blending among the four instruments. To solve this problem, the oscillator intervals were extended to have more binary decimal places, resulting in a more accurate sampling frequency of the BRAMs. After this change, the music synthesis and audio modules behaved as expected.

## **5 Video Output Modules**

The video output of the Musical Feet system has two modes: the Music Information mode and the Visualization mode. The mode is set by a switch on the 6.111 Labkit, which determines whether the display pixel is taken from the Music Information module or the Visualization module. In the Music Information mode, the display shows the current tempo of the output music in beats per minute (BPM), and the music's current chord. In the Visualization mode, a footprint image appears and fades away each time a footstep is taken by the user, allowing the user to observe whether the system has registered his steps.

The output is shown on a 1024x768 XVGA display, which requires a 65MHz clock for a 60Hz refresh rate. Thus, all of the video output modules are clocked off a 65MHz clock signal produced by the 6.111 Labkit. Signals coming from modules clocked off the 27MHz signal are synchronized to the 65MHz clock before being used, and the digital pedometer signal from the Schmitt trigger inverter is filtered for 0.2 seconds off the 65MHz clock (Section 2.2, p. 3).

#### 5.1 XVGA Module

The XVGA module was written by the 6.111 staff. It generates the necessary horizontal and vertical sync signals, using counters to keep track of the horizontal and vertical coordinates of the current pixel. The sync signals are sent to the ADV7125 video DAC, while the count signals are used by the Music Information and Visualization modules.

## 5.2 Music Information Modules

The Music Information module takes synchronized data from the tempo generator and chord generator to display them on a monitor screen. It sends an output pixel value to the XVGA module based on the location of the current pixel. To produce the appropriate text, the Music Information module uses several submodules (Figure 7, p. 23).

## 5.2.1 String Display Module

The string display module was written by the 6.111 staff. Given horizontal and vertical coordinates, it produces the appropriate pixel values to display text input in the form of ASCII strings. Characters are produced based on a font ROM, which was written by Xilinx. The Music Information module uses four instances of the string display module to display "TEMPO:", the tempo in beats per minute (BPM), "CHORD:", and the key of the chord.

Figure 8. Block diagram of music information module.

#### 5.2.2 Cycles-to-Decimal BPM Converter

The tempo period produced by the tempo generator is in number of cycles of a 27MHz clock per beat. For the Music Information display, this number needs to be converted into beats per minute. Moreover, the number should be displayed as a decimal number. The cycles-to-decimal BPM converter achieves this by dividing the number of cycles of a 27MHz clock in one minute (1.62e9) by the tempo period. The division is carried out by continuously subtracting the tempo period from 1.62e9 until subtraction would yield a negative number. The quotient is the number of subtractions that were performed. This number is the tempo in beats per minute.

To convert this tempo to a decimal number, the converter first continuously subtracts 100 until the result is less than 100. The number of subtractions performed is equal to the hundreds digit of the decimal number. Similarly, 10 is then continuously subtracted, and then 1, to get the tens digit and the ones digit of the decimal number. Since the tempo is limited to 300 BPM by the pedometer data filter (Section 2.3, p. 4), three decimal digits will suffice for any valid tempo period.

#### 5.2.3 Decimal Digit-to-Character Converter

This module takes a decimal digit produced by the cycles-to-decimal BPM converter and outputs the corresponding 8-bit ASCII value, to be used in the string display module. For the hundreds digit, a value of 0 will produce a "" on the display, while a value of 0 for the tens or ones digit produce a "0" on the display.

#### 5.2.4 Chord-to-Characters Converter

This module takes the 5-bit chord output from the chord generator and outputs the corresponding ASCII value of the string, to be used in the string display module. The high order bit of the chord signal indicates the tonality, while the four low order bits encode the root note of the chord.

#### 5.3 Visualization Modules

The Visualization module contains two submodules, one that produces a left footprint and one that produces a right footprint. The module alternates between selecting the left and right footprint image pixels to send to the video output. Every time that the filtered pedometer signal asserts high, a white footprint is displayed on a black background and fades away. The location of the footprints on the screen is controlled by the Visualization module. They stay in the same horizontal positions, but their vertical positions are changed after each footstep, creating the image of feet walking forward and looping back to the bottom of the screen after they reach the top.

The Visualization module also has a 5-bit count signal that resets to 0 when a footstep is taken, increments when the vertical sync signal is asserted low, and stays at 31 when it is reached until the next footstep. This count is used by the footprint modules to fade the image of the footprints.

## 5.3.1 Footprint Modules

The left and right footprint modules are identical except that they contain BRAMs initialized with images of a left footprint and a right footprint, respectively. Each module keeps an address to its BRAM. The location of the image on the screen is given by the Visualization module. When the current pixel lies within the image's space, the footprint module outputs a pixel value based on the value at the BRAM's current address and increments the address. When the BRAM outputs a 0, the output pixel is black. When the BRAM output a 1, the output pixel is a shade of gray. The shade of gray is determined by setting the red, green, and blue pixel values to 248 minus the value of the count from the Visualization module times eight. Since the count ranges from 0 to 31, the pixel values range from 248 (nearly white) to 0 (black). Thus, the image fades completely after 31 low assertions of the vertical sync signal, which is about half a second.

## 5.4 Testing of Video Output Modules

The XVGA module and the other modules written by the 6.111 staff have been previously tested. The Music Information modules were tested by hardwiring numbers to the inputs of the converter modules and checking to see if the expected text was displayed on the screen. Then, the tempo generator and chord generator modules were hooked up to the inputs of the video modules, and the input of the tempo generator was hooked up to a Labkit button as described in Section 2.7. The values of the chord and tempo period signals were shown on the hex display and checked with the video output on the monitor to see if they matched. To test the Visualization modules, the signal that triggered footprints to appear was wired to a Labkit button. The expected pattern of footprints appeared.

#### 6 Conclusion

The Musical Feet system differs from previous music generation systems in two innovative ways. First, the user has some degree of control over the music output through the speed of his footsteps, which allows for interesting possibilities. The system can provide auditory feedback of the user's walking and running paces, which could be useful for recognizing fatigue during athletic training. Also, it provides an entertaining form of exercise. Once the entire system was put together, it was used by several subjects, all of whom greatly enjoyed the novel experience.

Second, the Musical Feet system is unique in that it improvises its own music in real time instead of playing recorded samples. Not only does this significantly save memory, it also provides an interesting experience for the user. Adding randomness to the improvisation also prevents the user from hearing the same music each time he uses the system.

As described in previous sections, each part of the system was thoroughly tested for full functionality. Once the entire system was put together, further tests were performed. The audio and video outputs behaved as expected based on the user footstep input, and the music composition produced aurally pleasing music. During the course of this testing, one problem that did occur was in the initialization of the block RAMs containing the string samples. Occasionally, some of the block RAMs would be initialized with noisy samples, which resulted in a static-filled or distorted output sound. This problem could usually be resolved by restarting the 6.111 Labkit and reloading the Verilog code onto the FPGA.

The Musical Feet system has great potential for further improvement. The video output modules can be expanded to produce significantly flashier visualizations. The string sample BRAMs could contain longer samples so that the low frequency components of the sound waveforms are not lost. In addition, there could be direct control of the music volume based on the speed of the user's footsteps. Many parameters in the system can be tweaked to conform to each user's preferences, such as the tonality threshold and the envelope amplitude parameters. More advanced musical techniques can be replicated, such as different note articulations being imposed by the envelope generators. In an exercise setting, it may be helpful to have the music tempo slightly exceed the user's pace, encouraging the user to run faster. Another useful improvement for an exercise setting would be to provide a wireless interface between the pedometer and the 6.111 Labkit. Right now, the wires attached to the pedometer limit the user to walking or running in place, while a wireless interface would give users free rein to walk or run around while using the system.

## 7 References

### String samples:

- University of Iowa Musical Instrument Samples: http://theremin.music.uiowa.edu/MIS.html

- Fitchsound Free Cello Samples http://fitchsounds.com/freestuff.html

### Audio synthesis:

- MATLAB Help Desk: http://www.mathworks.com/access/helpdesk/help/toolbox/filterdesign/ref/

- The Amateur Gentleman's Introduction to the Principles of Music Synthesis: http://beausievers.com/synth/synthbasics/

- Articulation and Vibrato on the Violin: http://www.phys.unsw.edu.au/jw/violinarticulation.html

## 8 Appendix A: Verilog – Pedometer Input Processing Modules

### 8.1 Pedometer Data Filter

```

// ped filter.v

// Author: Rajeev Nayak

// The ped filter module filters the pedometer signal, ignoring all

// enables within .2 seconds of the first one.

module ped_filter #(parameter DELAY=5400000) // .2 sec with a 27Mhz clock

(input reset,

input clock,

input noisy,

output reg clean);

reg [23:0] count;

reg waiting;

always @(posedge clock) begin

if (reset) begin

count <= 0;

waiting <= 1;</pre>

clean <= noisy;</pre>

end

else if (waiting) begin

clean <= 0;

if(count == DELAY) waiting <= 0;</pre>

else count <= count + 1;</pre>

else if (noisy) begin

clean <= 1;</pre>

waiting <= 1;</pre>

count <= 0;

end

end

endmodule

```

## 8.2 Tempo Generator

```

// Tempo Generator Module

// Author: Harley Zhang

// Takes one-bit input from pedometer filter and calculates tempo periods

module tempo_gen (input reset,

input clock,

input ped enable,

output reg tempo ready,

output reg [31:0] tempo period);

wire [31:0] count;

reg [32:0] calc period = 0;

buffer reset = 1;

reg

counter reset = 0;

reg

busy = 0;

reg [31:0] buffer[7:0];

reg [2:0] buff addr = 0;

reg [2:0] addr offset = 0;

counter 32 counter(.reset(counter_reset),.clock(clock),.count(count));

always @(posedge clock) begin

if (reset) begin

// System reset

buffer_reset <= 1;</pre>

counter reset <= 1;</pre>

calc period <= 0;</pre>

busy <= 0;

buff addr <= 0;</pre>

addr offset <= 0;

tempo ready <= 0;

end

else if (ped enable) begin

// First cycle of footstep

busy <= 1;

tempo ready <= 0;</pre>

counter reset <= 1;</pre>

buffer_reset <= 0;</pre>

if (buffer reset) begin

// For first footstep, fill all buffer locations with the count

buffer[0] <= count;</pre>

buffer[1] <= count;</pre>

buffer[2] <= count;</pre>

buffer[3] <= count;</pre>

buffer[4] <= count;</pre>

buffer[5] <= count;</pre>

buffer[6] <= count;</pre>

buffer[7] <= count;</pre>

end

else begin

// For subsequent footsteps, write over current buffer location

buffer[buff addr] <= count;</pre>

```

```

buff addr <= buff addr + 1;</pre>

end

end

else if (busy) begin

// Use eight clock cycles to calculate tempo period

addr offset <= addr offset + 1;</pre>

counter reset <= 0;

buffer reset <= 0;</pre>

if (addr_offset == 3'b111) begin

// Finished calculating tempo_period

busy <= 0;

tempo ready <= 1;</pre>

tempo_period <= ((calc_period >> 1) + buffer[buff_addr +

addr offset]) >> 1;

calc period <= 0;</pre>

end

else begin

calc period <= (calc period >> 1) + buffer[buff addr +

addr offset];

busy <= 1;

tempo ready <= 0;</pre>

end

end

else begin

tempo ready <= 0;</pre>

counter_reset <= 0;</pre>

buffer_reset <= 0;</pre>

end

end

endmodule

```

## 8.3 Tonality Generator

```

// Tonality Generator Module

// Author: Harley Zhang

// Takes tempo period from tonality generator module whenever

// it is ready, and then uses logic to determine tonality bit

module tonality_gen (input reset,

input clock,

input tempo ready,

input [31:0] tempo period,

output reg tonality);

parameter threshold = 33'h40FFFF;

reg [32:0] calc tonality = 0;

reg [31:0] prev tempo period;

buffer reset = 1;

rea

busy = 0;

reg

reg [31:0] buffer[7:0];

reg [2:0] buff_addr = 0;

reg [2:0] addr offset = 0;

always @(posedge clock) begin

if (reset) begin

// System reset

buffer reset <= 1;</pre>

calc tonality <= 0;</pre>

busy <= 0;

buff addr <= 0;

addr offset <= 0;

end

else if (tempo ready) begin

busy <= 1;

buffer_reset <= 0;</pre>

prev tempo period <= tempo period;</pre>

if (buffer reset) begin

buffer[0] <= 0;

buffer[1] <= 0;

buffer[2] <= 0;

buffer[3] \leftarrow 0;

buffer[4] <= 0;

buffer[5] <= 0;

buffer[6] <= 0;

buffer[7] <= 0;

end

else begin

// For subsequent tempos, write over current buffer location

buffer[buff addr] <= (prev tempo period > tempo period) ?

prev tempo period - tempo period :

tempo period - prev tempo period;

buff addr <= buff addr + 1;</pre>

end

end

```

```

else if (busy) begin

// Use eight clock cycles to calculate calc tonality

addr_offset <= addr_offset + 1;</pre>

buffer reset <= 0;</pre>

if (addr offset == 3'b111) begin

// Finished calculating calc tonality

tonality <= ((calc tonality >> 1) +

buffer[buff_addr + addr_offset]) < threshold;</pre>

// If the weighted average of the differences exceeds or equals

// the threshold, tonality is 0, which is minor. Otherwise, it

is

// 1, which is major.

calc_tonality <= 0;</pre>

busy <= 0;

end

else begin

calc_tonality <= (calc_tonality >> 1) +

buffer[buff addr + addr offset];

busy <= 1;

end

end

else begin

buffer reset <= 0;</pre>

end

end

endmodule

```

## 8.4 Beat Generator

```

// Beat Generator Module

// Author: Harley Zhang

// Takes tempo period from tonality generator module

// and generates corresponding single-cycle enable signal

module beat_gen (input reset,

input clock,

input tempo ready,

input [31:0] tempo period,

output reg beat);

reg counter reset = 0;

reg [31:0] prev tempo period = 32'hFFFFFFFF;

wire [31:0] count;

counter 32 counter(.reset(counter reset),.clock(clock),.count(count));

always @(posedge clock) begin

if (reset) begin

counter_reset <= 0;</pre>

beat <= 0;

prev tempo period <= 32'hFFFFFFF;</pre>

end

else if (tempo_ready) begin

// Read in new tempo period when ready

prev tempo period <= tempo period;</pre>

end

else if (count >= prev tempo period) begin

// Assert output high and reset counter when desired count is

// reached or surpassed

counter_reset <= 1;</pre>

beat <= 1;

end

else begin

counter reset <= 0;</pre>

beat <= 0;

end

end

endmodule

```

## 9 Appendix B: Verilog – Music Composition Modules

### 9.1 Random Number Generator

```

// Author: Rajeev Nayak

// The random module generates a 2-bit pseudorandom number using a

// 10-bit Fibonacci linear feedback shift register.

module random (input clock,

input reset,

output [1:0] rand);

reg [9:0] seed;

reg [9:0] value;

wire next;

always @(posedge clock) begin

// create a "random" seed by incrementing on every clock cycle

// starting at system reset

seed <= seed + 1;</pre>

if(reset) begin

// on the user reset, set the LFSR value to the current seed

// value if the seed is 0, assign the value to 1

if(seed == 0) value <= 1;

else value <= seed;

end

else begin

// shift the register

value[0] <= value[1];</pre>

value[1] <= value[2];</pre>

value[2] <= value[3];</pre>

value[3] <= value[4];</pre>

value[4] <= value[5];</pre>

value[5] <= value[6];</pre>

value[6] <= value[7];</pre>

value[7] <= value[8];</pre>

value[8] <= value[9];</pre>

value[9] <= next;</pre>

end

end

// calculate the next value for the high-order bit using a Fibonacci

// LFSR polynomial

assign next = value[0] ^ value[3];

// assign the output to be the low-order 2 bits of the LFSR value

assign rand = value[1:0];

endmodule

```

## 9.2 Chord Generator

```

// chord generator.v

// Author: Rajeev Nayak

// The chord generator module uses an FSM to choose a chord

// based on the previous chord and the current tonality.

module chord generator (input clock,

input reset,

input beat,

input tonality,

input [1:0] rand,

output [4:0] chord,

output reg chord ready);

parameter S_I = 0; // major tonic chord

parameter S IV = 1; // major subdominant chord

parameter S_V = 2; // major dominant chord

parameter S i = 3; // minor tonic chord

parameter S iv = 4; // minor subdominant chord

parameter S v = 5; // minor dominant chord

reg[3:0] key; // the current key of the music

reg[2:0] state;

always @(posedge clock) begin

if(reset) begin

key \ll 0;

state <= S I;</pre>

chord ready <= 0;

end

// turn the chord ready signal off after 1 cycle

else if(chord ready) chord ready <= 0;</pre>

// transition between chords on every beat

else if (beat) begin

case (state)

S I: begin

state <= tonality ?</pre>

(rand[0] ? (rand[1] ? S V : S IV) : S I) :

(rand[0] ? (rand[1] ? S v : S i) : S iv);

// key changes to iv on the S I->S i transition

if(~tonality && rand[0] && ~rand[1]) begin

if(key \geq= 7) key \leq= key - 7;

else key \ll key + 5;

end

end

S IV: begin

state <= tonality ?</pre>

(rand[0] ? (rand[1] ? S I : S IV) : S V) :

(rand[0] ? S v : S i);

// key changes to vi on the S IV->S i transition

if(~tonality && ~rand[0]) begin

if(key >= 3) key <= key - 3;

else key <= key + 9;

```

```

end

end

S V: state <= tonality ?

(rand[0] ? S I : S V) :

(rand[0] ? S v : S i);

S i: begin

state <= tonality ?</pre>

(rand[0] ? (rand[1] ? S_I : S_IV) : S_V) :

(rand[0] ? (rand[1] ? S_v : S_iv) : S_i);

// key changes to III on the S i->S I and S i->S IV

transitions

if(tonality && rand[0]) begin

if(key >= 9) key <= key - 9;

else key \leq key + 3;

end

end

S iv: state <= tonality ?

(rand[0] ? S_I : S_V) :

(rand[0] ? (rand[1] ? S i : S iv) : S v);

S v: state <= tonality ?

(rand[0] ? S I : S V) :

(rand[0] ? S i : S v);

default: state <= S_I;</pre>

endcase

// assert that the new chord is ready

chord ready <= 1;</pre>

end

end

// assign the tonality of the chord based on the state

assign chord[4] = state == S I || state == S IV ||

state == SV \mid | state == Sv;

// assign the root note of the chord based on the state and key

assign chord[3:0] = (state == S I || state == S i) ? key :

((state == S_IV || state == S_iv) ?

((\text{key} >= 7) \ ? \ \text{key} - 7 : \text{key} + 5) :

((key >= 5) ? key - 5 : key + 7));

```

endmodule

### 9.3 Note Generator

```

// note generator.v

// Author: Rajeev Nayak

// The note generator module chooses four notes for a string quartet

// based on the chord produced by the chord_generator.

module note generator(input clock,

input reset,

input chord ready,

input [4:0] chord,

input [1:0] rand,

output [4:0] cel note,

output [4:0] vla note,

output [4:0] vln2 note,

output [4:0] vln1 note);

// states for the note search

parameter S WAIT FOR CHORD = 0;

parameter S CEL UP INITIALIZE = 1;

parameter S CEL SEARCH_UP = 2;

parameter S CEL DOWN INITIALIZE = 3;

parameter S CEL SEARCH DOWN = 4;

parameter S VLA UP INITIALIZE = 5;

parameter S VLA SEARCH UP = 6;

parameter S_VLA_DOWN_INITIALIZE = 7;

parameter S_VLA_SEARCH_DOWN = 8;

parameter S_VLN2_UP_INITIALIZE = 9;

parameter S_VLN2_SEARCH_UP = 10;

parameter S VLN2 DOWN INITIALIZE = 11;

parameter S VLN2 SEARCH DOWN = 12;

parameter S VLN1 UP INITIALIZE = 13;

parameter S VLN1 SEARCH UP = 14;

parameter S VLN1 DOWN INITIALIZE = 15;

parameter S_VLN1_SEARCH_DOWN = 16;

parameter S FINISH = 17;

// note counter state

parameter S ROOT = 0;

parameter S THIRD = 1;

parameter S FIFTH = 2;

// notes found in the previous search

reg [5:0] prev cel;

reg [5:0] prev vla;

reg [5:0] prev vln2;

reg [5:0] prev vln1;

// notes in the current search

reg [5:0] temp cel;

reg [5:0] temp vla;

reg [5:0] temp vln2;

reg [5:0] temp vln1;

// temporary registers for note search

reg [5:0] lower note; // stores the lower neighbor note in each

```

```

// instrument's search

reg [1:0] lower note type;

reg [1:0] same note_type;

reg [5:0] higher note; // stores the higher neighbor note in each

// instrument's search

req [1:0] higher note type;

reg [1:0] last note type;

reg [2:0] note found; // keeps track of which notes have been found in

// each instrument's search:

// 0=lower note, 1=same note, 2=higher note

reg [1:0] note type available[2:0]; // keeps track of which notes have

// been assigned:

// 0=root, 1=third, 2=fifth

reg [4:0] search state;

// temporary registers for the note counter

reg [5:0] note counter; // keeps track of the current note candidate

reg [1:0] counter state;

always @(posedge clock) begin

if(reset) begin

temp cel <= 9;

temp vla <= 13;

temp_vln2 <= 9;

temp vln1 <= 14;

prev cel <= 12;

prev vla <= 28;

prev vln2 <= 31;

prev vln1 <= 36;</pre>

search state <= S WAIT FOR CHORD;</pre>

counter_state <= S_ROOT;</pre>

end

else begin

case(search state)

// wait for the next chord to be chosen

S WAIT FOR CHORD: begin

if(chord ready) search state <= S CEL UP INITIALIZE;</pre>

end

// based on the chord, set the note counter to the

// lowest possible note for the cello

S CEL UP INITIALIZE: begin

// initialize the note counter

// major chord

if(chord[4]) case(chord[3:0])

4'd0: begin

note_counter <= 6'd4;</pre>

counter_state <= S_THIRD;</pre>

end

4'd1: begin

note counter <= 6'd5;</pre>

counter state <= S THIRD;</pre>

end

4'd2: begin

note counter <= 6'd6;</pre>

counter state <= S THIRD;</pre>

```

```

end

4'd3: begin

note counter <= 6'd3;</pre>

counter state <= S ROOT;</pre>

end

4'd4: begin

note counter <= 6'd4;</pre>

counter state <= S ROOT;</pre>

end

4'd5: begin

note counter <= 6'd5;</pre>

counter state <= S ROOT;</pre>

4'd6: begin

note counter <= 6'd6;</pre>

counter state <= S ROOT;</pre>

end

4'd7: begin

note counter <= 6'd7;

counter_state <= S_ROOT;</pre>

end

4'd8: begin

note counter <= 6'd8;

counter state <= S ROOT;</pre>

end

4'd9: begin

note counter <= 6'd9;

counter_state <= S_ROOT;</pre>

end

4'd10: begin

note_counter <= 6'd10;</pre>

counter_state <= S_ROOT;</pre>

end

4'd11: begin

note counter <= 6'd3;</pre>

counter state <= S THIRD;</pre>

end

default: begin

note counter <= 6'd4;

counter state <= S THIRD;</pre>

end

endcase

// minor chord

else case(chord[3:0])

4'd0: begin

note counter <= 6'd3;</pre>

counter state <= S THIRD;</pre>

end

4'd1: begin

note counter <= 6'd4;</pre>

counter state <= S THIRD;</pre>

end

4'd2: begin

note counter <= 6'd5;

counter state <= S THIRD;</pre>

end

4'd3: begin

```

```

note counter <= 6'd3;</pre>

counter state <= S ROOT;</pre>

4'd4: begin

note counter <= 6'd4;

counter state <= S ROOT;</pre>

4'd5: begin

note counter <= 6'd5;</pre>

counter state <= S ROOT;</pre>

end

4'd6: begin

note counter <= 6'd6;</pre>

counter state <= S ROOT;</pre>

end

4'd7: begin

note counter <= 6'd7;</pre>