# Voice-Controlled Chess Game on FPGA Using Dynamic Time Warping

Varun Chirravuri, Michael Kuo

### **Project Abstract**

Most modern digital chess games employ a mouse and keyboard based user interface. We change this paradigm by designing an FPGA based, voice-controlled, chess game. We will train the game to recognize specified voice commands from the players. We will use dynamic time warping to compare real-time speech samples to the trained command templates to determine what move a player wishes to make. The game will be displayed on a VGA display with all the functionality of a standard chess game.

| Table of Contents                                              |    |

|----------------------------------------------------------------|----|

| VOICE-CONTROLLED CHESS GAME ON FPGA USING DYNAMIC TIME WARPING | i  |

| Project Abstract                                               | i  |

| Table of Figures                                               |    |

| Overview                                                       | 1  |

| Audio Recognition Hardware                                     | 1  |

| Chess Hardware                                                 | 2  |

| Keyboard Input                                                 | 2  |

| Chess Engine                                                   | 2  |

| Graphics Engine                                                | 3  |

| Description                                                    | 3  |

| Input                                                          | 3  |

| Audio Recognition Hardware                                     | 3  |

| DTW System Controller                                          | 4  |

| Dynamic Time Warping Engines                                   | 7  |

| Valid Checker                                                  |    |

| Finite Impulse Response Filter                                 | 11 |

| Shift Connector                                                | 11 |

| Chess Hardware                                                 | 12 |

| Keyboard Input                                                 | 12 |

| Keyboard Entry                                                 | 12 |

| Keyboard Encoder                                               | 13 |

| Chess Engine                                                   | 13 |

| Chess Engine                                                   | 14 |

| Move Checker                                                   | 15 |

| Graphics Engine                                                | 16 |

| Chessboard Drawer                                              | 16 |

| Chess Pieces Drawer                                            | 17 |

| Text Drawer                                                    | 18 |

| Chess Graphics                                                 | 18 |

| Testing and Debugging                                          | 18 |

| Audio Recognition Hardware                                     |    |

| DTW Engine                                                             | 19  |

|------------------------------------------------------------------------|-----|

| DTW System Controller                                                  | 20  |

| System Integration                                                     | 20  |

| Proof of Concept Testing                                               | 20  |

| Chess Hardware                                                         | 21  |

| Conclusion                                                             | 22  |

| Appendices                                                             | 23  |

| Appendix A : Single DTW Test Data "Funk" v "Bridge" and "Cat" v "Dog"  | 23  |

| Appendix B: Letter Hit Frequency Data                                  | 25  |

| Appendix C: Shift Connector Verilog                                    | 28  |

| Appendix D: FIR 31 Verilog                                             | 30  |

| Appendix E: DTW Engine Verilog                                         | 33  |

| Appendix F: DTW System Controller + Valid Checker Verilog              | 38  |

| Appendix G: Modified Lab 4 W/ Instantiated Modules + Debouncer Verilog | 46  |

| Appendix H: Labkit File for Chess System                               | 62  |

| Appendix I: Keyboard Entry                                             | 74  |

| Appendix J: Keyboard Encoder                                           | 76  |

| Appendix K: Chess Engine                                               | 81  |

| Appendix L: Move Checker                                               | 88  |

| Appendix L: Chessboard Drawer                                          | 97  |

| Appendix M: Chess Pieces Drawer                                        | 98  |

| Appendix N: Text Drawer                                                | 102 |

| Appendix O: Chess Graphics                                             | 108 |

| Appendix P: MATLAB IPG to COE                                          | 111 |

## **Table of Figures**

| Figure 1. High Level Block Diagram Of Entire System                        | 1  |

|----------------------------------------------------------------------------|----|

| Figure 2. Top level block diagram of chess system                          | 2  |

| Figure 3. Move command encoding                                            | 3  |

| Figure 4. Block Diagram Of Audio Recognition Hardware                      | 4  |

| Figure 5. Outer FSM of the DTW System Controller                           | 5  |

| Figure 6. Inner FSM of the DTW System Controller.                          | 7  |

| Figure 7. Diagram of the DTW Engine                                        | 8  |

| Figure 8. Dynamic Time Warping Engine FSM                                  | 10 |

| Figure 9. Block diagram of keyboard input component                        | 12 |

| Figure 10. Block diagram of chess engine component                         | 13 |

| Figure 11. State diagram of chess engine FSM                               | 14 |

| Figure 12. Graphics produced by the graphics engine                        | 16 |

| Figure 13. Text types. Labels are red. Column and row indicators are green | 17 |

| Figure 14. "Dog" and "Cat" when trained on "Dog"                           | 21 |

| Figure 15. "Bridge" and "Funk" when trained on "Funk"                      | 21 |

#### Overview

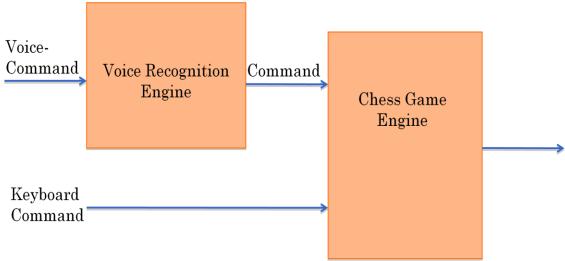

The complete system takes in voice commands and keyboard inputs to control a chess game displayed on an XVGA display. The system is divided into two components: audio recognition hardware and chess hardware.

Figure 1. High Level Block Diagram Of Entire System

#### **Audio Recognition Hardware (Varun)**

The audio recognition hardware is in charge of handling all of the audio processing and calculations associated with the voice-recognition portion of the chess game. Employing a series of finite state machines and the dynamic time warping algorithm to compare audio samples, the system correctly determines which move the user wishes to make in the chess game, and sends that information to the chess engine to execute.

Incoming audio streams are down-sampled and filtered to reduce the aliasing effects caused by the down-sampling. The filtered audio stream is then sent to a valid-checking module that determines whether a valid word has indeed been spoken or if the incoming audio is simply background noise. When the checking module detects a valid word, the system begins actively recording the audio stream. A one-half second audio clip is stored into memory, and then streamed down to the dynamic time warping engines.

There are a total of eight dynamic time warping (DTW) engines. Once trained, each engine contains audio-templates corresponding to one of the eight letters (A-H), and one of the eight numbers (1-8) that specify all possible positions on the board. Depending on where in the command sequence the user is when the valid sample is detected, the incoming audio streamed is compared to either all eight numbers or all eight numbers, once comparison per engine.

The DTW engines use the dynamic time warping algorithm to compare the samples. The algorithm uses dynamic programming to correct for temporal differences between stored samples and the valid sample, and returns a value corresponding to the error between the samples. The template belonging to the engine that returns the lowest error for a given audio input is determined to be the intended number or letter. Once four such commands are issued, the system concatenates the results as a complete command consisting of two numbers and two letters and sends the information to the chess engine.

#### **Chess Hardware (Michael)**

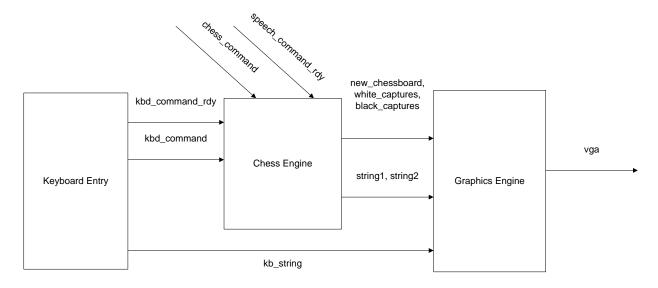

The chess system is an implementation of a two-player chess game on the 6.111 LabKit. It receives move instructions from either the voice recognition system or a keyboard, checks that instructed moves are permissible, and displays the chessboard and chess pieces on an XVGA display. The three main components of the chess system, as illustrated in the figure below, are the keyboard input, the chess engine, and the graphics engine.

Figure 2. Top level block diagram of chess system.

#### **Keyboard Input**

The keyboard input component encodes keyboard input into a move command that is passed to the chess engine.

#### **Chess Engine**

The chess engine directs the flow of the chess game. It keeps track of the turn, determines if instructed moves from the voice recognition system or keyboard input are permissible, and manages the internal representation of the chessboard and the chess pieces on the board.

#### **Graphics Engine**

The graphics engine generates video images for the chess game to be displayed on the XVGA display. The video images include the chessboard and the chess pieces on the board, a grid of the pieces that each player has captured, as well as text from the chess engine and keyboard input.

#### **Description**

#### Input (Michael)

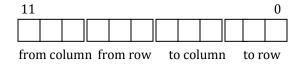

In order to modularize the voice recognition system and the chess system, a unified encoding scheme was defined for all move commands passed to the chess engine. The encoding of the move command is composed of the column and row (file and rank) of the square containing the piece being moved and the column and row of the square where the piece is being moved.

Figure 3. Move command encoding.

The chessboard is a square board of eight columns and eight rows of squares. The columns, which are lettered A through H are encoded with 0 through 7, and the rows, which are numbered 1 through 8 are also encoded with 0 through 7. The complete encoding of the move command is twelve bits – three bits for each of the columns and rows of the original square and destination square of the piece being moved.

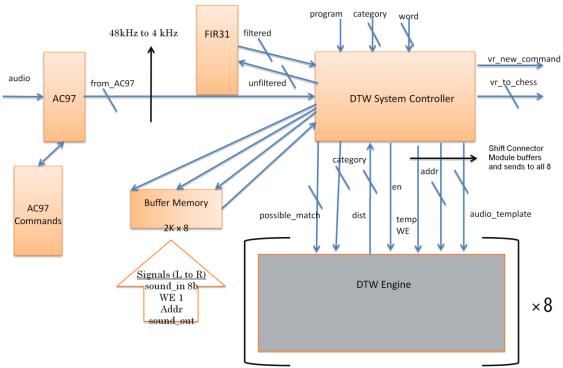

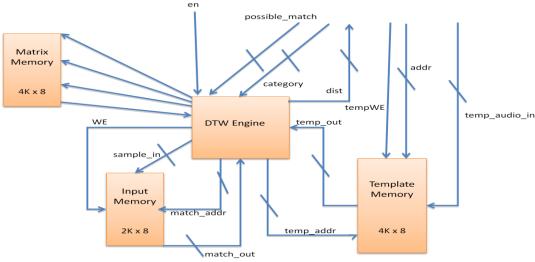

#### **Audio Recognition Hardware (Varun)**

Audio is sent to the audio recognition hardware from the AC97 codec found in the 6.111 lab 4 documents. Audio is sampled from the headphones at 48 kHz and sent from the codec directly to the Audio Recognition Hardware. The hardware consists of five modules, listed in the order of complexity: the DTW System Controller, DTW Engines, Valid Detector, Finite Impulse Response Filter, and the Shift Connector. Because of the many modules involved in processing incoming audio, a complex signaling and handshaking system was used to ensure data was not lost, and was processed in the correct order.

Figure 4. Block Diagram Of Audio Recognition Hardware.

#### **DTW System Controller**

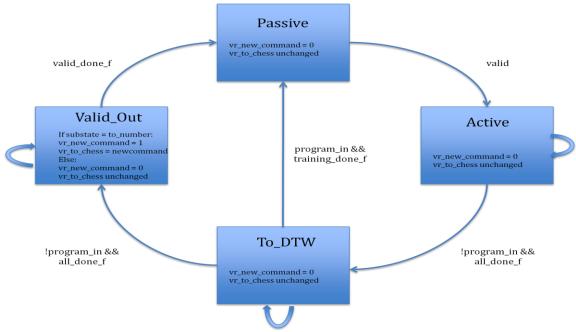

The DTW System Controller controls the flow of data through the entire system, and therefore contains the most complexity. It is implemented as two nested finite state machines. The outer most FSM is in charge of capturing incoming data, sending valid samples to the DTW Engines, and then interpreting the error values returned by the DTW Engines to output the correct command to the chess module. The inner FSM is used to determine which section of the command the user is inputting (<code>from\_letter</code>, <code>from\_number</code>, <code>to\_letter</code>, or <code>to\_number</code>) and if a complete command has been issued and is ready to be outputted. The next state and next substate are determined combintationally, with state being updated to reflect the next state at the following clock edge.

Figure 5. Outer FSM of the DTW System Controller.

#### **Outer FSM**

#### **Passive State**

The outer FSM has four states: passive, active, to\_DTW, and valid\_out. The default state of the machine is passive. In this state, audio is downsampled from the 48 kHz sampling rate of the AC97 codec to 4 kHz. Audio is only sampled when users press the record button, indicating that they wish to record audio. Incoming audio is immediately sent to the anti-aliasing filter to correct for the error induced by downsampling. The filter output is then stored in a 2048 x 8 bit BRAM (incoming audio is 8 bits wide). The BRAM stores approximately half a second of audio, and is used like a circular buffer when in the passive state. Whenever a sample is written to memory, an enable pulse is sent to the Valid\_Checker module along with the current sample being written. The Valid\_Checker outputs a valid signal whenever a valid word is spoken. Because the valid-checking module outputs a valid pulse only after there is a noticeable increase in the amplitudes of the previous 128 samples, a start\_val pointer is updated to point 128 memory locations behind the current location being written to. As soon as a valid signal is outputted, the FSM switches to the active state.

#### **Active State**

The job of the *active* state is to continue downsampling and recording audio until a complete, half-second audio segment is written to memory. While downsampling, and filtering occur just as in the *passive* state, the *start\_val* and *end\_val* pointers are no longer updated. Enable signals are no longer sent to the *Valid\_Checker* as we have already recording a valid word. Writing to memory continues and incrementing the address continues until a sample is written to the *end\_val* address. At this point, the system asserts a flag (*end\_record\_f*) letting the system know a half-second word has

been recorded. Once this flag goes high, *to\_DTW* is assigned to next state, and becomes the state on the following clock cycle.

#### To DTW State

Upon entering the *to\_DTW* state, the end record flag is reset to zero and the memory address is set to the sample-starting pointer, *start\_val*. Over the next 2048 clock cycles, all 2048 audio samples stored in the *Controller's* memory are outputted to one of two audio output channels depending on whether the system is training the DTW Engines or if it is sending then possible match audio to compare against their templates.

If the user is training the system and the *train\_in* switch is set high, then a write enable signal (*temp\_WE*) is outputted to the DTW Engines. When training, users use switches to choose which category they are training (letters or numbers) and which word (1-8 or A-H) they wish to train. This data is outputted via the 3 bit *word\_out* and 1 bit *category\_out* registers, which are combinationally assigned to the value selected by the user. The flag *training\_done\_f* is raised to indicate that training is complete, and nextstate is set to *passive*, so the system can accept a new training sample or a command.

If the user is not training the device, the match write enable is raised instead of the template write enable, signalling to the DTW engines that the incoming audio sample is a possible match and should be compared to the stored template. The system remains in the *to\_DTW* state until all 8 of the DTW engines signal that they have finished their calculations and have returned a valid *distance* value. When this happens, the *all\_done\_f* flag is raised and the system moves the *valid out* state.

#### Valid Out State

The *valid\_out* state compares the *distance* values returned by the DTW Engines and determines which trained template most closely matched the inputted audio. To prevent any timing issues, and to reduce redundancy, the system sequentially calculates the minimum of the 8 returned value in 4 clock cycles. In the first three clock cycles, the system performs four, two, and one comparison respectively to determine which DTW Engine returned the lowest distance. The number of the DTW Engine with the lowest distance is stored. On the fourth clock cycle, a *valid\_done\_f* flag is raised, indicating all comparisons are done, and setting the state back to *passive*. The number of the register with the lowest distance is stored as the intended letter/number (1-8, A-H). If all four parts of the complete command have been determined, the complete command is sent to the chess engine along with a signal *vr\_new\_command* which signals that a new command has indeed been sent.

Figure 6. Inner FSM of the DTW System Controller.

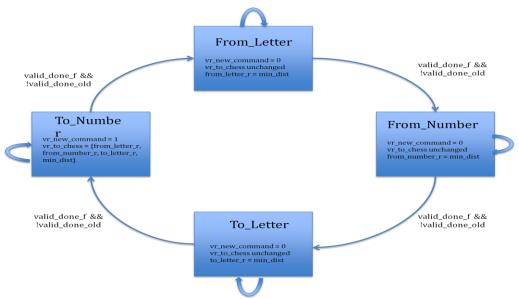

#### Inner FSM

The inner FSM is in charge of determining which element of the complete command the current input corresponds to, and is much simpler than the outer FSM. All state changes occur at the positive edge of the <code>valid\_out\_f</code> flag—that is, once the previous section of the command, or the previous command has successfully been computed. The states correspond to each section of the complete command – the letter and number coordinates of the piece to be moved (<code>from\_letter</code>, <code>from\_number</code>), and the letter and number coordinates of the location the piece is to be moved to (<code>to\_letter</code>, <code>to\_number</code>). Because the last section of a command is the number of the square where the piece should be moved, commands are only outputted when the inner FSM is in the <code>to\_letter</code> substate and the outer FSM is in the <code>valid\_out</code> state. The sequential nature of the inner FSM ensures that the entire command is specified once the system reaches this overall state.

#### **Dynamic Time Warping Engines**

The Dynamic Time Warping Engines use a dynamic programming to remove temporal differences between audio samples and compare how closely they match. For instance, if a speaker says the word "book" twice, it is highly unlikely that the time-domain waveforms of the words will correspond—it is more likely that one of the two times the word will be spoken slower or faster than the other. Algorithms that just match time-domain samples cannot correct for this difference, and so an algorithm like dynamic time warping is used.

Figure 7. Diagram of the DTW Engine.

#### **Dynamic Time Warping Algorithm**

The DTW algorithm is fairly straightforward. Take two data series, X and Y, of length m and n respectively. Create an  $m \times n$  matrix D, where the element  $D_{ij}$  represents the squared difference between the  $i^{th}$  sample of X and the  $j^{th}$  sample of Y. That is:

$$D_{ij} = (X_i - Y_j)^2$$

for  $0 \le i \le m$  and  $0 \le j \le n$

From this matrix, we then solve the dynamic programming problem of the shortest path from  $D_{00}$  to  $D_{mn}$  by creating a second m+1 x n+1 matrix Y. The values of Y are computed as such:

$$Y_{ij} = D_{i-1,j-1} + min(Y_{i-1,j}, Y_{i,j-1}, Y_{i-1,-1j})$$

for  $1 \le i \le m+1$  and  $1 \le j \le n+1$  with  $Y_{0,j} = Y_{i,0} = \infty$ ,  $Y_{1,1} = D_{0,0}$  and  $Y_{0,0} = 0$

Thus, every value  $\Upsilon_{ij}$  represents the shortest "error path" found from the first element of D to the current element. So it stands that, once the algorithm completes,  $\Upsilon_{m+1,n+1}$  will be the shortest "error path" that exists between the two samples. So, for example, if the word "book" is said once at a normal pace, and once twice as slow, the algorithm will traverse  $\Upsilon$  precisely on the diagonal with a slope of 2, accruing no error as it traverses, and will indicate that the words are an exact match.

#### **Dynamic Time Warping Implementation**

The main challenge with porting the DTW algorithm into hardware is that assuming that the samples are of length m and n with each sample having width b, the overall memory needed will be m\*n\*b bits. At 2048 8-bit samples per audio segment, running 8 DTW Engines on the FPGA would exceed the memory available. To work around this limitation, a simple solution was chosen. At each iteration of the algorithm, only two rows of  $\Upsilon$  are ever needed to compute the current element. So

instead of needing to store 2048\*2048\*8 bits of data, the algorithm would only need 2048\*2\*8 bits or memory, which is feasible. Also, the algorithm must keep 4 data registers to hold the 4 values needed to compute the next value of the matrix  $(D_{i-1,j-1}, Y_{i-1,j}, Y_{i,j-1}, Y_{i-1,-1j})$ .

To do this, the DTW Engine keeps two counters, one that is 11 bits and one that is 22 bits. At each iteration of the algorithm, both counters are incremented. The first counter rolls back to 0 once it has reached 2047, and so it is used to indicate where in the row the algorithm is. The other counter increments until it reaches the value 4,194,303, which indicates that the algorithm has computed all of the values of  $\Upsilon$ .

The algorithm then moves sequentially, with each iteration taking 5 clock cycles. On the first clock, if the value of element (i,j) is being computed, the algorithm decrements the memory address for the DTW pseudo-matrix memory by 2047, so that it loads the value of the (i,j-1) on the third clock. On the second clock, it pulls the value for the  $i^{th}$  element of the template and the  $j^{th}$  element of the inputted sample and stores their difference to a register. On the third clock cycle, the previous value of (i,j) is loaded into the register for (i,j-1), the previous value of (i-1,j) is loaded into the register for (i-1,j-1), and the value coming out of the DTW memory is loaded into the (i-1,j) register. Essentially, the frame of reference for the computation shifts right. Also on the third clock cycle, the value  $D_{ij}$  is computed by squaring the difference found in the second clock cycle, and storing that back into the same register. The DTW memory address is also set to point to the next location in memory to store the (i,j) <sup>th</sup> value in two clock cycles.

A simple speedup that was used reduced the number of comparisons needed in the next clock cycle was to store the minimum of the (i,j) and (i-1,j) elements and storing that instead of shifting the values in those registers into the other registers and finding the minimum of three values on the next clock.

On the third clock cycle, the algorithm performs all of the comparisons, and computes the value for the next (i,j) value. If the 22 bit counter is at zero, it simply loads the  $D_{ij}$  value into the (i,j) register. If the 22 bit counter is less than 2047, the algorithm is still computing the first row of the matrix and so (i,j) is the sum of  $D_{ij}$  and (i,j-1). When the 11 bit counter is 0 but the 22 bit counter is not 0, the algorithm is computing the first column, so (i,j) is the sum of  $D_{ij}$  and (i-1,j). Otherwise (i,j) is computed as the sum of  $D_{ij}$  and the minimum of (i-1,j) and the "speedup" register mentioned in the previous paragraph. Once the 22 bit counter reaches its maximum value, the algorithm has finished computing, and the current value of  $D_{ij} + (i,j)$  represents the minimum "distance" between the samples. At each iteration both counters are incremented. At every pass, the address to the possible match BRAM is incremented, and only when the 11 bit counter is zero and the 22 bit is not zero is the address to the template BRAM incremented.

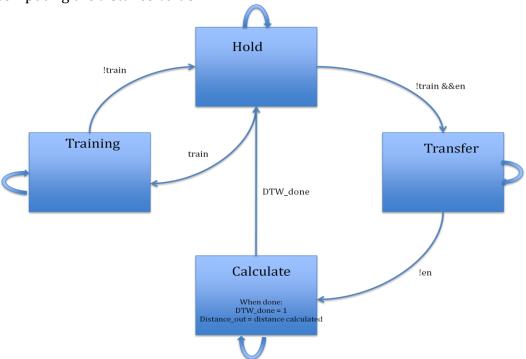

#### **DTW Engine FSM**

To allow for the DTW Engine to be trained, to take in template samples, and to compute the distance between samples and a template, an FSM is implemented. It has four states: hold, training, transfer, and calculate. When in the hold state, the FSM simply waits for either a training enable or a transfer enable from the DTW System Controller. If in training, the engine uses the category bit from the System Controller to determine whether to store the sample in the first 2048 memory locations, or in the last 2048 memory locations in its template BRAM—0 is for letter and is stored in the first 2048, 1 is for number and is stored in the last. Similarly, when in the transfer and calculate states, it uses the same category bit to determine which template to compare the input against. Once a template is fully transferred to the BRAM, the system depends on the train from the *Controller* to fall to move into the hold state. When in the transfer state, the system depends on the enable signal from the *Controller* to go low to move into the *calculate* state, where the above calculations are performed. Once completed, the system outputs a *DTW done* signal, and outputs the calculated distance value. The DTW holds its outputs for 3 clocks cycles, and completely wipes the DTW pseudo-matrix memory after it has finished computing the *distance* value.

Figure 8. Dynamic Time Warping Engine FSM.

#### **Valid Checker**

The valid checker algorithm samples the audio stream coming into the *System Controller* to determine whether a word is being spoken. It uses a 256 x 8 bit register partitioned into two 128 halves. The register array is used as a FIFO buffer. At each clock, when an enable is issued from the *Controller*, the *valid checker* takes the audio input sent to it, calculates its absolute value, and then adds it to the tail of

the array. Three values are always maintained – the index of the current sample, the 256th sample, and the 128th sample. Initially all registers in the array are set to zero. Two sum counters, first and last, are set to zero as well. When a new sample arrives, it is inserted into the array, and its absolute value is added to the last sum counter. The value of the old 128th sample is subtracted from that sum counter, and added to the other. The value of the old 256th sample is subtracted off of the first sum counter. The indices of the 128th and 256th values are moved back to indicate that the frame of reference as shifted. As this repeats and the buffer fills up, the values of the sum counters reflect the sum of the first 128th and last 128th samples. When the value of sum last exceeds the value of sum first by some margin that was empirically determined, the valid checker outputs a *valid* signal, and then clears the register array as well as the sum first and sum last counters in preparation for the next time the *System Controller* enters the *passive* state.

#### **Finite Impulse Response Filter**

The FIR filter used here was the same 31 tap FIR filter designed in 6.111 lab 4, with the filter coefficients modified to represent the change in downsampling rate. It is implemented with a circular register array to hold audio samples, and an accumulator that performs the necessary convolution multiplication between *ready* signals from the AC97 codec to output filtered data to the *DTW System Controller*.

#### **Shift Connector**

The *shift connector* module sits between the *DTW System Controller* and all of the DTW Engines. When the *System Controller* sends train signals to the engines, the shift connector uses the word outputted by the *System Controller* to determine which of the 8 engines should receive the training enable pulse and the template audio. The *shift connector* has the important function of allowing the *System Controller* and the *DTW Engine* to communicate as state machines, without having to assign outputs at different times to compensate for the one clock lag of changing state. There is a one-clock lag from when the DTW Engine receives an enable pulse and changes state to training or transfer, to when it actually accepts audio data in the new state. So without the *shift connector*, the DTW Engine would drop the first audio sample from the *System Controller*. To avoid this, the *shift connector* extends the enable/train from the *System Controller* by one clock cycle, and holds each audio sample being streamed down for one clock cycle, padding the first, dropped packet with a 0 value.

#### **Chess Hardware (Michael)**

#### **Keyboard Input**

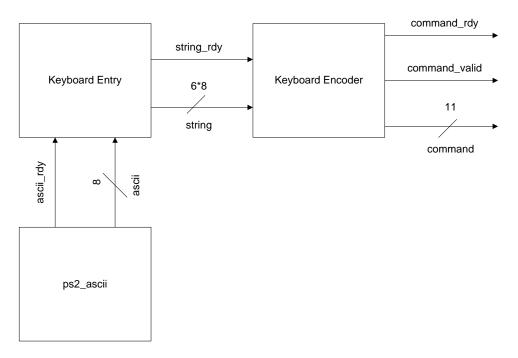

The keyboard input component consists of two modules: keyboard entry and keyboard encoder. A block diagram containing the two modules is illustrated in the figure below.

Figure 9. Block diagram of keyboard input component.

#### **Keyboard Entry**

The keyboard entry module packages inputs from the keyboard into strings of ASCII code to be encoded into move commands. Professors Ike Chuang's and Chris Terman's  $ps2\_kbd\ module^1$  is used to convert scan codes generated by the keyboard into ASCII codes. An array stores the ASCII codes as keys are pressed – up to five codes, as five ASCII characters is enough to issue a keyboard move instruction. Keyboard move instructions take the form

<from column><from row>\_<to column><to row>

(e.g. "A2 A3"). Pressing the Backspace key deletes the last stored ASCII code stored in the array – functionally similar to pressing the Backspace key in a word processor. Pressing the Enter key locks the array of ASCII codes for one clock cycle and signals on the same clock cycle that a string of ASCII code is ready to be

<sup>&</sup>lt;sup>1</sup> http://web.mit.edu/6.111/www/f2005/code/ps2\_kbd.v

encoded. Afterwards, the array is cleared to allow new ASCII codes for new move commands to be stored.

#### **Keyboard Encoder**

The keyboard encoder module encodes the string of ASCII code received from the keyboard entry module into a 12-bit move instruction using the encoding scheme described previously. Each ASCII code is encoded if it corresponds to a valid letter or number, depending on its position in the string. The rightmost and forth-from-right ASCII codes in the string should each correspond to one of the letters from A through H, the second-from-right and leftmost ASCII codes in the string should each correspond to one of the numbers from 1 through 8, and the third-from-right ASCII code in the string should correspond to a whitespace. The overall encoding is valid if the above criteria are met. A one clock cycle ready signal is raised once encoding is complete or the string of ASCII code has been determined to be invalid – a valid signal is raised at the same time if the overall encoding is actually valid.

#### **Chess Engine**

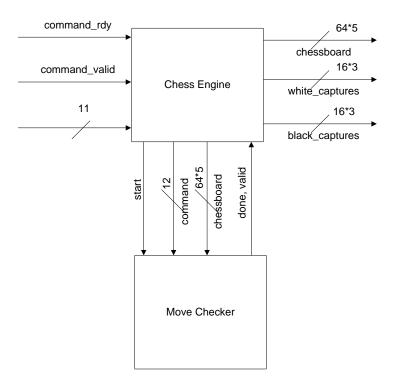

The chess engine component consists of two modules: chess engine and move checker. A block diagram containing the two modules is illustrated in the figure below.

Figure 10. Block diagram of chess engine component.

#### **Chess Engine**

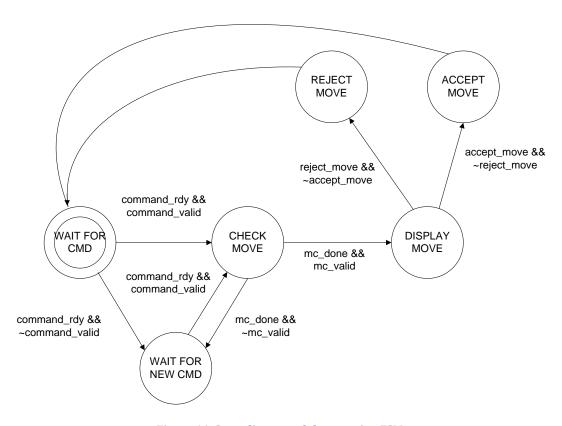

The chess engine module is an FSM that directs the play of the chess game and manages the internal representation of the chessboard. Its states and transitions are illustrated in the figure below.

Figure 11. State diagram of chess engine FSM.

The FSM starts in the state WAIT FOR CMD, with a register indicating the current player initialized to WHITE. Two switches on the 6.111 LabKit are used to select the input signals for the two players. If the input is the voice recognition module, then the chess engine will wait for a ready signal from that. Otherwise it will wait for a ready signal from the keyboard encoder. On a ready signal from the voice recognition module, the FSM will direct the start of move checking to determine if the instructed move is permissible. On a ready signal from the keyboard encoder, the FSM will check that the encoding was valid before signaling the start of the move checker. An invalid encoding will land the FSM in the state WAIT FOR NEW CMD, which is also the state that the FSM transitions to if the move checker decided that an instructed move is impermissible. However, if the move checker determines that the instructed move is valid, the chess engine will update the internal representation of the chessboard – a multidimensional array of registers – to reflect the move in the state DISPLAY MOVE.

Because the voice recognition module is not expected to generate the correct move instruction all of the time, the chess engine keeps a second copy of the chessboard to allow the players (regardless of their input type) to review their moves. The two copies of the chessboard are designated old-chessboard and new-chessboard. Moves are always made to new-chessboard first. If a player rejects a move, then the two affected squares of new-chessboard are replaced with the values in the corresponding squares of old-chessboard. On the other hand, if a player accepts the move, then the two affected squares of new-chessboard are copied over to old-chessboard. Once a player accepts the move, his or her turn is over (the register indicating the current player switches to the other player), and the two chessboards are made identical by the start of the next player's turn.

The chess engine also handles pawn promotions, as well as outputs text to be displayed on the XVGA screen. When pawns have reached the other side of the chessboard, they are, due to design limitations, automatically promoted to queens. The chess engine outputs text to let the players know whose turn it is, as well as direct them as they play the game.

#### **Move Checker**

The move checker module determines whether an instructed move is valid according to the style of movement of the piece being moved. The move checker first determines the type of piece being moved by looking at the square in new-chessboard corresponding to the from-column and from-row specified in the move instruction. If there is a piece in the square, then the move checker verifies that it belongs to the current player, as well as verifies that the destination square, corresponding to the to-column and to-row specified in the move instruction, is empty or contains an opponent's piece. Only then does it check to see that the instructed move matches the style of movement of the piece being moved. Descriptions of each piece's style of movement are listed below.

| Piece  | Style of Movement                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| King   | One square in any direction                                                                                                                                                                                        |

| Queen  | Up to seven squares in any direction if its path is unhindered                                                                                                                                                     |

| Rook   | Up to seven squares horizontally or vertically if its path is unhindered                                                                                                                                           |

| Bishop | Up to seven squares diagonally if its path is unhindered                                                                                                                                                           |

| Knight | L-shaped – two squares horizontally or vertically, then one square vertically or horizontally, respectively                                                                                                        |

| Pawn   | Generally, one square up the rows for WHITE and down the rows for BLACK, but can advance two squares in the same manner on the piece's first move – captures are made one square in the forward diagonal direction |

For queens, rooks, and bishops, the move checker directs a sub-module to iterate through the squares along its path of movement to determine if the path is clear or blocked by another piece. Otherwise, the move checker uses combinational logic to determine if a piece's movement matches its prescribed style of movement. The move checker signals for one cycle that it is done if a move instruction is determined to be valid or as soon as it is determined to be invalid. A valid signal is raised at the same time if the move instruction is valid.

#### **Graphics Engine**

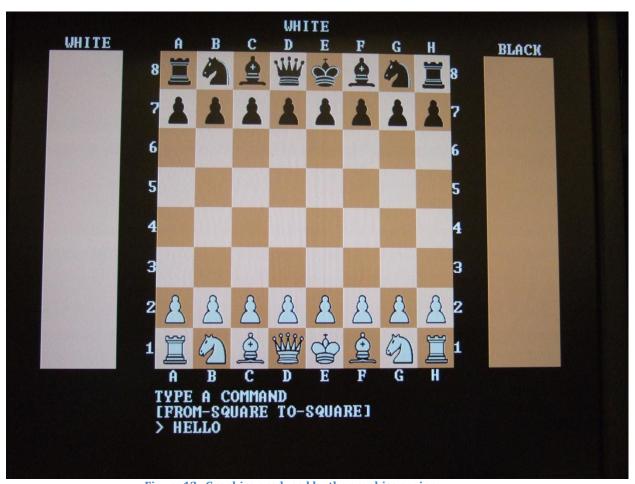

The graphics engine produces the visual aspects of the chess game, pictured in the figure below.

Figure 12. Graphics produced by the graphics engine.

#### **Chessboard Drawer**

Chessboard drawer generates the pixel values needed to render a chessboard on the XVGA display. The width of each square of the chessboard is 64 pixels, so within the bounds of the chessboard, the chessboard drawer uses only the higher order bits of normalized hount and vocunt signals to determine which of the two parameterized color values to output.

#### **Chess Pieces Drawer**

Chess pieces drawer generates the pixel values needed to render images of chess pieces on the XVGA display. Twelve images of the six types of pieces in white and black were obtained from Wikipedia. Using GIMP, the backgrounds of these images were filled with solid blue and the images were converted into .jpg files. A MATLAB script (Appendix P) was then used to generate .coe files from the .jpg files. The .coe files were then analyzed to determine what values the originally solid blue had become. Those values of blue are used as transparent colors.

Twelve ROMs for the chess piece images are instantiated in the chess pieces drawer. All twelve ROMs are addressed by the five lower order bits of normalized hount and vount signals. The data out from a specific ROM is selected if a corresponding piece needs to be drawn at the location specified by hount and vount. Otherwise, the module generates the pixel value corresponding to a blue transparent color. The pixel values from the ROM and the blue transparent color are 8-bits (3-bits red, 3-bits green, 2-bits blue), so they are upconverted into 24-bit values by padding with zeros.

Figure 13. Text types. Labels are red. Column and row indicators are green.

#### **Text Drawer**

Text drawer generates all the pixel values for text to be rendered on the XVGA display. The text to be rendered is divided into three types; labels, column and row indicators for the chessboard, and body text. As indicated in the figure above, the labels include the headers for the grids of captured pieces as well as the turn indicator above the chessboard. Column and row indicators are the letters and numbers surrounding the perimeter of the chessboard. These indicators make it easier for the players to specify columns and rows in making moves. Body text consists of two lines of text from the chess engine and text from the keyboard entry module. The texts of each type are all the same length. Labels read either "WHITE" or "BLACK", which are five characters each. Column and row indicators are single characters. The actual lines of body text and text from the keyboard entry module vary, but are each padded to be 32 characters long. In order to render the three different types of text, three instances of Professors Ike Chuang's and Chris Terman's cstringdisp<sup>2</sup> module are instantiated with the appropriate parameter values. Since the text is designed to have no overlap, the outputs from the three cstringdisp modules are composed into one output by taking the bitwise OR of the three signals.

#### **Chess Graphics**

The chess graphics module combines the outputs from the chessboard drawer, the chess pieces drawer, the text drawer, as well as two solid-colored rectangles generated by the  $blob^3$  module from Lab 5, to produce the final output to be displayed on the XVGA display. The chessboard, text, and solid-colored rectangles are designed so that they do not overlap. Thus, the outputs from chessboard drawer, text drawer, and two blobs can be combined simply by performing a bitwise OR on the four. The chess pieces produced by the chess pieces drawer, however, are intended to layer on top of the chessboard and the two solid colored rectangles. In terms of layering, the chess pieces make up the top layer and everything else make up the bottom layer. The graphics module displays the top layer when there are chess pieces to be displayed and the bottom layer otherwise. To accomplish this, the chess graphics module allows the bottom layer to filter through when pixel values in the top layer correspond to the blue transparent colors.

#### **Testing and Debugging**

#### **Audio Recognition Hardware (Varun)**

Debugging the Audio Recognition hardware initially done entirely in ModelSim, and once the ModelSim tests were satisfactory, the modules were debugged and tested on hardware. To develop solid testing practices and to build awareness of common mistakes that were being made, an informal bug log was kept for the first week of ModelSim testing. The shift connector, finite impulse response filter, and valid

<sup>&</sup>lt;sup>2</sup> http://web.mit.edu/6.111/www/f2005/code/cstringdisp.v

<sup>&</sup>lt;sup>3</sup> http://web.mit.edu/6.111/www/f2008/handouts/labs/lab5.html

checker modules were relatively easy to debug. They each required only ModelSim verification before being shown to work up to specification on hardware. For the valid checker, additional testing on hardware was done to find the optimal threshold at which to acknowledge a valid word was spoken. It was integrated into the 6.111 lab4 audio recorder<sup>4</sup> and fed incoming audio streams with varying thresholds. The goal was to systematically determine what threshold provided the highest hit rate for spoken words while minimizing the rate of false positives (ie. prevent short audio bursts like claps from being acknowledged as valid words).

#### **DTW Engine**

The first stage of testing the DTW involved performing a proof of concept test on the DTW algorithm. For that, a version of the algorithm quickly scripted in Python was fed a series of audio test vectors and shown to perform satisfactorily. After this was shown, the algorithm was examined rigorously to find where improvements could be made to reduce memory requirements. At this stage, it would have been very beneficial to build a MATLAB or Python simulation of the hardware-optimized algorithm to ensure that no unforeseen errors could occur, but luckily careful planning was all that was necessary.

Once the frameworks for the algorithm were written in Verilog, they were run over and over again in ModelSim. Trying to pipeline the circuit for increased computational throughput created the biggest problem. This caused serious problems because of the necessary accesses to different parts of the DTW Memory. Eventually this was scrapped in favor of a sequential approach. While the sequential approach required almost six times as many clock cycles to complete as a working pipelined version would have, the incremental gain in time would have been imperceptible. Finally a version of the algorithm was shown to work on known test vectors in ModelSim and hardware testing began.

The first problem noticed when testing on hardware began almost immediately. When fed any audio samples, the algorithm would return a distance metric that hovered around a value that seemed linked to the template audio. That is, when the template audio was very loud, the distance returned would be very large, and vice versa. Using the Logic Analyzer, it was found to be a problem with state. The <code>DTW\_done</code> signal was not being reset fast enough so as soon as the System Controller would move into the <code>to\_DTW</code> state, it would see the done signal high, and only have one clock cycle to send data before its FSM would move it to the next state – meaning that the DTW Engine would compare the template against an audio sample with one valid input and the rest zeros.

The second major problem had to do with how the engine handled audio inputs. In simulation, test vectors were chosen to be unsigned integer values. As such, the algorithm code never specified that the audio samples should be treated as signed integers, and so seemingly small negative numbers were viewed as large positive

<sup>4</sup> http://web.mit.edu/6.111/www/f2008/handouts/labs/lab4.v

numbers. So while the algorithm continued to produce the proper values when hardwired to positive constants, when fed audio, the values that were being computed were absurd. Luckily, the fix was relatively simple—just adding the word signed to the Verilog.

#### **DTW System Controller**

The DTW System Controller was initially written in pseudo code on paper and then refined to be as robust as possible. Once the pseudo code was written, it was translated into Verilog and tested top to bottom. First, its ability to transition between states with proper input sequences was tested. At the same time, the system was shown not to glitch when many inputs arrived simultaneously, and instead dealt with them sequentially as it was supposed to.

After state transitions were tested, enable pulse timings were tested and debugged. Because the entire system has so many parts that depend on exact timing and transfer of data, this step was very important.

Next to be tested was the audio buffering and transfer procedure. The address incrementing and memory storage/output were examined to show that no data was being truncated, lost, or written improperly.

Once this was done, the system was ready to be tested on hardware, with DTW\_done pulses controlled by switches and distance values set to by switches. The states, substates, and outputted commands were displayed on the hex display using the module provided in the 6.111 lab documentation. Because of the ModelSim testing, this phase only took a few hours to debug the entire controller system.

#### **System Integration**

Because the input/output and handshaking behavior of each module were understood from their individual ModelSim simulations, whole system integration was not too challenging. It was first done in ModelSim and shown to work. The ModelSim model was then compiled to hardware. After fixing the bug caused by not clearing the DTW\_done signal before the *System Controller* reached the *to\_DTW* state—which took three days to catch—and after losing a day to not specifying the proper bit width of an output, the system worked as hoped.

#### **Proof of Concept Testing**

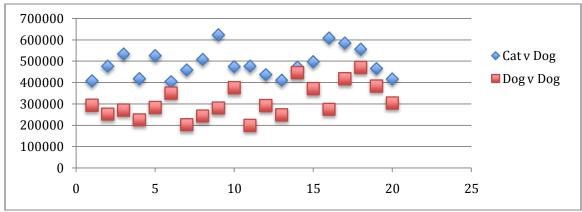

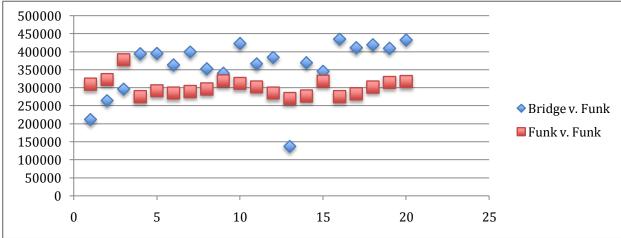

Once the system was running, the performance of one single DTW Engine was tested. While the engine had trouble distinguishing between words like "alpha" and "beta", it was shown to be able to distinguish between "funk" and "bridge" when trained on "funk", and between "cat" and "dog" when trained on "dog" as can be seen in Figures 14 and 15 (data for "cat v dog" and "funk v bridge", see Appendix A). Further testing revealed on the entire system with all 8 DTW Engines showed that the system had between a 3% and 12% hit rate when matching complete chess commands to human voices—and had an almost 90% hit rate when trying to distinguish a spoken number 5 (See Appendix B).

The errors with the system are almost entirely due to the variable nature of human voice, as well as the environmental noise of the training and testing environment. When a computer generated voice was used to train the system and then inputted as test audio, the computer had a 100% hit rate – indicating that it could successfully match perfect signals. Furthermore, when the audio was sped up or slowed down by up to 12%, the algorithm still exhibited a 95% hit rate. This indicates that the DTW algorithm was, in fact, performing dynamic time warping successfully.

Figure 14. "Dog" and "Cat" when trained on "Dog".

Figure 15. "Bridge" and "Funk" when trained on "Funk".

#### **Chess Hardware (Michael)**

Testing of the modules of the chess system was done either by visual inspection or by simulating using ModelSim. The keyboard entry and the graphics engine modules were tested by loading up the LabKit and checking the visual output on the XVGA display. Since the keyboard encoder and move checker had no visual components, they were tested in ModelSim. Problems were usually caught by checking the Warning messages in the Xilinx tool, as well as by carefully analyzing and reanalyzing the Verilog code that had been written. However, I did come upon an odd bug that took the help of Ben to resolve – at one point, my project file could not be opened by Xilinx, and any attempts to create a new project from the old Verilog

file resulted in Xilinx closing unannounced. After numerous attempts at creating new projects and copying various fragments of code into to Xilinx, Ben noticed that a *localparam* had been assigned to itself. Sure enough, this circular assignment was the cause of the mysterious problem.

#### Conclusion

The Voice Controlled Chess Game built on the FPGA was successfully shown to demonstrate full chess visualizations and game play, as well as sufficient voice recognition capability.

The voice recognition hardware was shown to be a successful implementation of the Dynamic Time Warping algorithm. Controlling for the effects of environment noise and audio pitch, the system was able to detect and match input audio samples of varying rates of up to 15% from the trained sample. It also demonstrated that the DTW algorithm, which is normally thought to be memory inefficient, could be built in a way so as to preserve the functionality while greatly curbing memory usage.

The system's inability to reliably detect microphone inputs can be attributed to the shortcomings of comparing unfiltered time series of audio instead of converting audio streams features vectors that emphasize spoken voice and normalize for the speaker's pitch and amplitude. One such technique involves using Mel-cepstral coefficients to scale the Fourier Transform of incoming audio before passing these new scaled feature-vectors to the DTW Engine. This has been implemented on FPGAs and shown to perform better than the system implemented in this project.

The chess hardware was successfully implemented on the FPGA. Capable of taking both keyboard and speech commands, it can function both independently and as a part of the voice controlled chess system. The chess hardware features basic move checking – checking that moves match the style of movement of a piece. Thus, it does have a number of limitations, preventing it from functioning as a full-fledged chess system. Due to design limitations, the chess system does not allow a number of special moves, namely, en passant captures and castling. Pawn promotion is also limited to queens. Regardless of these shortcomings in the chess engine, the chess hardware is still complete, taking moves and displaying them on screen.

The Voice Controlled Chess Game is fully functional, although there are features that we would have liked to implement.

## **Appendices**

Appendix A: Single DTW Test Data "Funk" v "Bridge" and "Cat" v "Dog"

|                                                                                                        | Cat v Dog      |                                                                                                                                |                                                                                                                   | Dog v D | _       |                                                                                                                                |

|--------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                        | 6360E          |                                                                                                                                | 407054                                                                                                            |         | 47889   | 293001                                                                                                                         |

|                                                                                                        | 74628          | 3                                                                                                                              | 476712                                                                                                            | 3D6D3   |         | 251603                                                                                                                         |

|                                                                                                        | 8255D          |                                                                                                                                | 533853                                                                                                            | 420F0   |         | 270576                                                                                                                         |

|                                                                                                        | 65E4C          |                                                                                                                                | 417356                                                                                                            | 36CDE   |         | 224478                                                                                                                         |

|                                                                                                        | 806ad          |                                                                                                                                | 525997                                                                                                            | 44E5F   |         | 282207                                                                                                                         |

|                                                                                                        | 628BA          |                                                                                                                                | 403642                                                                                                            |         | 55812   | 350226                                                                                                                         |

|                                                                                                        | 6FFAB          |                                                                                                                                | 458667                                                                                                            | 3148A   |         | 201866                                                                                                                         |

|                                                                                                        | 7C193          |                                                                                                                                | 508307                                                                                                            | 3B28B   |         | 242315                                                                                                                         |

|                                                                                                        | 9830C          |                                                                                                                                | 623372                                                                                                            |         | 44706   | 280326                                                                                                                         |

|                                                                                                        | 73B0A          |                                                                                                                                | 473866                                                                                                            | 5B9CF   |         | 375247                                                                                                                         |

|                                                                                                        | 7455F          |                                                                                                                                | 476511                                                                                                            |         | 30770   | 198512                                                                                                                         |

|                                                                                                        | 6A867          |                                                                                                                                | 436327                                                                                                            |         | 47119   | 291097                                                                                                                         |

|                                                                                                        | 6434D          |                                                                                                                                | 410445                                                                                                            | 3C9A3   |         | 248227                                                                                                                         |

|                                                                                                        | 731C7          |                                                                                                                                | 471495                                                                                                            | 6CDF4   |         | 445940                                                                                                                         |

|                                                                                                        | 796A4          |                                                                                                                                | 497316                                                                                                            | 5A901   |         | 370945                                                                                                                         |

|                                                                                                        | 94692          | <u>)</u>                                                                                                                       | 607890                                                                                                            |         | 43061   | 274529                                                                                                                         |

|                                                                                                        | 8EC7E          |                                                                                                                                | 584830                                                                                                            |         | 66072   | 417906                                                                                                                         |

|                                                                                                        | 87AE8          |                                                                                                                                | 555752                                                                                                            | 72C33   |         | 470067                                                                                                                         |

|                                                                                                        | 7193C          |                                                                                                                                | 465212                                                                                                            | 5D8AB   |         | 383147                                                                                                                         |

|                                                                                                        | 65A2C          |                                                                                                                                | 416300                                                                                                            | 4A219   |         | 303641                                                                                                                         |

| Mean                                                                                                   | 487545.2       | 2                                                                                                                              |                                                                                                                   | 30      | 08792.8 |                                                                                                                                |

| Median                                                                                                 | 475188.5       | 5                                                                                                                              |                                                                                                                   |         | 286652  |                                                                                                                                |

| Std Dev                                                                                                | 67004.73487    | 7                                                                                                                              |                                                                                                                   | 7915    | 7.35594 |                                                                                                                                |

| Bridge v Fur<br>33f16<br>40b71<br>488a1<br>607a7<br>60b37<br>58dbf<br>61af2<br>564ad<br>675e1<br>599e9 | 53533          | 212758<br>265073<br>297121<br>395175<br>396087<br>363967<br>400114<br>353453<br>341299<br>423393<br>367081                     | Funk v<br>4be07<br>4efd1<br>5c625<br>436b9<br>476b1<br>45de4<br>46e06<br>488d1<br>4e272<br>4c6a9<br>49f7c         | runk    |         | 310791<br>323537<br>378405<br>276153<br>292529<br>286180<br>290310<br>297169<br>320114<br>313001<br>302972                     |

| 5dfda<br>21afd<br>5a56a<br>548f7<br>6a5a0<br>6423c<br>69d0d<br>33f16<br>40b71<br>488a1<br>607a7        | 64846<br>66826 | 384986<br>137981<br>370026<br>346359<br>435616<br>411718<br>419878<br>410172<br>433421<br>212758<br>265073<br>297121<br>395175 | 45d59<br>423f5<br>43d37<br>4de76<br>436cd<br>4551a<br>49e9d<br>4d0e9<br>4dada<br>4be07<br>4efd1<br>5c625<br>436b9 |         |         | 286041<br>271349<br>277815<br>319094<br>276173<br>283930<br>302749<br>315625<br>318170<br>310791<br>323537<br>378405<br>276153 |

| 60b37 | 396087 | 476b1 | 292529 |

|-------|--------|-------|--------|

| 58dbf | 363967 | 45de4 | 286180 |

**Appendix B: Letter Hit Frequency Data**

| spoken | received | frequency |

|--------|----------|-----------|

| a      | a        | 0.31      |

| a      | b        | 0.02      |

| a      | С        | 0.09      |

| a      | d        | 0.00      |

| a      | е        | 0.10      |

| a      | f        | 0.12      |

| a      | g        | 0.06      |

| a      | h        | 0.30      |

| b      | a        | 0.00      |

| b      | b        | 0.30      |

| b      | С        | 0.10      |

| b      | d        | 0.00      |

| b      | е        | 0.00      |

| b      | f        | 0.10      |

| b      | g        | 0.00      |

| b      | h        | 0.40      |

| С      | a        | 0.00      |

| С      | b        | 0.20      |

| С      | С        | 0.00      |

| С      | d        | 0.00      |

| С      | e        | 0.20      |

| С      | f        | 0.10      |

| C      | g        | 0.30      |

| С      | h        | 0.20      |

| d      | a        | 0.20      |

| d      | b        | 0.00      |

| d      | С        | 0.00      |

| d      | d        | 0.00      |

| d      | e        | 0.50      |

| d      | f        | 0.00      |

| d      | g        | 0.00      |

| d      | h        | 0.30      |

| e      | a        | 0.30      |

| e      | b        | 0.00      |

| e      | c        | 0.00      |

| e      | d        | 0.00      |

| e      | e        | 0.40      |

| e      | f        | 0.10      |

| e      | g        | 0.00      |

| е      | h<br>h   | 0.20      |

| f      | a        | 0.33      |

| f      | b        | 0.00      |

| f      | С        | 0.22      |

| f      | d        | 0.00      |

| f      |          | 0.00      |

| f      | e<br>f   | 0.00      |

| f      |          | 0.00      |

| ı      | g        | 0.00      |

| _             |               |      |

|---------------|---------------|------|

| f             | h             | 0.44 |

| g             | a             | 0.00 |

| g             | b             | 0.20 |

| g             | c<br>d        | 0.10 |

| g             |               | 0.00 |

| g             | e             | 0.20 |

| g             | f             | 0.00 |

| g<br>-        | g<br>L        | 0.00 |

| g             | h             | 0.40 |

| h             | a             | 0.00 |

| h             | b             | 0.60 |

| h             | C             | 0.00 |

| h             | d<br>-        | 0.00 |

| h<br>•        | e<br>•        | 0.10 |

| h             | f             | 0.30 |

| h             | g             | 0.00 |

| h             | h             | 0.00 |

| 1             | 1             | 0.61 |

| 1             | 2             | 0.13 |

| 1             | 3             | 0.01 |

| 1             | 4             | 0.14 |

| 1             | 5             | 0.08 |

| 1             | 6             | 0.01 |

| 1             | 7             | 0.01 |

| 1             | 8             | 0.01 |

| 2             | 1             | 0.00 |

| 2             | 2             | 0.70 |

| 2             | 3             | 0.00 |

| 2             | 4             | 0.10 |

| 2             | 5             | 0.00 |

| 2             | 6<br>7        | 0.20 |

| 2             |               | 0.00 |

| 3             | 8             | 0.00 |

|               |               | 0.00 |

| 3             | 2             | 0.20 |

| 3             | 3             | 0.30 |

| 3             | 4             | 0.00 |

| 3             | 5             | 0.10 |

| <b>3</b> 3    | <b>6</b><br>7 | 0.30 |

|               |               | 0.10 |

| 3 4           | 8             | 0.10 |

|               | 1             | 0.00 |

| 4             | 2             | 0.60 |

| 4<br><b>4</b> | 3             | 0.10 |

| 4             | 4             | 0.30 |

| 4             | 5             | 0.00 |

| 4             | 6             | 0.00 |

|               | 7             | 0.00 |

| 4             | 8             | 0.00 |

| 5             | 1             | 0.00 |

| 5 | 2 | 0.00 |

|---|---|------|

| 5 | 3 | 0.00 |

| 5 | 4 | 0.10 |

| 5 | 5 | 0.90 |

| 5 | 6 | 0.00 |

| 5 | 7 | 0.00 |

| 5 | 8 | 0.00 |

| 6 | 1 | 0.00 |

| 6 | 2 | 0.00 |

| 6 | 3 | 0.00 |

| 6 | 4 | 0.30 |

| 6 | 5 | 0.10 |

| 6 | 6 | 0.50 |

| 6 | 7 | 0.00 |

| 6 | 8 | 0.00 |

| 7 | 1 | 0.00 |

| 7 | 2 | 0.40 |

| 7 | 3 | 0.00 |

| 7 | 4 | 0.20 |

| 7 | 5 | 0.20 |

| 7 | 6 | 0.00 |

| 7 | 7 | 0.10 |

| 7 | 8 | 0.00 |

| 8 | 1 | 0.10 |

| 8 | 2 | 0.20 |

| 8 | 3 | 0.00 |

| 8 | 4 | 0.10 |

| 8 | 5 | 0.10 |

| 8 | 6 | 0.50 |

| 8 | 7 | 0.00 |

| 8 | 8 | 0.00 |

#### **Appendix C: Shift Connector Verilog**

```

module shift_connector(

clock, reset, cat_in,word_in,

train_in, train_audio_in,

en_in, audio_in,

en_out, audio_out,

cat_out, train_audio_out,

train_1, train_2, train_3, train_4,

train_5, train_6, train_7, train_8);

input wire clock;

input wire reset;

input wire cat_in;

input wire [2:0] word_in;

input wire train_in;

input wire [7:0] train_audio_in;

input wire en_in;

input wire [7:0] audio_in;

output reg en_out;

output reg [7:0] audio_out;

output reg cat_out;

output reg [7:0] train_audio_out;

output reg train_I;

output reg train_2;

output reg train_3;

output reg train_4;

output reg train_5;

output reg train_6;

output reg train_7;

output reg train_8;

/*shift registers that hold things back two clock cycles*/

reg en_old;

reg en_old_old;

reg train_old;

reg train_old_old;

reg [7:0] audio_hold_l;

reg [7:0] train_hold_1;

reg cat_in_hold;

reg word_in_hold;

always @ (posedge clock) begin

if (reset) begin

audio_hold_I <= 0;

audio_hold_2 <= 0;</pre>

train_hold_I <= 0;

train_hold_2 <= 0;

en_old <= 0;

en\_old\_old <= 0;

train_old <= 0;

train_old_old <= 0;

en_out <= 0;

audio_out <= 0;

cat_out <= 0;

train_audio_out <= 0;

train_I <= 0;

train_2 <= 0;

train_3 <= 0;

train_4 <= 0;

train_5 <= 0;

train_6 <= 0;

train_7 <= 0;

train_8 <= 0;

end

else begin

en_old <= en_in;

en_old_old <= en_old;

```

```

train_old <= train_in;

train_old_old <= train_old;

if (train_in | | train_old_old) begin

en\_out <= 0;

cat_in_hold <= (train_in) ? cat_in : cat_in_hold;</pre>

train_hold_I <= (train_in) ? train_audio_in : 0;</pre>

train_audio_out <= train_hold_I;</pre>

cat_out <= cat_in;

train_I <= (word_in == 0) ? I : 0;

train_2 <= (word_in == 1) ? 1 : 0;

train_3 <= (word_in == 2) ? I : 0;

train_4 <= (word_in == 3) ? I : 0;

train_5 <= (word_in == 4) ? 1 : 0;

train_6 <= (word_in == 5) ? I : 0;

train_7 <= (word_in == 6) ? I : 0;

train_8 <= (word_in == 7) ? I : 0;

else if (en_in | | en_old_old) begin

train_I \leq = 0;

train_2 <= 0;

train_3 <= 0;

train_4 \le 0;

train_5 <= 0;

train_6 <= 0;

train_7 <= 0;

train_8 <= 0;

audio_out <= audio_in;</pre>

cat_out <= cat_in;

en_out <= I;

end

else begin

audio_hold_I <= 0;</pre>

audio_hold_2 <= 0;</pre>

train_hold_I <= 0;

train_hold_2 <= 0;

en_old <= 0;

en_old_old <= 0;

train_old <= 0;

train_old_old <= 0;

en\_out <= 0;

audio_out <= 0;

train_audio_out <= 0;

train_I <= 0;

train_2 <= 0;

train_3 <= 0;

train_4 <= 0;

train_5 <= 0;

train_6 <= 0;

train_7 <= 0;

train_8 <= 0;

end

end

```

end

endmodule

29

#### **Appendix D: FIR 31 Verilog**

```

//////

//

// 31-tap FIR filter, 8-bit signed data, 10-bit signed coefficients.

// ready is asserted whenever there is a new sample on the X input,

// the Y output should also be sampled at the same time. Assumes at

// least 32 clocks between ready assertions. Note that since the

// coefficients have been scaled by 2**10, so has the output (it's

// expanded from 8 bits to 18 bits). To get an 8-bit result from the

// filter just divide by 2^{**}10, ie, use Y[17:10].

//////

module fir31(

input wire clock, reset, ready,

input wire signed [7:0] x,

output reg signed [17:0] y

);

reg signed [7:0] sample[31:0];

// buffer of 32 8-bit signed samples

reg [4:0] offset;

// offset pointer for sample memory

reg [4:0] index;

wire signed [9:0] coeff;

coeffs31 coeffs31(.index(index),.coeff(coeff));

always @(posedge clock) begin

if (reset) begin

offset \leq 0;

index \le 0:

y <= 0;

end

else if (ready) begin

offset <= offset + 1;

sample[offset] <= x;</pre>

y <= 0;

index \le 0:

end

else if (index < 31) begin

y \le y + coeff * sample[(offset - index - 1) & 31];

index \le index + 1;

end

end

endmodule

```

```

//////

//

// Coefficients for a 31-tap low-pass FIR filter with Wn determined for a 4kHz

sampling rate. Since we're doing integer arithmetic, we've scaled

// the coefficients by 2**10

// Matlab command: round(fir1(30,.2/24)*1024)

//

//////

module coeffs31(

input wire [4:0] index,

output reg signed [9:0] coeff

// tools will turn this into a 31x10 ROM

always @(index)

case (index)

'd0: coeff = -1;

'd1: coeff = -1;

d2: coeff = -1;

'd3: coeff = 0;

'd4: coeff = 2:

d5: coeff = 5:

'd6: coeff = 11:

'd7: coeff = 19;

'd8: coeff = 28:

'd9: coeff = 40:

d10: coeff = 52;

'd11: coeff = 64:

d12: coeff = 75;

d13: coeff = 84:

d14: coeff = 90;

d15: coeff = 91;

'd16: coeff = 90;

d17: coeff = 84:

d18: coeff = 75:

d19: coeff = 64;

d20: coeff = 52:

d21: coeff = 40;

d22: coeff = 28;

'd23: coeff = 19;

d24: coeff = 11:

'd25: coeff = 5;

d26: coeff = 2;

```

```

'd27: coeff = 0;

'd28: coeff = -1;

'd29: coeff = -1;

'd30: coeff = -1;

default: coeff = 10'hXXX;

endcase

endmodule

```

## **Appendix E: DTW Engine Verilog**

module dtw\_engine2(input wire clock,

```

input wire reset,

input wire signed [7:0] train_in,//training audio

input wire train,

input wire en,

input wire signed [7:0] audio_in,

input wire category, //I bit toggle for category

output reg [25:0] distance,

output reg DTW_done);

```

```

reg [11:0]a_temp;

reg we_temp;

reg signed [7:0] mem_in_temp;

wire signed [7:0] mem_out_temp;

//Template Memory

mybram #(.LOGSIZE(12),.WIDTH(8))

template(.addr(a\_temp),.clk(clock),.we(we\_temp),.din(mem\_in\_temp),.dout(mem\_out\_temp));

reg [10:0] a_match;

reg we_match;

reg signed [7:0] mem_in_match;

wire signed [7:0] mem_out_match;

//Match Memory

mybram #(.LOGSIZE(11),.WIDTH(8))

match(.addr(a_match),.clk(clock),.we(we_match),.din(mem_in_match),.dout(mem_out_match));

reg [11:0] a_dtw;

reg [11:0] a_dtw_store;

//stores the address of a_dtw so that we can go back to it while doing the address manipulation

reg we_dtw;

reg [19:0] mem_in_dtw;

wire [19:0] mem_out_dtw;

//DTW Memory

mybram #(.LOGSIZE(12),.WIDTH(20))

DTW(.addr(a_dtw),.clk(clock),.we(we_dtw),.din(mem_in_dtw),.dout(mem_out_dtw));

/*miscellaneous */

reg [2:0] state;

reg [2:0] nextstate;

reg [2:0] substate;

reg train_old;

reg train_old_old;

reg en_old;

reg en_old_old;

reg we_dtw_old;

reg a_dtw_toggle;

reg clear_dtw_mem_f;

reg [12:0] clear_count;

/*pointers */

reg [11:0] end_val;

reg [11:0] start_val;

reg [21:0] count;

reg [10:0] rollcount;

/*local storage */

reg [25:0] ij;

//the four blocks needed for each calculation

reg [25:0] ilj;

reg [25:0] min_ijl_iljl;

```

```

reg [25:0] iljl;

reg [25:0] ijl;

reg [17:0] Dij;

//difference between the two samples

/*state*/

localparam training = 1;

localparam transfer = 2;

localparam calculate = 3;

localparam hold = 4;

/*substate*/

local param write = 0;