# MIT 6.111: Introductory Digital Systems Laboratory, Fall 2005 Final project report

# A Volumetric 3D LED display

David Wyatt wyatt@mit.edu

Lawrence Wujanto <a href="mailto:lwujanto@mit.edu">lwujanto@mit.edu</a>

# **Abstract**

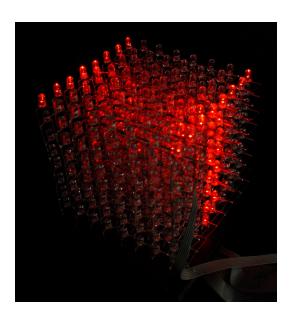

A 3D volumetric LED display was designed and built, along with a number of accompanying applications. The display consisted of a cube of 512 individually controllable ultra-bright LEDs hand-soldered into a lattice, and was intended to demonstrate some of the capabilities that a true 3D display have over 2D representations of 3D objects. In addition, a renderer was built which concurrently displays an orthographic representation of the cube on an SVGA display.

Applications built include 3D Pong, 2D and 3D versions of Cellular Automata, a music visualizer, and a "trip-let" displaying the letters MIT. Different applications can be activated by means of a switch. They incorporate various peripherals, including as mouse control and audio input with CIC filtering.

The project was implemented in the hardware description language Verilog, compiled and downloaded to a Xilinx FPGA chip. Conclusions arising from this aspect of the design process, and from the rest of the project, are presented at the end of the report.

# **Table of Contents**

| Abstract                                                                                      |    |

|-----------------------------------------------------------------------------------------------|----|

| List of Figures                                                                               | ii |

| 1 Overview                                                                                    | 1  |

| 1.1 Background                                                                                | 1  |

| 1.2 Chosen system configuration                                                               | 1  |

| 2 Technical description                                                                       |    |

| 2.1 Data generation subsystem                                                                 | A  |

| 2.1.i Application Reset                                                                       |    |

| 2.1.ii 3D Pong                                                                                | 4  |

| 2.1.iii 2D Cellular Automata                                                                  | 4  |

| 2.1.iv 3D Cellular Automata                                                                   | 5  |

| 2.1.v "MIT" trip-let                                                                          | 7  |

| 2.1.vi Music visualiser                                                                       | 7  |

| 2.2 Display subsystem                                                                         | 9  |

| 2.2.i Voxel addressing                                                                        | 9  |

| 2.2.ii Data output module                                                                     | 9  |

| 2.2.iii Renderer                                                                              | g  |

| 2.2.iv Screen buffer wrapper                                                                  | 10 |

| 2.2.v Wireframe generator                                                                     | 11 |

| 2.2.vi SVGA interface module                                                                  | 11 |

| 2.3 Physical display hardware                                                                 | 11 |

| 2.3.i Mechanical design and construction                                                      | 11 |

| 2.3.ii Driver electronics and power issues                                                    | 13 |

| 3 Implementation, testing and debugging                                                       | 15 |

| 3.1 Design flow                                                                               | 15 |

| 3.2 Debugging                                                                                 | 15 |

| 3.3 Division of Labour                                                                        | 16 |

| 4 Conclusions                                                                                 | 17 |

| 4.1 Results from the project                                                                  |    |

| 4.2 Possibilities for future expansion                                                        |    |

| 5 Components used                                                                             |    |

| 6 References                                                                                  |    |

| Appendix A: Labkit.v                                                                          |    |

| Appendix B: Data generation subsystem code                                                    | 28 |

| 1.application_reset.v                                                                         |    |

| 2.cell_aut_2d.v                                                                               |    |

| 3.cell_aut_3d.v                                                                               |    |

| 4.clock_divider.v                                                                             |    |

| 5.mit.v                                                                                       |    |

| 6.music_visualizer.v                                                                          | 35 |

| 7.mux_8input.v                                                                                |    |

| 8.pong.v                                                                                      |    |

| Appendix C: Display subsystem code                                                            |    |

| 1. data_output_module.v                                                                       |    |

| 2. renderer.v                                                                                 |    |

|                                                                                               |    |

| List of Figures                                                                               |    |

| Figure 1 - Overall block diagram                                                              | 2  |

| Figure 2 - The FPGA development board on which the project was implemented                    |    |

| Figure 3 - Layout of various application modules                                              |    |

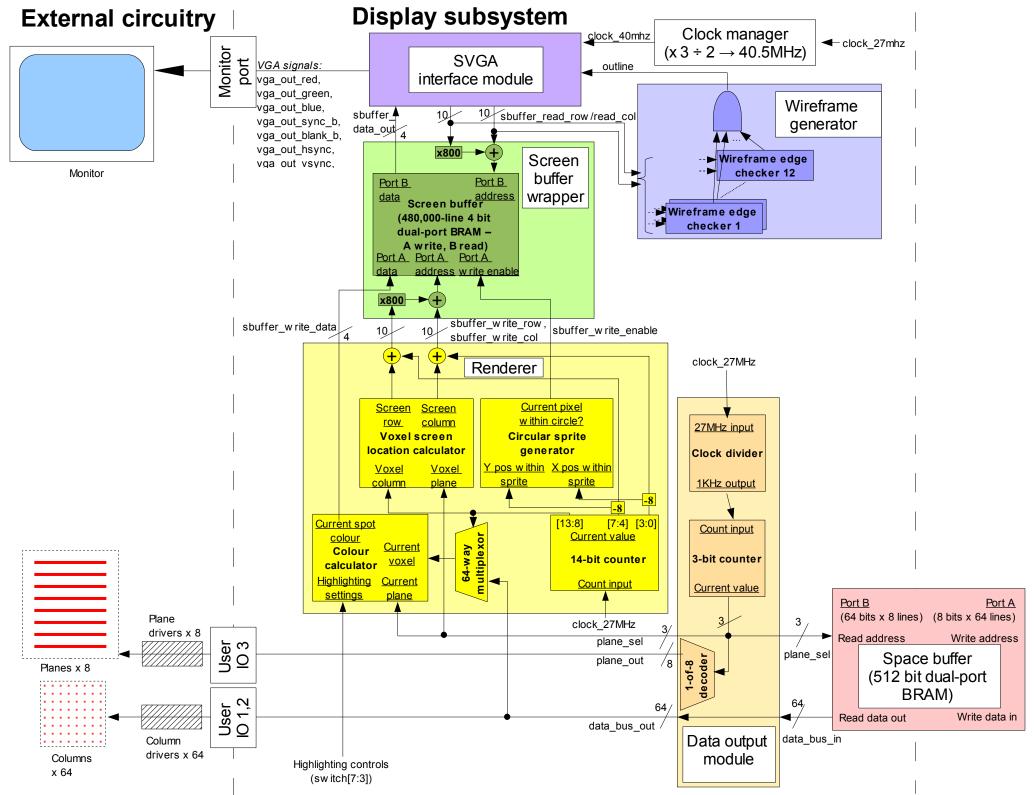

| Figure 4 - Block diagram for the display subsystem                                            |    |

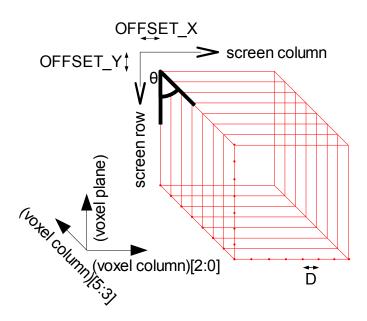

| Figure 5 - Diagram to show mapping from 3D (x,y,z) co-ordinates to 2D screen rows and columns |    |

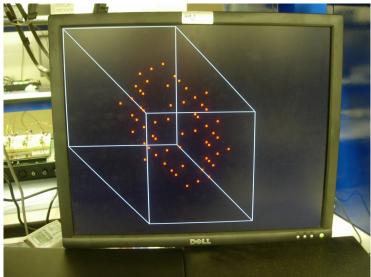

| Figure 6 - SVGA display output, with 3D cellular automata as the active application           |    |

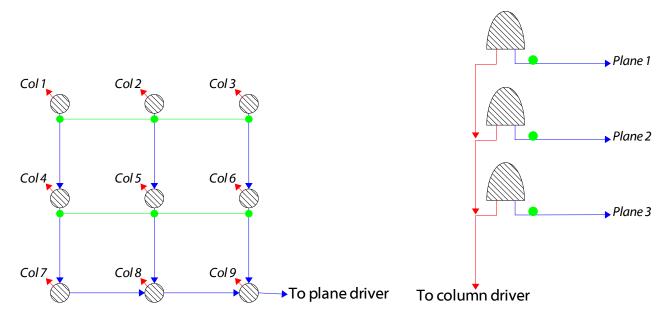

| Figure 7 - Top view of wiring within a horizontal plane.                                      |    |

| Figure 8 - Side view of wiring within a vertical column                                       |    |

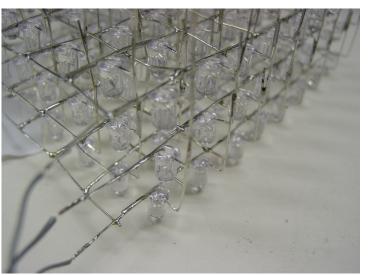

| Figure 9 - A plane of LEDs laid out on the jig                                                |    |

| Figure 10 - The first three planes of LEDs assembled                                          |    |

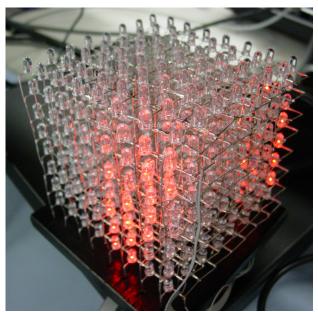

| Figure 11 - The completed LED cube                                                            |    |

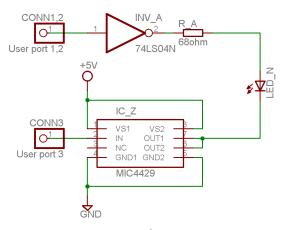

| Figure 12 - Driver circuitry for a representative LED                                         |    |

| rigure 12 - Driver Circuity for a representative LED                                          | 4  |

### 1 Overview

## 1.1 Background

Many aspects of contemporary work and recreation require the effective visualisation of three-dimensional data:

- studying the structures and interactions of biochemicals

- designing a new space vehicle

- extracting a relationship from multi-variable plots in the social sciences

- diagnosing a patient's illness from non-invasive scans

- planning a new sculpture

- · ...or playing the latest computer game!

Conventional methods for displaying 3D data exclusively involve flat (2D) displays that give the illusion of depth. These range from (albeit sophisticated) rendering techniques that still ultimately generate a flat image, to displays that direct a different 2D image to each eye (through head-mounted displays, coloured filter glasses or optical methods involving lenticular surfaces or parallax barriers). However, these all suffer a number of disadvantages, related to the fact that the 3D images do not occupy the same space as the observer:

- Images typically have a limited angle of view and/or are only visible with special goggles

- The observer cannot interact with the images in intuitive ways (e.g. pointing out a part of the image to a colleague with one's hand)

- The display can give erroneous impressions of relative size/scale

These shortcomings can be overcome by a true volumetric display – one where the image of a volume of space actually occupies a volume (composed of "voxels", volumetric pixels). A number of methods for constructing such displays have been attempted in the past, including the following:

- <u>Swept volume methods</u> ([1],[2]) projecting light onto a moving surface such that the reflected projection appears to originate from the appropriate location within the volume

- <u>Dot-matrix LED cubes</u> ([3], [4], [5], [6]) individual LEDs in a lattice form the voxels for displaying images

- <u>Solid-state fluorescence</u> ([2])– invisible laser beams excite specific regions within a crystal to emit visible light

# 1.2 Chosen system configuration

For this project a dot-matrix volumetric display was built using a lattice of 512 LEDs, arranged in an 8x8x8 cube. The number of voxels was chosen as a compromise between resolution and complexity – since the number of voxels required increases as the cube of the side length, another row of voxels would have increased the number of LEDs by over 40% for a marginal increase in display resolution.

In order to take advantage of the capabilities of the display, the project involved the production of several applications whose outputs would have been difficult, if not impossible, to display with a conventional 2D monitor.

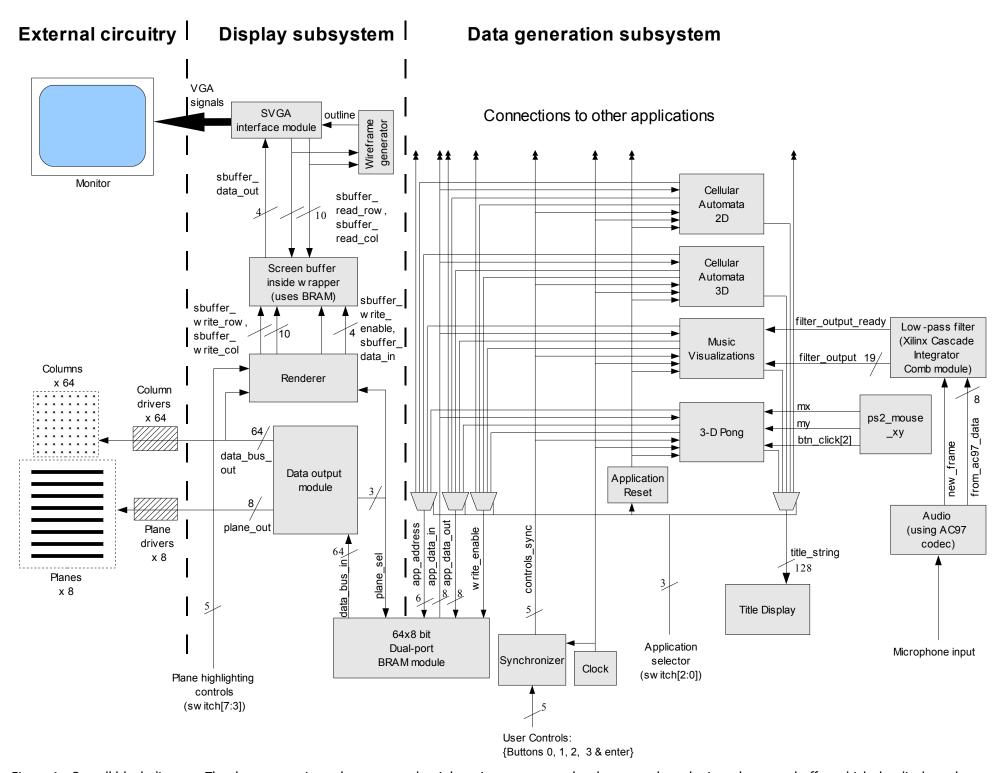

A block diagram showing the overall decomposition of the project into subsystems and modules, is shown in Figure 1; more detailed block diagrams of each subsystem can be found in section 2.

Figure 1 - Overall block diagram. The data generation subsystem on the right writes patterns to be shown on the cube into the space buffer, which the display subsystem then reads and displays on the cube and an SVGA screen.

An additional aspect of the project was the inclusion of an SVGA output to display an orthographic-projection image of the cube on a conventional PC monitor. This was primarily undertaken in case unforeseen problems made it impossible to implement the 3D display successfully, but this auxiliary output can also be used if other circumstances (such as debugging) require the data generation subsystem to be tested without the physical display hardware.

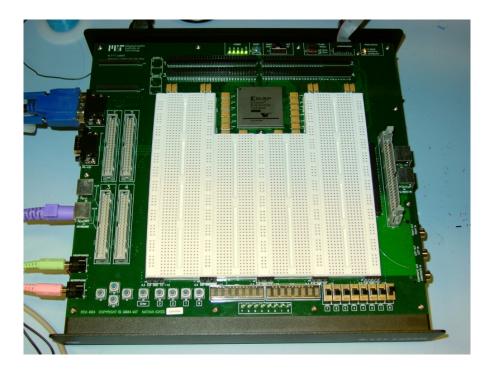

The system was implemented using the Xilinx VirtexII field-programmable gate array (FPGA) development board developed for the 6.111 laboratory class at MIT, shown in Figure 2. The board contains a small number of switches and LEDs that were used as signals for some of the modules, as well as connections to other input and output devices (in particular, the PS/2 mouse input and monitor output).

Figure 2 - The FPGA development board on which the project was implemented. The switches, buttons and LEDs are located at the front of the board, while the large FPGA chip is visible to the rear of the breadboard area.

The remainder of this report describes the design and implementation of the project; the computer-aided testing and debugging phase; and the conclusions drawn from the experience.

# 2 Technical description

Verilog code for all the modules implemented in this project is attached in the appendices to this report.

### 2.1 Data generation subsystem

A number of applications have been written for the volumetric display. Switches 0 to 2 are used to select between the different applications, allowing for up to 8 applications. These switches set the multiplexors in the data generation subsystem to select the appropriate app\_address, app\_data\_out, write\_enable and title\_string lines for the currently active application.

The 512 bit "space buffer" serves as an interface between the data generation display subsystems. Applications have read and write access via port B of this dual port BRAM, and update this buffer constantly with the present state of the active application.

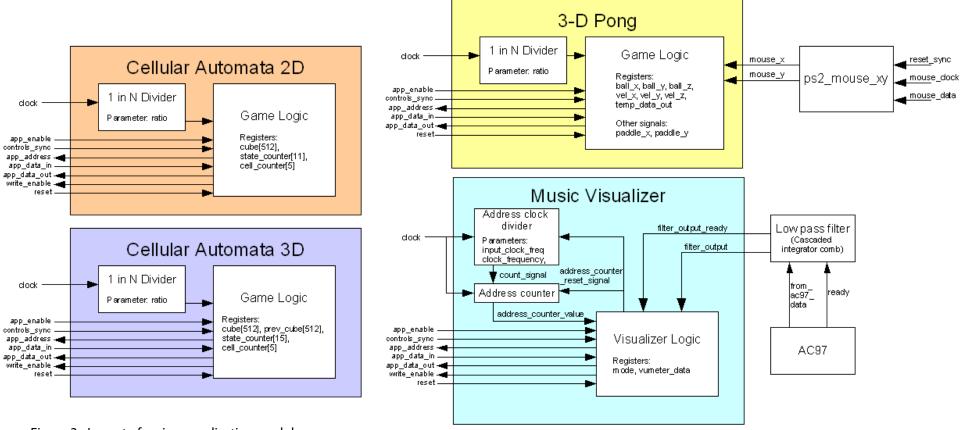

Figure 1 shows the interconnection between applications in the subsystem, while figure 3 shows more details on the implementation of each application.

### 2.1.i Application Reset

In order to make applications reset themselves whenever they are selected, an Application Reset module drives the reset line of all applications, sending a signal high pulse for one clock cycle whenever the application selector switches are toggled. This is used in applications such as 2D cellular automata to reset the playing field and await user input.

### 2.1.ii <u>3D Pong</u>

A natural extension of the popular two-dimensional game, 3D pong is a one-player game which involves defending the bottom surface of the cube from being struck by a bouncing "ball" by manipulating a paddle which deflects the ball. The paddle is controlled using a PS/2 interface mouse.

The PS/2 mouse driver module was used with X & Y motion limited from 0 (7'b000\_0000) to 95 (7'b101\_1111). The 4 least significant bits of the mouse coordinates were ignored so as to decrease the sensitivity of the mouse, while the next 3 bits were used for the location of the paddle.

Since a bouncing ball that travels with equal magnitudes of velocity along each axis (as was the case for the 2D pong implemented for Lab 4 in 6.111) would be rather boring in that it would follow the same path round the cube every time, we specified that the velocity of the ball should be altered during every bounce off the paddle, as a function of where it strikes the paddle.

To allow "intermediate" angles of motion that are not along one of the principle axes/diagonals, the location of the ball is stored using a 6 bit register for each of the three axes, and then truncated to 3 bits wide for determining the ball's location in the cube.

A set of registers store data governing the velocity and location of the ball. This data is updated regularly to shift the ball; ensure that it bounces off walls; and change its velocity upon contact with the paddle. At the same time, the registers are read off and used to update the contents of the space buffer to display the paddle and ball on the playing field. An 'inv' register was included in the game that is high for a short period after a collision, causing the state of the LEDs to invert. This indicates when a player has failed to catch the ball.

### 2.1.iii 2D Cellular Automata

Cellular automata, a popular form of which is Game of Life, involves a grid of cells which may each be either "living" or "dead", and a set of rules which dictates the next state of each cell, as a function of the states of its neighbouring

cells. This application has a number of predefined initial states that are loaded onto the top plane of the cube when one of buttons 0 to 3 are pressed. At a frequency of 1Hz, the contents of the top plane are evolved using the standard Game of Life rules set<sup>1</sup>, while previous states of the plane are propagated downwards in the cube so as to show the time evolution of the game.

The state of the entire cube was stored using a 512 bit register. The propagation of previous states could be done quite easily by a single cube [511:64] <= cube [447:0] command. Evolving the state of the plane was a little more complicated, as this involved summing the number of neighbouring live cells for each cell, and then deciding on the next state of each cell as a function of the value of this sum. This was done by incrementing through all possible values of an 11-bit register (state\_counter) to cycle through every operation that had to be done. This could be thought of as a 2 x 64 x 16 state FSM, allowing for 16 operations on each of the 64 LEDs on a plane, and doubling this to allow more operations which update the cube contents to the space buffer.

The first 64 x 16 states are used for computing the next state of the top plane, with bits [9:4] used to represent the active cell, and bits [3:0] to specify 16 operations for each cell, including resetting the cell counter, adding the contents of each of the 8 neighbouring cells, and applying the rule set to determine the next state of the active cell.

The next 64 x 16 states allow for updating the state buffer with the new state of the cube, with many leftover unused states. Note that when a new pattern is requested, the state jumps straight to this half of the state sequence so as to display the new state before evolving the cube state.

### 2.1.iv 3D Cellular Automata

The same idea from 2D Cellular Automata can be extrapolated into the third dimension by summing all 26 neighbouring cells for each of the 512 LEDs in the LED cube. The rule set we used was that 2 neighbouring live cells let life persist, while 3 or 4 neighbouring live cells cause life to be born, otherwise the cell "dies". A 15-bit state counter was required to allow for 2 x 512 x 32 states.

It has been suggested that a ROM could be used to store all possible combinations of the neighbouring cells and the cell itself, and return the next state of the cell. This would certainly be a good idea for 2D cellular automata in reducing the number of operations required. However, this may be infeasible for 3D cellular automata due to the large number of possible states that 27 cells may have, and hence the large ROM size.

<sup>1 2</sup> neighbouring live cells – life persists; 3 neighbouring cells – life is born; otherwise cell "dies"

# Application block diagrams

Figure 3 - Layout of various application modules.

### 2.1.v <u>"MIT" trip-let</u>

As a demonstration of the 3D display capability of the volumetric display, we created an application which displays the letters M, I & T from each of the principal axes, inspired by the cover of Douglas Hofstadter's *Gödel, Escher, Bach*. This was done by storing 64-bit parameters which describe 8 x 8 "font grids" for these letters, and using Boolean AND operators on elements of these grids, referenced using different pairs of the cube's three coordinates.

```

app_address <= next_address;

app_data_out[0] <= M[next_address] && I[{next_address[2:0], 3'b000}] && T[{next_address[5:3], 3'b000}];

app_data_out[1] <= M[next_address] && I[{next_address[2:0], 3'b001}] && T[{next_address[5:3], 3'b001}];

...(continued for all 8 bits of app_data_out)</pre>

```

next\_address[5:3] and next\_address[2:0] effectively represent the z and y axes of the cube respectively. The 8 bits of app\_data\_out contain the contents of a row of LEDs along the x axis. This idea could be extended to allow any combination of letters to be displayed, perhaps using the PS/2 keyboard to input letters.

In this module, we also experimented with varying the intensity of the LEDs by cycling the contents of each activated LED through the contents of different 8 bit strings. For example, this included an "all on" string, an alternating on/off string, and an "all off" string. The different number of "on" states in the string changed the brightness of the LED. A different string was selected as a function of time (using the top few bits of a large counter), and the z coordinate in the cube. The result of this was a wave-like pattern that propagated down the z axis of the cube.

#### 2.1.vi <u>Music visualiser</u>

This module uses audio input to create 3D patterns within the cube.

The audio input is first converted to digital form by a National Semiconductor LM4550 audio codec (compatible with the AC97 standard), controlled by a wrapper module supplied by [9]. It is then low-pass filtered by a Cascaded Integrator Comb filter produced by the Xilinx Coregen application, configured to downsample by a ratio of 1920 to 1 (thus giving a 25Hz output since new samples are supplied by the AC97 at 48KHz) with 1 stage and a differential delay of 2. These parameters were arrived at through experimentation and simulation of the filter's frequency response using Microsoft Excel, to determine a suitable cut-off frequency.

When ready, the top 3 bits of the filter's 19-bit output (plus 4, to convert signed 2's complement into unsigned format) are fed into the first of a queue of 8 vumeter\_data registers, the contents of the rest of which propagate down a register. The contents of these registers then generate the output to be shown on the cube according to the currently-selected mode:

- In mode 0, "Linear", the cube displays an oscilloscope that has been extruded in the third dimension; the contents of each register determines the height of the "oscilloscope trace" in the corresponding vertical plane.

- In mode 1, "Ripples", the contents of the registers determine the left-right positions of concentric squares of a vertical plane in the cube, with the newest register controlling the central square; the aim was to give the impression of ripples spreading out from the centre of the plane, though the pattern could also be regarded as an oscilloscope trace rotated about a vertical axis through its left-hand end.

Switching between modes is controlled by pressing the numbered pushbuttons on the labkit board. Writing data to the space buffer is accomplished using a 6-bit counter incremented at 65KHz and reset every time a new sample is received from the filter (to keep the space buffer writing in rough synchrony with the changes in the underlying data). The write address sent to the space buffer is the value of the counter, and the data is determined according to the mode and the values of the vu\_meter\_data registers.

Figure 4 - Block diagram for the display subsystem. The space buffer stores the current state of the cube, and the other modules control its display on both output devices.

### 2.2 Display subsystem

This subsystem:

- Transfers arbitrary data representing spatial patterns from the "space buffer" RAM to an 8x8x8 matrix of LEDs

- Has a refresh rate of 125Hz to exploit persistence of vision

- Produces an auxiliary SVGA output which displays an orthographic image of display state at 800 x 600 resolution, with controls to highlight specific planes of the cube

See Figure 4 for a block diagram of this subsystem.

#### 2.2.i <u>Voxel addressing</u>

Since there are only 192 output pins available on the labkit and 512 LEDs in the display, it is not possible to address each LED individually; thus a passive matrix multiplexing system is used. Each horizontal plane of 64 LEDs has a unique "enable" pin, corresponding to a row in a traditional (2D) passive matrix display, while the 8 LEDs in each vertical column correspond to the columns of a conventional display. Thus the LEDs that are lit are at the intersection of enabled planes and columns. This requires 64 output pins for the columns plus 8 for the planes.

With this pattern of interconnection, either 8 or 64 LEDs could be driven at once; the complete cube could be lit by cycling through each column or each plane in turn. In order to achieve the maximum the duty cycle for the LEDs and thus enhance their visibility, it was chosen to enable a single plane at a time while driving the columns with the correct data for that plane.

#### 2.2.ii Data output module

The data output module implements the above method for driving the cube's voxels. It contains a 3-bit counter that is incremented at 1kHz and is used as the address input for the B (read) side of the space buffer, which then outputs 64 bits on the 64-bit-wide data\_bus\_in wire, corresponding to the voxels in the currently selected plane. In the present implementation the data\_bus\_in wire is connected directly to the data\_bus\_out wire, which drives the output pins on user ports 1 and 2 on the labkit, but any processing necessary in future development (such as low-level pulse width modulation for adjusting the output brightness levels) could be incorporated at this stage.

This gives an overall refresh rate for the cube of 125Hz, quite sufficient for persistence of vision [7]. It would be possible to refresh the cube more frequently, but it was thought unnecessary; also, a reduction in brightness of the LEDs was observed if they were driven at significantly higher frequencies.

#### 2.2.iii Renderer

This module performs the orthographic projection from 3D to the 2D SVGA-resolution screen and writes the appropriate data to the screen buffer. It was designed to use the signals from the data output module without requiring any additional control signals so that the latter could be implemented in a straightforward way.

In order to generate the projection, it has four major components (shown as submodules on the block diagram but mostly implemented as code within the main module):

- A 14-bit counter, clocked by the main system clock at 27MHz the value of this counter can be regarded as the state of a finite state machine controlling the module. The top 6 bits of the counter are treated as the number of the voxel whose projection is to be generated, voxel\_column.

- The screen location calculator this takes as input the current voxel column and the current plane number (input to the renderer module from the data output module), and generates the screen co-ordinates of the centre of its projection as follows (where the capitalised terms are constant parameters):

(screen column) = OFFSET\_X + D\*voxel\_column[2:0] + D\_SIN\_THETA\*(7 - voxel\_column[5:3])

(screen row) = OFFSET\_Y +  $D*(7 - voxel\_plane) + D\_COS\_THETA*(7 - voxel\_column[5:3])$ A diagram showing the mapping from voxel\_column and voxel\_plane (specifying the (x,y,z) co-ordinates of a voxel) to the 2D screen co-ordinates can be seen in Figure 5.

- The colour calculator this uses voxel\_column to select the data\_bus\_out signal corresponding to the current voxel, and outputs red if it is on and black if it is off (the shades are configurable via constant parameters). In addition, if highlighting is enabled (that is, if switch[7] is on) it dims the shade of red output when the current plane is not the plane to be highlighted (as set up on switch[6:4]), either in terms of horizontal planes (switch[3] = 0) or vertical planes (switch[3] = 1).

- The circular sprite generator this takes the co-ordinates of the current point within the current voxel's sprite, extracted from the least significant 8 bits of the counter's value, and calculates whether they represent a point within a parameterised radius of the sprite's centre. If so, the write enable to the screen buffer is set high.

The net result of the operation of these four components is that the address inputs to the screen buffer wrapper cycle through the projections of each voxel in turn within the current plane, performing a 16x16 pixel raster scan around the centre of the projection. However, the write enable to the screen buffer is only high when the scan point is within a certain radius of the centre point, generating circles of the appropriate colour in the screen buffer memory.

The constant parameters used by the renderer to determine the scale, location and colours of the projected image can be taken from the instantiating module, allowing for easy reconfiguration of the output.

Figure 5 - Diagram to show mapping from 3D (x,y,z) coordinates to 2D screen rows and columns.

## 2.2.iv Screen buffer wrapper

The renderer and SVGA output modules output pixel co-ordinates on an SVGA screen as 10-bit numbers. These could be simple concatenated to produce the memory location to write; however, such an approach would be inefficient (since only 800x600 pixels out of the 1024x1024 would ever be used) and would mean that the screen buffer would be too large to be implemented using the BRAMs on the FPGA chip. Thus, the 480,000-line 4-bit dual-port BRAM comprising the screen buffer was surrounded by a wrapper module to translate the two 10-bit input co-

ordinates into memory addresses in a by performing a constant multiplication and an addition, on both the write (port A) and read (port B) sides of the memory.

### 2.2.v Wireframe generator

This module takes as input the co-ordinates of the current screen pixel from the SVGA interface module and produces a single-bit signal, outline, that indicates whether the pixel falls on one of the lines making up a wireframe image of the cube. Inside the module this detection is implemented as a series of twelve if statements corresponding to the twelve edges of the cube, parameterised from the labkit module to allow easy compile-time adjustment of the size and location of the image.

At present the projection angle is fixed to be 45° due to the algorithm chosen for drawing the oblique lines at the corners of the cube; use of a more general algorithm, such as the Bresenham line drawing algorithm [8], would remove this restriction.

Figure 6 - SVGA display output, with 3D cellular automata as the active application.

### 2.2.vi SVGA interface module

This module, based heavily on the one provided by [9], generates the required sync and blanking signals for SVGA (800x600) display at a refresh rate of 60Hz. It is clocked at 40.5MHz, the nearest frequency to the ideal 40MHz that could be synthesised by a Digital Clock Manager (a delay-locked-loop, here set up to output the input frequency x 3  $\div$  2). As well as outputting the VGA control signals, it produces the signals hount and vocunt – 10-bit signals specifying the point on the screen whose data is being output at that time. These signals are sent to the read side of the screen buffer wrapper and to the wireframe generator, which return (respectively) signals representing the presence of a voxel sprite and/or a a wireframe outline pixel at that location; logic in the main labkit module ensures that voxel sprites receive priority if both are present at the same location.

# 2.3 Physical display hardware

### 2.3.i Mechanical design and construction

As described in Section 2.2.i, the LEDs were connected in a passive matrix in which:

- All LED cathodes within a horizontal plane are wired together

- All anodes within a vertical column are wired together

With this polarity, the selected cathode plane is driven low while all others are driven high, and simultaneously the data to be displayed on that plane is presented on the columns in uninverted logic (i.e. if the column is high the corresponding LED will be on).

For simplicity when using 5mm LEDs, and to reduce obscuring of the display by a support frame, the structure that holds the LEDs in the lattice was built by soldering together the LEDs' own wires and some extra strands of solid-core wire whose insulation had been removed. The resulting lattice has a 15mm pitch, due to the lengths of the LED leads. Diagrams of the arrangement are shown in Figure 7 and Figure 8.

Figure 7 - Top view of wiring within a horizontal plane.

Figure 8 - Side view of wiring within a vertical column.

The LED cathodes (blue) are joined together in rows within each plane, with each row joined to the next at one end; supplementary wires (green) provide redundant cathode connections and mechanical stability. The LED anodes (red) are connected together in columns.

This design permitted easy, if repetitive, assembly as follows:

- 1. Each LED's leads were bent according to the diagrams in Figure 7 and Figure 8.

- 2. The LEDs were soldered together in planes of 64 (wiring up the cathodes), using a simple jig to hold them in place while soldering (Figure 9).

- 3. The planes were then stacked into a cube (soldering together the anodes), starting from the topmost layer and working downwards (Figure 10).

- 4. Finally, a wooden baseboard was attached to the cube for addition mechanical strength, and the plane and column connection wires were attached.

The completed cube, shown in Figure 11, contains 1472 hand-soldered joints, and took approximately 10 hours to construct. During the initial periods of LED lead-shaping before cube construction began, despite the fact that no count was kept, exactly 508 LEDs were processed of which only 1 was incorrectly bent.

Figure 9 - A plane of LEDs laid out on the jig. The LEDs' cathodes have been soldered together, and the first stabilising cross-wire has been soldered in place.

Figure 10 - The first three planes of LEDs assembled. The corner closest to the camera is the corner at which the cathode wires for each plane were connected, and the way in which the anodes in each plane are soldered to those in the plane below is also evident.

Figure 11 - The completed LED cube. The current pattern was generated by the 2D Cellular Automaton module; the cathode connection corner, voxel column 0, is in the foreground.

### 2.3.ii <u>Driver electronics and power issues</u>

In order to give an acceptable level of brightness at a duty cycle of 1 in 8, high-brightness LEDs with a specified light intensity of 8000mcd and a viewing angle of 20° total were used. They were specified to draw 30mA at 2.7V, and pass less than  $30\mu$ A when reverse biased. The FPGA output pins can only handle up to 24mA, so driver circuitry was needed whose maximum ratings were calculated as follows.

- · Per plane:

- when active, at maximum 64 LEDs will be on plane driver must sink 1.92A

- when inactive, at maximum 64 LEDs will be reverse biased plane driver must source 1.92mA

- Per column:

- when high, 1 LED will be on and 7 off column driver must source 30mA

- when low, 1 LED will be off and 7 reverse biased column driver must sink 0.21mA

Eight MIC4429 6A inverting MOSFET drivers were thus used for each plane, driven directly by FPGA output pins. The column driver circuitry used 7404 TTL inverters along with  $68\Omega$  current-limiting resistors. The schematic for the driver circuitry is shown in Figure 12.

Figure 12 - Driver circuitry for a representative LED. LED N is at the intersection of column A (between 0 and 63) and plane Z (between 0 and 7).

Since only one plane is be active at once, the current supply requirement for the entire system were expected to be 2A at 5V (in addition to the power requirement of the FPGA and peripherals). This was more than could be supplied by the FPGA board, but well within the capability of a standard laboratory bench power supply. In fact current consumption was limited to around 0.3A due to unanticipated voltage drops within the driver circuitry, but this did not appear to hinder brightness.

# 3 Implementation, testing and debugging

## 3.1 Design flow

The submodules specified in Section 2 were implemented in Verilog, an industry-standard hardware description language, using the Xilinx Integrated Software Environment (ISE) v6 toolchain. The initial steps involved writing the modules by hand using ISE's built-in text editor and project-based file organisation system; a bitstream configuration file for a VirtexII XC2V6000 field-programmable gate array (FPGA) chip was then generated from within ISE. This involved the following sequence of steps (automated by the software):

- 1. Compiling Verilog to a netlist of primitive gates and circuit elements (using the synthesis tool XST).

- 2. Mapping the netlist onto the resources available in the FPGA.

- 3. Placing and routing the components of the circuit for maximum performance.

The bitstream file was downloaded to the FPGA through a JTAG interface. The resulting system behaviour was compared with expectation, leading to modifications of the source files and further compilation cycles.

# 3.2 Debugging

In general, Verilog modules were tested in the hardware rather than by simulating them on a PC. A number of factors contributed to the decision to use this method for fault-finding:

- It was generally simpler to test on the FPGA than in software, once a body of known functional code had been achieved. In the initial stages of the project, priority was given to establishing the shared interface between the subsystems (the space buffer in particular) and creating the display subsystem before embarking on the construction of the physical cube and the programming of the applications. This meant that the two members of the team could work independently, each with access to a functioning (if minimal) system; thus, the patterns produced by an application under construction could be viewed on the SVGA output, and by the same token the partially-complete cube could be tested with a pregenerated test pattern to check its functioning.

- There were usually sufficient inputs and outputs available on the labkit to use those for debugging, rather than having to use a test bench waveform.

- Signals usually changed states sufficiently slowly that it was possible to perform the functions of a logic analyser/oscilloscope by eye.

- The coding style of the members of the team was such that mistakes were usually fairly straightforward slips that could be found without extensive experimentation indeed, the errors were usually obvious after a little consideration of the behaviour of the output.

By good fortune there were no faults or mistakes during the physical construction of the cube, so debugging as such was not carried out. Careful testing took place, however, to ensure that any potential faults were detected early (as it would be almost impossible to replace a faulty LED in the centre of the cube): each plane's 64 LEDs were tested individually after soldering, and the complete stack was tested after the new plane had been attached. The driver circuitry was similarly checked for function with a current-limited power supply before connecting it to the FPGA for the first time.

## 3.3 Division of Labour

The work was divided between the two partners as follows.

- Lawrence Wujanto:

- 3D Pong

- 2D Cellular Automaton

- 3D Cellular Automaton

- MIT Trip-let

- David Wyatt:

- Display subsystem

- Music visualiser

- Display hardware construction

### 4 Conclusions

### 4.1 Results from the project

A 512-voxel volumetric display was successfully constructed and interfaced to a number of different applications running in an FPGA. The control logic of the applications uses memories, digital signal processing units and human interface devices, and contains multiple finite-state-machines executing different tasks in parallel. All the features specified in the checklist were implemented successfully, as well as completion of or significant progress being made towards some additional features (the MIT Trip-let and an application to rotate arbitrary shapes in 3 dimensions, which unfortunately was not completed by the end of the project).

Undertaking this project contributed greatly to the team's knowledge of and familiarity with contemporary methods of digital logic design, prototyping and debugging. It also gave useful practice in project planning, teamwork and dividing an engineering project into sections for parallel implementation. Communication skills were exercised in preparing reports at multiple stages, from a proposal abstract through to this document, and presenting the design concept for review at an early stage. Lastly, both team members greatly enjoyed the experience and are very grateful for the opportunity to take part.

## 4.2 Possibilities for future expansion

- Low-level (as opposed to application-level) pulse width modulation brightness control of the LEDs, with corresponding intensity variations on the SVGA output

- Implementation of the Bresenham line drawing algorithm to allow projection angles other than 45°.

- Display of 3D data stored on a CompactFlash card may be used as initial conditions for cellular automata

- True 3D rendering (rather than orthographic projection) of the cube on SVGA output, rotatable in real time by user

- Modification of the cube to increase resolution/enhance visibility use a larger lattice spacing or smaller LEDs (ideally SMT, but this would require a new construction technique)

# 5 Components used

- 6.111 class labkit (designed by Nathan Ickes (MIT) and Xilinx)

- Windows PC and Xilinx ISE software for development (monitor can also be used for displaying auxiliary SVGA output)

- 512 ultra-bright LEDs: 5mm, 8000mcd, 20° viewing angle (source: www.ledshoppe.com)

- Wire: solid-core, multi-core ribbon cable

- Baseboard: plywood, 10mm thick, 135mm x 135mm

- Bench power supply: capable of supplying 1A at 5V

- 2 breadboards

- LED driver circuitry: 12x 7404 hex inverter chips, 64x  $68\Omega$  resistors, 8x MIC4429 inverting 6A MOSFET driver chips (source: www.digikey.com)

### 6 References

- [1] Actuality Systems, "Perspecta 3d display", <a href="http://www.actuality-systems.com/">http://www.actuality-systems.com/</a> (accessed 3 November 2005)

- [2] Felix 3D, "Felix 2"/"solidFELIX", http://www.felix3d.com/ (accessed 3 November 2005)

- [3] James Clar, "3d display cube white", <a href="http://www.jamesclar.com/product/2005/3dcubewhite/">http://www.jamesclar.com/product/2005/3dcubewhite/</a> (accessed 3 November 2005)

- [4] Network Wizards, "Cubatron", <a href="http://nw.com/nw/projects/cubatron/">http://nw.com/nw/projects/cubatron/</a> (accessed 3 November 2005)

- [5] Todd Holoubeck, "LED cube", <a href="http://www.toddholoubek.com/projects/ledpage/">http://www.toddholoubek.com/projects/ledpage/</a> (accessed 3 November 2005)

- [6] Chris Lomont, "LED Cube", <a href="http://www.lomont.org/Projects/LEDCube/LEDCube.php">http://www.lomont.org/Projects/LEDCube/LEDCube.php</a> (accessed 3 November 2005)

- [7] Wikipedia, "Persistence of Vision", <a href="http://en.wikipedia.org/wiki/Persistence">http://en.wikipedia.org/wiki/Persistence</a> of Vision (accessed 3 November 2005)

- [8] Colin Flanagan, "The Bresenham Line-Drawing Algorithm", <a href="http://www.cs.helsinki.fi/group/goa/mallinnus/lines/bresenh.html">http://www.cs.helsinki.fi/group/goa/mallinnus/lines/bresenh.html</a> (accessed 12 December 2005)

- [9] 6.111 course staff, MIT, sample Verilog files, http://web.mit.edu/6.111/www/f2005/handouts.html#samplecode (accessed 15 November 2005)

# Appendix A: Labkit.v

```

// 6.111 FPGA Labkit -- Template Toplevel Module

//

// For Labkit Revision 004

//

// Created: October 31, 2004, from revision 003 file

// Author: Nathan Ickes

// CHANGES FOR BOARD REVISION 004

// 1) Added signals for logic analyzer pods 2-4.

// 2) Expanded "tv_in_ycrcb" to 20 bits.

// 3) Renamed "tv out data" to "tv out i2c data" and "tv out sclk" to

"tv out i2c clock".

// 4) Reversed disp_data_in and disp_data_out signals, so that "out" is an

output of the FPGA, and "in" is an input.

//

// CHANGES FOR BOARD REVISION 003

// 1) Combined flash chip enables into a single signal, flash_ce_b.

// CHANGES FOR BOARD REVISION 002

//

// 1) Added SRAM clock feedback path input and output

// 2) Renamed "mousedata" to "mouse data"

// 3) Renamed some ZBT memory signals. Parity bits are now incorporated into

the data bus, and the byte write enables have been combined into the

//

//

4-bit ram# bwe b bus.

// 4) Removed the "systemace_clock" net, since the SystemACE clock is now

hardwired on the PCB to the oscillator.

//

// Complete change history (including bug fixes)

//

// 2005-Sep-09: Added missing default assignments to "ac97 sdata out",

//

"disp data out", "analyzer[2-3] clock" and

//

"analyzer[2-3] data".

// 2005-Jan-23: Reduced flash address bus to 24 bits, to match 128Mb devices

actually populated on the boards. (The boards support up to

//

//

256Mb devices, with 25 address lines.)

//

// 2004-Oct-31: Adapted to new revision 004 board.

//

// 2004-May-01: Changed "disp data in" to be an output, and gave it a default

value. (Previous versions of this file declared this port to

//

//

be an input.)

//

// 2004-Apr-29: Reduced SRAM address busses to 19 bits, to match 18Mb devices

//

actually populated on the boards. (The boards support up to

//

72Mb devices, with 21 address lines.)

// 2004-Apr-29: Change history started

```

```

module labkit (beep, audio_reset_b, ac97_sdata_out, ac97_sdata_in, ac97_synch,

ac97 bit clock,

vga out red, vga out green, vga out blue, vga out sync b,

vga out blank b, vga out pixel clock, vga out hsync,

vga out vsync,

tv_out_ycrcb, tv_out_reset_b, tv_out_clock, tv_out_i2c_clock,

tv_out_i2c_data, tv_out_pal_ntsc, tv_out_hsync_b,

tv out vsync b, tv out blank b, tv out subcar reset,

tv in ycrcb, tv in data valid, tv in line clock1,

tv in line clock2, tv_in_aef, tv_in_hff, tv_in_aff,

tv in i2c clock, tv in i2c data, tv in fifo read,

tv_in_fifo_clock, tv_in_iso, tv_in_reset_b, tv_in_clock,

ram0 data, ram0 address, ram0 adv ld, ram0 clk, ram0 cen b,

ram0 ce b, ram0 oe b, ram0 we b, ram0 bwe b,

ram1 data, ram1 address, ram1 adv ld, ram1 clk, ram1 cen b,

ram1_ce_b, ram1_oe_b, ram1_we_b, ram1_bwe_b,

clock feedback out, clock feedback in,

flash_data, flash_address, flash_ce_b, flash oe b, flash we b,

flash reset b, flash sts, flash byte b,

rs232 txd, rs232 rxd, rs232 rts, rs232 cts,

mouse clock, mouse data, keyboard clock, keyboard data,

clock 27mhz, clock1, clock2,

disp blank, disp data out, disp clock, disp rs, disp ce b,

disp reset b, disp data in,

button0, button1, button2, button3, button_enter, button_right,

button left, button down, button up,

switch,

led,

user1, user2, user3, user4,

daughtercard,

systemace data, systemace address, systemace ce b,

systemace_we_b, systemace_oe_b, systemace_irq, systemace_mpbrdy,

analyzer1_data, analyzer1_clock,

analyzer2_data, analyzer2_clock,

analyzer3_data, analyzer3_clock,

analyzer4 data, analyzer4 clock);

output beep, audio_reset_b, ac97_synch, ac97_sdata_out;

input ac97_bit_clock, ac97_sdata_in;

output [7:0] vga_out_red, vga_out_green, vga_out_blue;

output vga out sync b, vga out blank b, vga out pixel clock,

vga out hsync, vga out vsync;

```

```

output [9:0] tv out ycrcb;

output tv_out_reset_b, tv_out clock, tv out i2c clock, tv out i2c data,

tv_out_pal_ntsc, tv_out_hsync_b, tv_out_vsync_b, tv_out_blank_b,

tv out subcar reset;

input [19:0] tv in ycrcb;

input tv in data valid, tv in line clock1, tv in line clock2, tv in aef,

tv in hff, tv in aff;

output tv_in_i2c_clock, tv_in_fifo_read, tv_in_fifo_clock, tv_in_iso,

tv in reset_b, tv_in_clock;

inout tv in i2c data;

inout [35:0] ram0 data;

output [18:0] ram0 address;

output ram0 adv ld, ram0 clk, ram0 cen b, ram0 ce b, ram0 oe b, ram0 we b;

output [3:0] ram0 bwe b;

inout [35:0] ram1 data;

output [18:0] ram1 address;

output ram1 adv ld, ram1 clk, ram1 cen b, ram1 ce b, ram1 oe b, ram1 we b;

output [3:0] ram1_bwe_b;

input clock_feedback_in;

output clock feedback out;

inout [15:0] flash data;

output [23:0] flash address;

output flash ce b, flash oe b, flash we b, flash reset b, flash byte b;

input flash sts;

output rs232 txd, rs232 rts;

input rs232 rxd, rs232 cts;

inout mouse clock, mouse data;

input keyboard clock, keyboard data;

input clock 27mhz, clock1, clock2;

output disp blank, disp clock, disp rs, disp ce b, disp reset b;

input disp data in;

output disp data out;

input button0, button1, button2, button3, button_enter, button_right,

button left, button down, button up;

input [7:0] switch;

output [7:0] led;

inout [31:0] user1, user2, user3, user4;

inout [43:0] daughtercard;

inout [15:0] systemace_data;

output [6:0] systemace address;

output systemace ce b, systemace we b, systemace oe b;

input systemace irq, systemace mpbrdy;

output [15:0] analyzer1_data, analyzer2_data, analyzer3_data,

analyzer4 data;

output analyzer1 clock, analyzer2 clock, analyzer3 clock, analyzer4 clock;

// I/O Assignments

```

```

// Audio Input and Output

assign beep= 1'b0;

// assign audio reset b = 1'b0;

// assign ac97_synch = 1'b0;

// assign ac97_sdata_out = 1'b0;

// ac97 sdata in is an input

// VGA Output

/*assign vga out red = 10'h0;

assign vga out green = 10'h0;

assign vga out blue = 10'h0;

assign vga out sync b = 1'b1;

assign vga out blank b = 1'b1;

assign vga out pixel clock = 1'b0;

assign vga out hsync = 1'b0;

assign vga out vsync = 1'b0;*/

// Video Output

assign tv_out_ycrcb = 10'h0;

assign tv_out_reset_b = 1'b0;

assign tv_out_clock = 1'b0;

assign tv_out_i2c_clock = 1'b0;

assign tv_out_i2c_data = 1'b0;

assign tv_out_pal_ntsc = 1'b0;

assign tv_out hsync b = 1'b1;

assign tv out vsync b = 1'b1;

assign tw out blank b = 1'b1;

assign tv_out_subcar_reset = 1'b0;

// Video Input

assign tv in i2c clock = 1'b0;

assign tv in fifo read = 1'b0;

assign tv in fifo clock = 1'b0;

assign tv_in_iso = 1'b0;

assign tv_in_reset_b = 1'b0;

assign tv_in_clock = 1'b0;

assign tv in i2c data = 1'bZ;

// tv in ycrcb, tv in data valid, tv in line clock1, tv in line clock2,

// tv in aef, tv in hff, and tv in aff are inputs

// SRAMs

assign ram0 data = 36'hZ;

assign ram0 address = 19'h0;

assign ram0 adv ld = 1'b0;

assign ram0 clk = 1'b0;

assign ram0 cen b = 1'b1;

assign ram0_ce \overline{b} = 1'b1;

assign ram0\_oe\_b = 1'b1;

assign ram0_we_b = 1'b1;

assign ram0_bwe_b = 4'hF;

assign ram1_data = 36'hZ;

assign ram1_address = 19'h0;

assign ram1 adv ld = 1'b0;

assign ram1_clk = 1'b0;

assign ram1 cen b = 1'b1;

assign raml ce \bar{b} = 1'b1;

assign ram1 oe b = 1'b1;

assign ram1 we b = 1'b1;

assign ram1 bwe b = 4'hF;

assign clock feedback out = 1'b0;

```

```

// clock feedback in is an input

// Flash ROM

assign flash data = 16'hZ;

assign flash address = 24'h0;

assign flash ce b = 1'b1;

assign flash_oe_b = 1'b1;

assign flash_we_b = 1'b1;

assign flash_reset_b = 1'b0;

assign flash_byte_b = 1'b1;

// flash sts is an input

// RS-232 Interface

assign rs232 txd = 1'b1;

assign rs232 rts = 1'b1;

// rs232_rxd and rs232_cts are inputs

// PS/2 Ports

// mouse clock, mouse data, keyboard clock, and keyboard data are inputs

// LED Displays

/* assign disp_blank = 1'b1;

assign disp_clock = 1'b0;

assign disp_rs = 1'b0;

assign disp_ce_b = 1'b1;

assign disp_reset_b = 1'b0;

assign disp data out = 1'b0; */

// disp data in is an input

// Buttons, Switches, and Individual LEDs

// assign led = 8'hFF;

// button0, button1, button2, button3, button enter, button right,

// button left, button down, button up, and switches are inputs

// User I/Os

// assign user1 = 32'hZ;

// assign user2 = 32'hZ;

// assign user3 = 32'hZ;

assign user4 = 32'hZ;

// Daughtercard Connectors

assign daughtercard = 44'hZ;

// SystemACE Microprocessor Port

assign systemace data = 16'hZ;

assign systemace address = 7'h0;

assign systemace ce b = 1'b1;

assign systemace we b = 1'b1;

assign systemace oe b = 1'b1;

// systemace_irq and systemace_mpbrdy are inputs

// Logic Analyzer

// assign analyzer1 data = 16'h0;

assign analyzer1 clock = 1'b1;

assign analyzer2_data = 16'h0;

assign analyzer2_clock = 1'b1;

assign analyzer3 data = 16'h0;

assign analyzer3 clock = 1'b1;

assign analyzer4 data = 16'h0;

assign analyzer4 clock = 1'b1;

```

```

// ***********************

// Generic inputs and outputs

// Reset switch = enter button

wire reset sync;

debounce reset debouncer(.reset(1'b0), .clock(clock 27mhz), .noisy(~button enter),

.clean(reset sync));

// Debug bus - wired to LEDs (invertedly) and low byte of Analyser 1 data port

wire [7:0] debug bus;

assign led[7:0] = \sim debug bus[7:0];

assign analyzer1 data[15:0] = {8'b0, debug bus};

// **********************

// Space buffer, with inputs and outputs

// Data generation subsystem wires (port A)

wire[5:0] app address;

wire[7:0] app data in, app data out;

wire write enable;

// Display subsystem wires (port B)

wire[2:0] plane_sel;

wire[63:0] data bus in;

space buffer space buffer (.addra(app address), .dina(app data out), .douta(app data in),

.wea(write enable), .clka(clock 27mhz),

.addrb(plane sel), .doutb(data bus in), .clkb(clock 27mhz));

// ***********************

// Modules for data generation subsystem

// Last modified by David Wyatt

// 2005/12/11

// Labkit button inputs

wire [4:0] controls sync;

synchronize synchronize0(.clk(clock_27mhz), .in(~button0), .out(controls_sync[0]));

synchronize synchronize1(.clk(clock_27mhz), .in(~button1), .out(controls_sync[1]));

synchronize synchronize2(.clk(clock_27mhz), .in(~button2), .out(controls_sync[2]));

synchronize synchronize3(.clk(clock_27mhz), .in(~button3), .out(controls_sync[3]));

synchronize synchronize enter(.clk(clock 27mhz), .in(~button enter),

.out(controls sync[4]));

// PS/2 Mouse

wire [2:0] mouse btn;

wire [11:0] mouse x, mouse y;

ps2 mouse xy my mouse(.clk(clock 27mhz), .reset(reset sync), .ps2 clk(mouse clock),

.ps2 data(mouse data), .mx(mouse x), .my(mouse y),

.btn click(mouse btn));

// AC97 Audio

wire [7:0] from_ac97_data, to_ac97_data;

wire ready;

audio a(clock_27mhz, ac97_reset, from_ac97_data, to_ac97_data, ready,

audio reset b, ac97 sdata out, ac97 sdata in,

ac97 synch, ac97 bit clock);

// Loopback input AC97 audio to output

assign to_ac97_data = from_ac97_data;

// detect clock cycle when READY goes 0 -> 1

// f(READY) = 48khz

wire new frame;

req old ready;

always @ (posedge clock 27mhz) old ready <= reset sync ? 0 : ready;

```

```

assign new frame = ready & ~old ready;

// Instantiate the cascade integrator comb filter, a Xilinx Coregen module

wire[18:0] filter_output;  // Filter output - 19 bits wide, according to Coregen...

// Filter output ready signal

wire filter output ready;

low pass filter low pass filter1(.DIN(from ac97 data), .ND(new frame), .CLK(clock 27mhz),

.DOUT(filter output), .RDY(filter output ready));

// ASCII string display

wire [127:0] title;

display_string my_display(.reset(reset_sync), .clock 27mhz(clock 27mhz),

.string data(title), .disp blank(disp blank),

.disp clock(disp clock), .disp rs(disp rs), .disp ce b(disp ce b),

.disp_reset_b(disp_reset_b), .disp_data_out(disp_data_out));

// Application selection (including Muxes to select appropriate inputs)

// MUX connectors

wire [5:0] app address0, app address1, app address2, app address3, app address4,

app address5;

wire [7:0] app data in0, app data in1, app data in2, app data in3, app data in4,

app_data_in5;

wire [7:0] app_data_out0, app_data_out1, app_data_out2, app_data_out3, app_data_out4,

app data out5;

wire write enable0, write enable1, write enable2, write enable3, write enable4,

write enable5;

wire [127:0] title0, title1, title2, title3, title4, title5;

// MUXes

mux_8input_6bit app_address_mux(.in0(app_address0), .in1(app_address1),

.in2(app address2), .in3(app address3), .in4(app address4),

.in5(app address5), .in6(6'b0), .in7(6'b0), .selector(switch[2:0]),

.out(app address));

mux 8input 8bit app data in mux(.in0(app data in0), .in1(app data in1),

.in2(app data in2), .in3(app data in3), .in4(app data in4),

.in5(app_data_in5), .in6(8'b0), .in7(8'b0), .selector(switch[2:0]),

.out(app_data_in));

mux_8input_8bit app_data_out_mux(.in0(app_data_out0), .in1(app_data_out1),

.in2(app_data_out2), .in3(app_data_out3), .in4(app_data_out4),

.in5(app data out5), .in6(8'b0), .in7(8'b0), .selector(switch[2:0]),

.out(app data out));

mux 8input 1bit write enable mux(.in0(write enable0), .in1(write enable1),

.in2(write_enable2), .in3(write_enable3), .in4(write_enable4),

.in5(write enable5), .in6(1'b0), .in7(1'b0), .selector(switch[2:0]),

.out(write enable));

mux 8input 128bit title mux(.in0(title0), .in1(title1), .in2(title2), .in3(title3),

.in4(title4),

.in5(title5), .in6(128'b0), .in7(128'b0), .selector(switch[2:0]), .out(title));

// Application reset controller

wire reset;

application reset application reset1(.selector(switch[2:0]), .clock(clock 27mhz),

.reset(reset));

// Applications

// -----

// 0: 3D Pong

pong pong1(.app_address(app_address0), .app_data_in(app_data_in0),

.app_data_out(app_data_out0), .write_enable(write_enable0),

.controls_sync(controls_sync), .clock(clock_27mhz), .reset(reset), .title(title0),

.pos x(mouse x[6:4]), .pos y(mouse y[6:4]), .mclick(mouse btn));

// 1: 2D Game-of-Life cellular automaton

```

```

cell aut 2D cell aut 2D1(.app address(app address1), .app data in(app data in1),

.app_data_out(app_data_out1), .write_enable(write_enable1),

.controls_sync(controls_sync), .clock(clock_27mhz), .reset(reset), .title(title1));

// 2: 3D cellular automaton

cell aut 3D cell aut 3D1(.app address(app address2), .app data in(app data in2),

.app data_out(app_data_out2), .write_enable(write_enable2),

.controls sync(controls sync), .clock(clock 27mhz), .reset(reset), .title(title2));

// 3: Music visualiser

music visualizer music visualizer1(.app address(app address3),

.app data in(app data in3), .app data out(app data out3), .write enable(write enable3),

.controls sync(controls sync), .clock(clock 27mhz), .reset(reset), .title(title3),

.filter output ready(filter output ready), .filter output(filter output));

// 4: MIT triple-letter cube

mit mit1(.app address(app address4), .app data in(app data in4),

.app data out(app data out4), .write enable(write enable4),

.controls sync(controls sync), .clock(clock 27mhz), .reset(reset), .title(title4));

// 5: 3D spinning shapes

spinning_shapes spinning_shapes1(.app_address(app_address5), .app_data_in(app_data_in5),

.app_data_out(app_data_out5), .write_enable(write_enable5),

.controls_sync(controls_sync), .clock(clock_27mhz), .reset(reset), .title(title5),

.debug(debug_bus), .mouse_x(mouse_x), .mouse_y(mouse_y));

// **********************

// Modules for display subsystem

// Last modified by David Wyatt

// 2005/12/6

// Display on the cube:

//----

wire[63:0] data_bus_out;

wire[7:0] plane out;

wire toggled;

// Data output module

data output module data output module1(.clock(clock 27mhz), .reset(reset sync),

.plane sel(plane sel), .plane out(plane out), .data bus in(data bus in),

.data bus out(data bus out), .toggled(toggled));

// Configure it for a system clock frequency of 27MHz

defparam data output module1.input clock freq = 27000000;

// Actual inputs and outputs!

assign user1 = ~data bus out[31:0];

assign user2 = ~data bus out[63:32];

assign user3 = \{24'b0, plane out[7:0]\};

// Debugging

// assign led = ~plane out[7:0];

// assign analyzer1 clock = clock 27mhz;

// SVGA display on a monitor:

//-----

// Parameters to configure the colours of the output on the screen

parameter OFF LED = 4'h0;

parameter DIMMED LED = 4'h4;

parameter LIT LED = 4'hF;

parameter WIREFRAME SHADE = 8'h7F; // Grey shade of the wireframe cube outline

// Parameters for screen display size (in pixels)

```

```

// A good combination is D=50, Dsin(theta) = 45, Dcos(theta) = 27, offsets x,y = 20

// But for the moment we will use a 45 degree projection angle for simplicity of grid

lines...

parameter LED RADIUS = 3;

// Radius of circles to represent LEDs, maximum 8

parameter D = 47;

// Linear LED spacing (corresponds to real 3D spacing)

parameter D SIN THETA = 34;

// Projection of a Z-step of size D into the X direction

parameter D COS THETA = 34;

// Projection of a Z-step of size D into the Y direction

parameter OFFSET X = 10;

// Distance of graphic from left screen edge

parameter OFFSET Y = 10;

// Distance of graphic from top screen edge

// Renderer - does orthographic 3d to draw projection of cube on a screen buffer

wire sbuffer write enable;

wire [9:0] sbuffer write col, sbuffer write row, sbuffer read col, sbuffer read row;

wire [3:0] sbuffer data in, sbuffer data out;

renderer renderer1(.clock(clock 27mhz), .reset(reset sync), .voxel plane(plane sel),

.voxel data bus(data bus out),

.highlight enable(switch[7]), .highlight mode(switch[3]),

.highlighted plane(switch[6:4]),

.screen rdata out(sbuffer data in), .screen row(sbuffer write row),

.screen column(sbuffer write col),

.screen write enable(sbuffer write enable));

// Configure the colours and scale of the screen output

defparam renderer1.OFF_LED = OFF_LED;

defparam renderer1.DIMMED LED = DIMMED LED;

defparam renderer1.LIT_LED = LIT_LED;

defparam renderer1.LED RADIUS = LED RADIUS;

defparam renderer1.D = D;

defparam renderer1.D SIN THETA = D SIN THETA;

defparam renderer1.D COS THETA = D COS THETA;

defparam renderer1.\overline{OFFSET} X = \overline{OFFSET} X;

defparam renderer1.OFFSET Y = OFFSET Y;

// Clock manager to generate the 40MHz-ish clock (actually 40.5MHz) needed for the video

signal...

// Copied from Lab 4 - I hope this works!

wire clock 40mhz_unbuf, clock_40mhz;

DCM vclk1(.CLKIN(clock_27mhz),.CLKFX(clock_40mhz_unbuf));

// synthesis attribute CLKFX_DIVIDE of vclk1 is 2

// synthesis attribute CLKFX MULTIPLY of vclk1 is 3

// synthesis attribute CLK FEEDBACK of vclk1 is NONE

// synthesis attribute CLKIN PERIOD of vclk1 is 37

BUFG vclk2(.O(clock 40mhz),.I(clock 40mhz unbuf));

// Screen buffer (wrapped in a module) - stores 800 x 600 record of the top 4 bits of the

screen's red channel (!)

screen buffer wrapper screen buffer wrapper1(.write clock(clock 27mhz),

.write col(sbuffer write col),

.write row(sbuffer write row), .write data(sbuffer data in),

.write enable(sbuffer write enable), .read clock(clock 40mhz),

.read_col(sbuffer_read_col), .read_row(sbuffer_read_row),

.read data(sbuffer data out));

// SVGA video interface module - based on Lab 4

wire [9:0] hcount;

wire [9:0] vcount;

wire hsync, vsync, blank;

svga svga1(.vclock(clock_40mhz), .hcount(hcount), .vcount(vcount), .hsync(hsync),

.vsync(vsync), .blank(blank));

assign sbuffer read col[9:0] = hcount[9:0];

assign sbuffer_read_row[9:0] = vcount[9:0];

// Small module to draw a wireframe outline of the cube on the screen

// Has a single output, wireframe/outline, which when high causes the current pixel to be

```

```

grey

wire outline;

wireframe generator wireframe generator1(.hcount(hcount), .vcount(vcount),

.wireframe(outline));

// Configure the scale of the screen output

defparam wireframe generator1.D = D;

defparam wireframe generator1.D SIN THETA = D SIN THETA;

defparam wireframe generator1.D COS THETA = D COS THETA;

defparam wireframe_generator1.OFFSET_X = OFFSET_X;

defparam wireframe_generator1.OFFSET_Y = OFFSET_Y;

// SVGA Output - based on Lab 4.

// In order to meet the setup and hold times of the AD7125, we send it clock_40mhz.

assign vga out red = (sbuffer data out[3:0]) ? {sbuffer data out[3:0], 4'b0} : (outline ?

WIREFRAME SHADE: 8'h0);

assign vga out green = (sbuffer data out[3:0]) ? 8'b0 : (outline ? WIREFRAME SHADE :

assign vga out blue = (sbuffer data out[3:0]) ? 8'b0 : (outline ? WIREFRAME SHADE :

8'h0);

assign vga_out sync b = 1'b1;

// not used

assign vga_out_blank b = ~blank;

assign vga_out_pixel_clock = clock_40mhz;

assign vga_out_hsync = hsync;

assign vga_out_vsync = vsync;

```

# Appendix B: Data generation subsystem code

Note that the following files were used as provided by the 6.111 website:

- display\_string.v <<a href="http://web.mit.edu/6.111/www/f2005/code/display\_string.v">http://web.mit.edu/6.111/www/f2005/code/display\_string.v</a>

- ps2\_mouse.v < <a href="http://web.mit.edu/6.111/www/f2005/code/ps2\_mouse.v">http://web.mit.edu/6.111/www/f2005/code/ps2\_mouse.v</a> (parameters MAX\_X and MAX\_Y were both changed to 95)

- audio.v < <a href="http://web.mit.edu/6.111/www/f2005/handouts/lab3.v">http://web.mit.edu/6.111/www/f2005/handouts/lab3.v</a>>

- debounce.v < http://web.mit.edu/6.111/www/f2005/handouts/debounce.v >

- synchronize.v < <a href="http://web.mit.edu/6.111/www/f2005/handouts/synchronize.v">http://web.mit.edu/6.111/www/f2005/handouts/synchronize.v</a>

#### 1. application\_reset.v

endmodule

```

module application_reset(selector, clock, reset);

input [2:0] selector;

input clock;

output reset;

reg [2:0] prev_selector;

reg reset;

always @ (posedge clock)

begin

if (prev_selector == selector)

reset <= 1'b0;

else begin

reset <= 1'b1;

prev_selector <= selector;

end

end</pre>

```

#### 2. cell\_aut\_2d.v

```

module cell aut 2D(app address, app data in, app data out, write enable, controls sync,

clock, reset, title);

// Standard application inputs

input [7:0] app_data_in;

input [4:0] controls_sync;

input clock, reset;

// Standard application outputs

output [5:0] app address;

output [7:0] app_data_out;

output write enable;

output [127:0] title;

assign title = "Cell Automata 2D";

reg [5:0] app address;

reg [7:0] app_data_out;

// -----Cell aut 2D-----

// Register to store state of entire cube

reg [511:0] cube;

reg [10:0] state counter; // [3:0] - 16 substates; [9:4] - 64 LEDs, [10] - Allow time to

load to space buffer

reg [3:0] cell counter;

// Counts the number of live neighbouring cells

parameter pattern ring =

parameter pattern glider

64 ^{\circ} ^{

parameter pattern_ship =

wire clock 2khz;

clock divider cell aut 2D clock1 divider (clock, clock 2khz);

defparam cell aut 2D clock1 divider.ratio = 13500;

// Cell_aut_2D operates always in write mode wrt space_buffer

assign write enable = 1'b1;

always @ (posedge clock)

// Handle new pattern requests

if (reset || controls sync[0])

begin

cube <= 512'b0;

state counter <= 1024;

end

else if (controls sync[1])

begin

cube <= {448'b0, pattern ring};</pre>

state_counter <= 1024;</pre>

end

else if (controls sync[2])

cube <= {448'b0, pattern glider};

state counter <= 1024;</pre>

```

```

end

else if (controls_sync[3])

cube <= {448'b0, pattern ship};

state counter <= 1024;

else if (clock 2khz)

begin

state counter <= state counter + 1;</pre>

// Calculate next cube state

if (state counter < 1024)

case (state counter[3:0])

0: if (state_counter[9:4] == 0) cube[511:64] <= cube[447:0];

1: cell counter <= 0;

2: cell counter <= cell counter + cube[(state counter[9:4] - 8 - 1) % 64 + 64];

3: cell counter <= cell counter + cube[(state counter[9:4] - 8) % 64 + 64];

4: cell counter <= cell counter + cube[(state counter[9:4] - 8 + 1) % 64 + 64];

5: cell counter <= cell counter + cube[(state counter[9:4] - 1) % 64 + 64];

6: cell counter <= cell counter + cube[(state counter[9:4] + 1) % 64 + 64];

7: cell_counter <= cell_counter + cube[(state_counter[9:4] + 8 - 1) % 64 + 64];

8: cell_counter <= cell_counter + cube[(state_counter[9:4] + 8) % 64 + 64];

9: cell_counter <= cell_counter + cube[(state_counter[9:4] + 8 + 1) % 64 + 64];

10: case (cell counter)

3: cube[state counter[9:4]] <= 1'b1;</pre>

// Generate living cell

2: cube[state counter[9:4]] <= cube[state counter[9:4]]; // Maintain

living cell

// Cell dies

default: cube[state counter[9:4]] <= 1'b0;</pre>

(isolation/overcrowding)

endcase

endcase

// Store cube state into space buffer

else if (state counter < 1024 + 64)

most recent

// Life state is on the top plane

app data out[0] <= cube[8*state counter[5:0]+0];</pre>

app data out[1] <= cube[8*state counter[5:0]+1];</pre>

app data out[2] <= cube[8*state counter[5:0]+2];</pre>

app_data_out[3] <= cube[8*state_counter[5:0]+3];</pre>

app data out[4] <= cube[8*state counter[5:0]+4];</pre>

app_data_out[5] <= cube[8*state_counter[5:0]+5];</pre>

app data out[6] <= cube[8*state counter[5:0]+6];</pre>

app data out[7] <= cube[8*state counter[5:0]+7];</pre>

end

```

endmodule

#### 3. cell\_aut\_3d.v

```

module cell_aut_3D(app_address, app_data_in, app_data_out, write_enable, controls_sync,

clock, reset, title);

// Standard application inputs

input [7:0] app_data_in;

input [4:0] controls_sync;

input clock, reset;

```

```

// Standard application outputs

output [5:0] app address;

output [7:0] app data out;

output write enable;

output [127:0] title;

assign title = "Cell Automata 3D";

reg [5:0] app address;

reg [7:0] app data out;

// -----Cell aut 3D-----

// Register to store state of cube

reg [511:0] cube;

reg [511:0] prev cube;

// Predefined game states

parameter pattern_empty = 512'b0;

parameter pattern_row = {192'b0,32'b0,8'b00111000,24'b0,256'b0};

parameter pattern_corners = {8'b10000001, 48'b0, 8'b10000001, 384'b0, 8'b10000001, 48'b0,

8'b10000001};

parameter pattern random = {256'b0,

64'b10001101001001\overline{0}1000010010000010010010010010001000101001001001001, 192'b0};

// 1khz clock -- For updating space buffer contents

wire clock 27khz;

clock_divider cell_aut_3D_clock1_divider (clock, clock_27khz);

defparam cell_aut_3D_clock1_divider.ratio = 1000;

// Cell aut 3D operates always in write mode wrt space buffer

assign write enable = 1'b1;

//

Cell aut 3D works like a 1024 x 32 state FSM:

//

* First 512 x 32 states for computing next state of the cube

//

- 512 main states for each of the 512 LEDs

//

- 32 sub states for adding up neighbouring cell contents and deciding the next

cell state

* Next 64 states used for updating space buffer with contents of cube register.

//

* Remaining states are "do nothing" states

//

// Counter for maintaining state of game machine

reg [14:0] state counter;

reg [4:0] cell counter = 0;

always @ (posedge clock)

if (reset)

begin

cube <= pattern_empty;

end

else if (clock 27khz) begin

// Check if new pattern has been requested (or if application has been reset)

// If a pattern has been requested, jump to state 16384 to skip computing the next state

and

// start displaying the next state.

if (controls_sync[0] || reset)

begin

cube <= pattern_empty;</pre>

state counter <= 16384;

cell counter <= 0;</pre>

end

```

```

else if (controls sync[1])

begin

cube <= pattern row;</pre>

state counter <= 16384;

cell counter <= 0;

end

else if (controls_sync[2])

begin

cube <= pattern_corners;</pre>

state counter <= 16384;

cell counter <= 0;

else if (controls sync[3])

begin

cube <= pattern_random;</pre>

state counter <= 16384;

cell counter <= 0;

end

// The "compute next cube" states

else if (state counter < 16384)

begin

// Select the appropriate sub-state

case(state counter[4:0])

// Make copy of previous state of cube (to be used as a source for calculating

next state),

// but only right at the beginning (before any states have cells have been

manipulated)

0: if (state counter[13:5] == 0) prev cube <= cube;

// Add up neighbouring cells one by one.

// Note that state counter[13:5] identifies the cell that we are manipulating

1: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 - 8 - 1 +

512) % 512];

2: cell_counter <= cell_counter + prev_cube[(state_counter[13:5] - 64 - 8 + 512) %

5121:

3: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 - 8 + 1 +

512) % 5121;

4: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 - 1 + 512) %

512];

5: cell_counter <= cell_counter + prev_cube[(state_counter[13:5] - 64 + 512) %

5121:

6: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 + 1 + 512) %

5121;

7: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 + 8 - 1 +

512) % 512];

8: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 + 8 + 512) %

5121;

9: cell counter <= cell counter + prev cube[(state counter[13:5] - 64 + 8 + 1 +

512) % 512];

10: cell counter <= cell counter + prev cube[(state counter[13:5] - 8 - 1 + 512) %

5121;

11: cell counter <= cell counter + prev cube[(state counter[13:5] - 8 + 512) %

512];

12: cell_counter <= cell_counter + prev_cube[(state_counter[13:5] - 8 + 1 + 512) %

512];

13: cell counter <= cell counter + prev cube[(state counter[13:5] - 1 + 512) %

5121;

// cell counter <= cell counter + prev cube[(state counter[13:5]) % 512]; (Don't</pre>

add the cell itself)

14: cell counter <= cell counter + prev cube[(state counter[13:5] + 1) % 512];

```

```

15: cell counter <= cell counter + prev cube[(state counter[13:5] + 8 - 1) % 512];

16: cell_counter <= cell_counter + prev_cube[(state_counter[13:5] + 8) % 512];</pre>

17: cell counter <= cell counter + prev cube[(state counter[13:5] + 8 + 1) % 512];

18: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 - 8 - 1) %

512];

19: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 - 8) %

512];

20: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 - 8 + 1) %

512];

21: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 - 1) %

512];

22: cell counter <= cell counter + prev cube[(state counter[13:5] + 64) % 512];

23: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 + 1) %

512];

24: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 + 8 - 1) %

5121:

25: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 + 8) %

512];

26: cell counter <= cell counter + prev cube[(state counter[13:5] + 64 + 8 + 1) %

512];

// After counting the number of neighbouring cells, decide the next state for the

active

// cell, and reset the cell counter.

27: case(cell counter)

2: cube[state counter[13:5]] <= prev cube[state counter[13:5]];</pre>

3: cube[state counter[13:5]] <= 1'b1;</pre>

4: cube[state counter[13:5]] <= 1'b1;

default: cube[state counter[13:5]] <= 1'b0;</pre>

endcase

28: cell counter <= 0;

endcase

state counter <= state counter + 1;</pre>

end

// Update contents of space buffer

// state counter[5:0] identifies the column of cells we are updating (the space buffer

takes in

// 8 cells at a time (i.e. 1 column)

else if ((state counter >= 16384) && (state counter < 16384 + 64))

app_address <= state_counter[5:0];</pre>

app data out[7] <= cube[8*state counter[5:0]+7];</pre>

app_data_out[6] <= cube[8*state_counter[5:0]+6];</pre>

app data out[5] <= cube[8*state counter[5:0]+5];</pre>

app data out[4] <= cube[8*state counter[5:0]+4];</pre>

app data out[3] <= cube[8*state counter[5:0]+3];</pre>

app data out[2] <= cube[8*state counter[5:0]+2];</pre>

app_data_out[1] <= cube[8*state_counter[5:0]+1];</pre>

app_data_out[0] <= cube[8*state_counter[5:0]+0];</pre>

state_counter <= state_counter + 1;</pre>

end

// The "do nothing state"

else state counter <= state counter + 1;</pre>

end

endmodule

```

#### 4. clock\_divider.v

```

module clock divider(clock in, clock out);

input clock in;

output clock out;

reg clock_out;

parameter ratio = 1000;