6.205

Sequential Logic II:

Sequential Logic Timing

Intro to Finite State Machines

#### Administrative

• Week 02's content is due tomorrow

Week 03's comes out on Thursday

#### Think Like a Hardware Engineer

Many programming constructs/patterns are done to help you, the person, rather than reflect the underlying hardware design

Part of becoming a good hardware-focused engineer is learning how to give the machine what it wants.

For example...object oriented programming. Who is that really for?

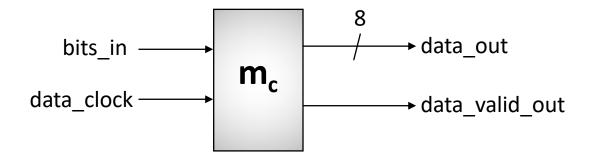

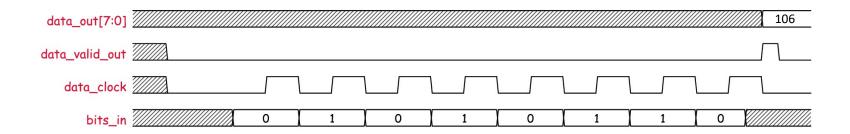

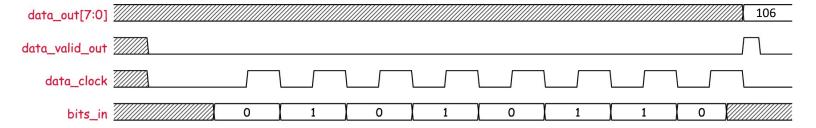

#### Consider this task: Data Deserializer

- Single bits come in **Isb-first\*** one after the other on a clock.

- Module assembles them into 8-bit bytes and sends them out

## The solution must obviously involve an Indexable array

- What are you assuming?

- What functionality/capability can be stripped away?

- Are you doing what you're doing...

- for you? (not right answer...you don't matter)

- or the FPGA? (right answer...it is what matters)

#### So ugh...

```

logic [7:0] buffer;

logic [2:0] buffer_ind;

always_ff @(posedge clk)begin

buffer[buffer_ind] <= bit_in;

buffer_ind <= buffer_in +1;

end</pre>

```

Oh but I gotta take care of wrap-around

```

logic [7:0] buffer;

logic [2:0] buffer_ind;

always_ff @(posedge clk)begin

buffer[buffer_ind] <= bit_in;

if (buffer_ind > BUFFER_LIMIT)begin

buffer_ind <= 0;

end else begin

buffer_ind <= buffer_in +1;

end

end</pre>

```

Oh but backwards

```

logic [7:0] buffer;

logic [2:0] buffer_ind;

always_ff @(posedge clk)begin

buffer[7-buffer_ind] <= bit_in;

if (buffer_ind > BUFFER_LIMIT)begin

buffer_ind <= 0;

end else begin

buffer_ind <= buffer_in +1;

end

end</pre>

```

#### 6 hours later...

Your code is full of stuff like this

```

buffer_ind <= 2+ BUFFER_LIMIT - buffer_ind - 1 + new_old_buffer_ind_a;</pre>

```

• You've gotten this gross functionality "working" but it may not be beneficial for the problem at hand.

#### What do indexable arrays give us?

- "Random" Access to an array (in other words, at any point in time I can access/modify any element of the array)

- As we'll see, large-scale Randomly accessible memory is a burden. You do not want to use it unless you need to!

- Do we need that here?

#### Reconsider this task: Data Deserializer

- The bits are coming in in order of lsb-first

- They're only ever going to go in one place, and we'll use them in order they come in....we don't need array access.

#### Make a queue or fifo-like structure

Just push the data in as it comes in

```

logic [7:0] buffer;

always_ff @(posedge clk)begin

buffer <= {buffer[6:0], bit_in};

end</pre>

```

Oh is that backwards? No biggie...

```

logic [7:0] buffer;

always_ff @(posedge clk)begin

buffer <= {bit_in, buffer[7:1]};

end</pre>

```

"SHIFT BUFFER"....a simple FIFO for bits!

### Another Thing: / and %

- We've done nothing in this class so far that needs these two operators.

- In the land of digital design, / and % should be avoided at all costs until they are absolutely needed.

- They are extremely expensive operations to perform

- We'll see how expensive they are in future lectures and labs.

- No need to use these for a cycle counter or for anything so far

#### The Cycle Counter from Lab 01

- Build a thing that starts at zero and counts up to a number, then goes back to 0.

- Every clock cycle you are asking this thing to perform 32 bit integer division and find the remainder....that is a monumental task to just count a number and wrap it around

#### Simpler, Cheaper

• A 32 bit add, a 32 bit compare, an if/else

#### Now in some cases...

The tools may be able to optimize an atrocious line like this one for you, but that can depend on things it knows...and it doesn't know all the stuff you know.

The tool doesn't really know that count will never be greater than period...it will likely synthesize a device that can do % for all possible count start values\*

#### And at the very least...

• The closer your Verilog matches what should get built, the less you're asking of the tool.

• Tools will always let you down so you want to help them out as much as possible.

#### Simulation vs. Reality

- / and % may work in simulation, but likely not in real life.

- Be aware of that.

- You can compute pi to 1000 digits "instantaneously in simulation"...that does not mean it can be done in real life

### Asynchronous vs. synchronous reset

There's very little to no reason to have an asynchronous reset in our class, especially right now

Don't need this. Don't' do:

## Asynchronous vs. <u>synchronous</u> <u>reset</u>

Just have the flip flop sensitivity list be the positive edge of the clock

## Only thing clocking a Flip Flop should be our *high-speed clock*

Do not have numerous sequential numerous blocks all being clocked by different signals

#### HORRIBLE, BAD, DO NOT DO:

```

always_ff @(posedge a)begin

//stuff

end

always_ff @(posedge b)begin

//other stuff

end

always_ff @(posedge c)begin

//other other stuff

end

```

Can make simulations mismatch reality

Can make designs not meet timing and fail

Will be cludge code that will hurt you

#### **INSTEAD DO:**

```

always_ff @(posedge clk)begin

if (a)begin

//stuff

end else if (b) begin

//other stuff

end else if (c) begin

//other other stuff

end

end

```

Reliable Design Practice

Simulations more likely to match reality

Timing easier to meet

#### Or if you really need things to happen on the "edge" of a non-clock signal...

Remember old signal values and compare

```

always_ff @(posedge clk)begin

old_a <= a;

old_b <= b;

old_c <= c;

if (a && !old_a)begin //on the rising edge of a

//stuff

end else if (b && !old_b)begin //on the rising edge of b

//other stuff

end else if (c && !old_c) begin //on the rising edge of c

//other other stuff

end

end</pre>

```

#### Clocks are Special

Clock signals get special treatment inside the FPGA

• Get to priority routing, go down special "clock lines" to minimize skew (future class)

Making lots of signals "clocks" can cause congestion and the entire design to fail

### Sequential Logic

#### Registers, Latches, and Flip-Flops

- The terminology is a mess for historical reasons and just people in general, including myself. Here's one interpretation:

- A "register" is something that holds a value. Flip-flops and Latches are registers

## D Flip-Flop Registers Give Us A Few Critical Capabilities

- We can store values for later use (simple memory)

- We can sample values at precise times

- A rising edge is as close to a delta-function like event as we can get

- We can design in stages:

- Allow us to non-destructively limit signal propagation which prevents:

- Combinational loops (last week)

- Glitches (today)

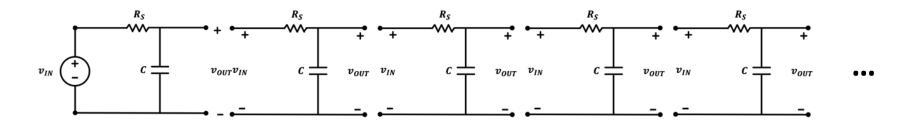

#### All Electronics are Non-Ideal

- Inherent to the logic is the need to charge and/or discharge parasitic capacitances and inductances through non-0 value resistances

- As 8.02, or 6.200/6.002 will have shown, this has an inherent time constant involved with it

- ...meaning a finite time at which it will respond given a change

- Obviously we don't want this, but I didn't want MIT to start using Okta for login stuff. What are you going to do? So it goes

### When one digital circuit drives another digital circuit

• Inputs change outputs...but takes time

# The more complex/more layers/the more delay you'll get

- Each individual "stage" needs to charge up/down before it can influence the next stage.

- Very complicated/deep logic will take time

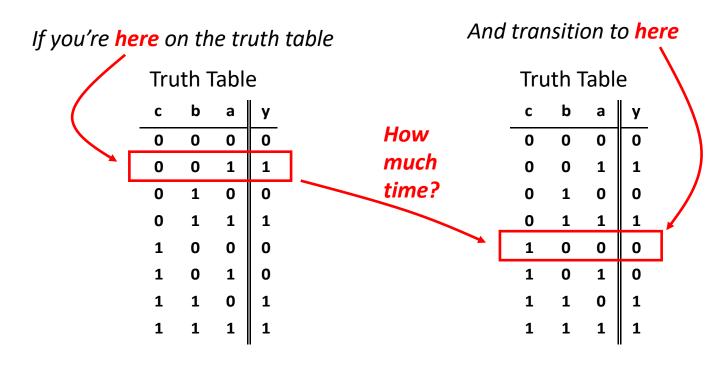

#### It'll take time to transition

- Response of a function will take time (and energy)

- So if we move around on a truth table it can't be instantaneous

### Digital Delays

For a given digital device, we need to quantify the delay

- Utilize two different numbers:

- For a given change at the inputs to a digital system:

- Contamination Delay ( $t_{cd}$ ): How long before the system will start to respond at its output?

- Propagation Delay  $(t_{pd})$ : How long until we can be sure the system has updated to new value (stabilized)?

#### The Combinational Contract

- 1. No Promises during XXXXX

- 2. Default (conservative) spec:  $t_{CD} = 0$

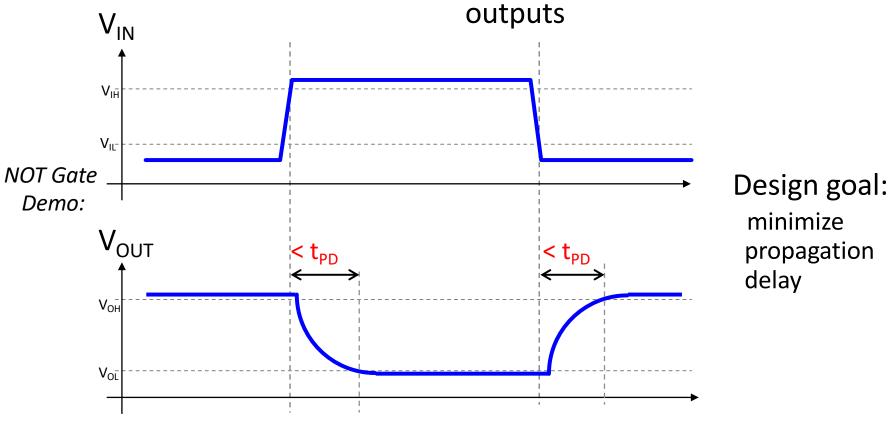

### Worst Case: Propagation Delay

An <u>upper bound</u> on the delay from valid inputs to valid outputs

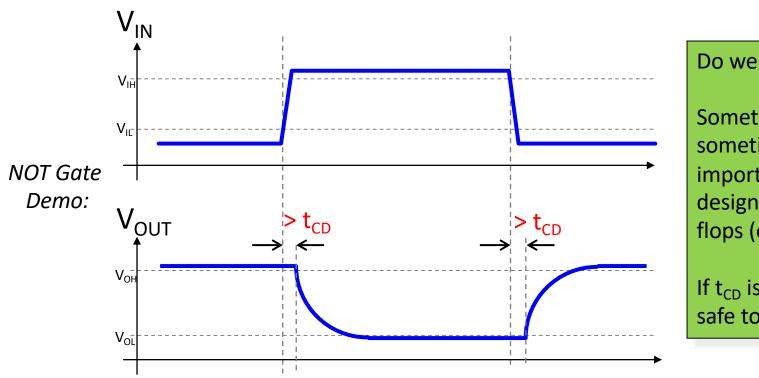

#### Best Case: Contamination Delay

Contamination delay( $t_{CD}$ ):

A <u>lower bound</u> on the delay from invalid inputs to invalid outputs

Do we really need  $t_{CD}$ ?

Sometimes yes, sometimes no... it'll be important when we design circuits with flops (coming next!)

If t<sub>CD</sub> is not specified, safe to assume it's **0**.

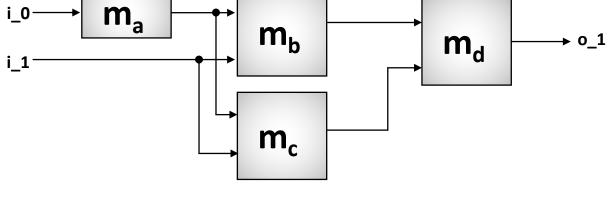

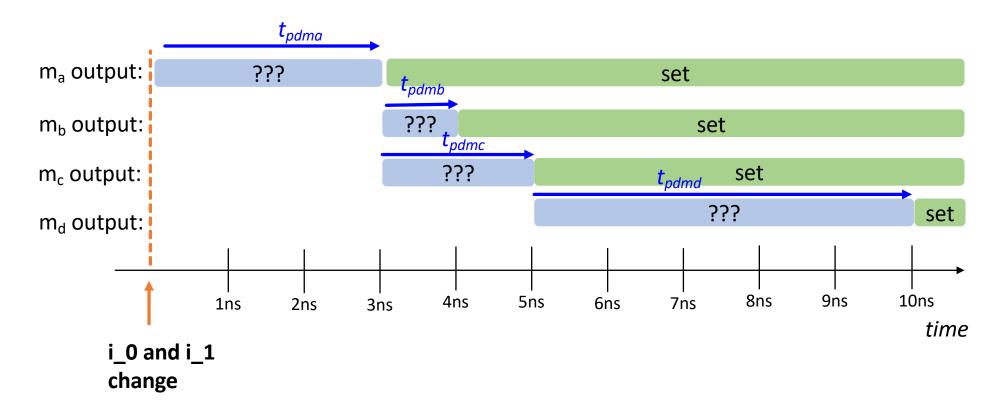

#### Review: Example System

i\_0

#### • Let's assume:

- $m_a$  has  $t_{pd}$  = 3ns

- $m_b$  has  $t_{pd} = 1$ ns

- $m_c$  has  $t_{pd} = 2ns$

- $m_d$  has  $t_{pd} = 5$ ns

- All four modules have  $t_{cd} = 0$ ns

#### • What is:

- i\_0 to o\_1 t<sub>pd</sub>?

- i\_1 to o\_1 t<sub>pd</sub>?

- t<sub>cd</sub> of system?

- Critical Path of the system and t<sub>pd</sub>?

### Timing Diagram

The t<sub>pd</sub> on any stage/module can't start being used until all inputs to it are set/stable:

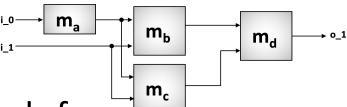

### Timing Diagram

Additionally: the "unknown" periods for subsequent outputs are quite large

Downstream outputs can be undefined for long time! Undefined things still take on values

### From the Outside

- If all you see is o\_1 how can you actually determine what is valid and what isn't?

- Is that 1'b1 on o\_1 valid or invalid? Who knows?

- Unless you know when you put in values and know the total t<sub>pd</sub> of system very hard to discern what is good and what isn't.

## Another Way to Look At Problem

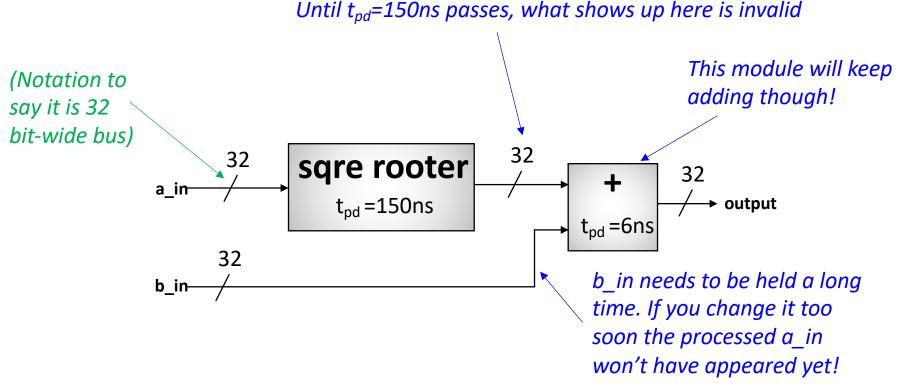

- You have a system, takes in two numbers, a\_in and b\_in and produces an output.

- System calculates square root of a\_in and then adds b\_in to it

## Another Problem (being a real downer today, I know...)

Consider simple addition in binary (or any base):

- Notice how we need to calculate the lower digits first before we calculate the upper digits?

- Uh Oh...

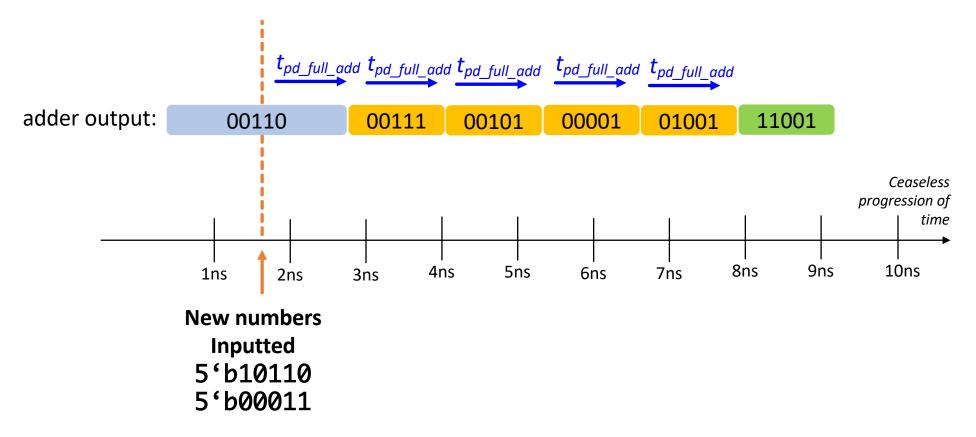

## Timing Diagram of Add

Lots of invalids before the valid result!

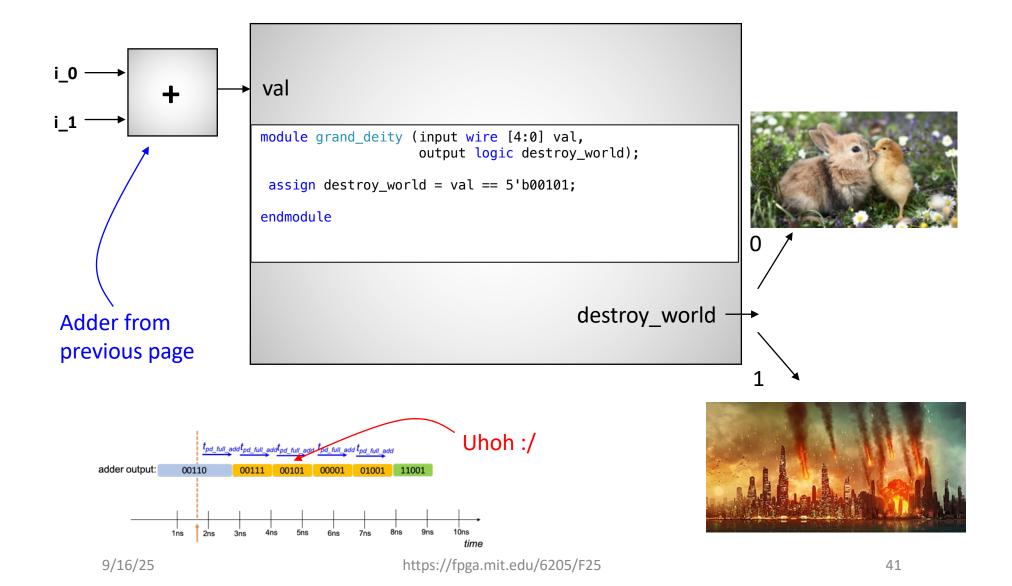

## What if we then had this circuit?

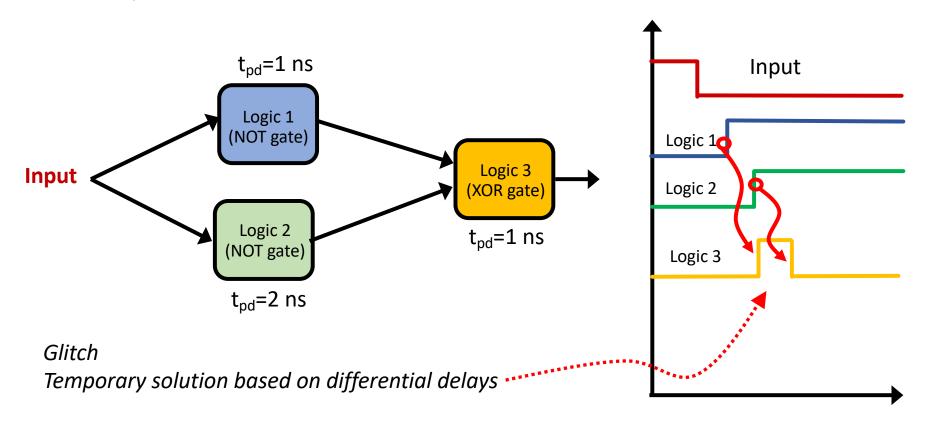

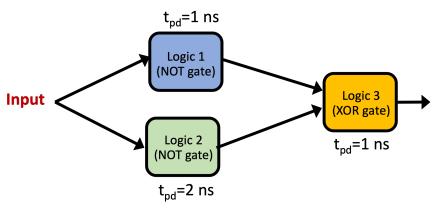

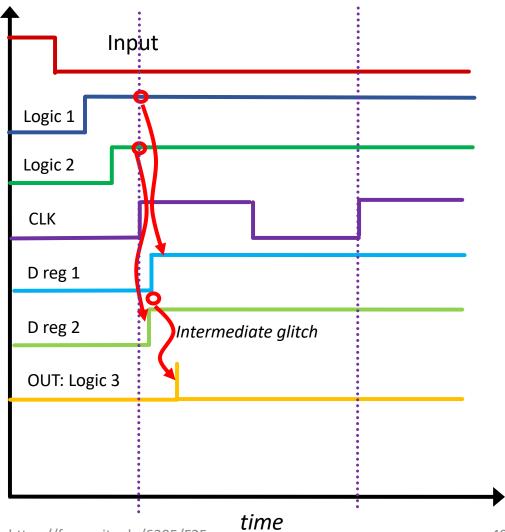

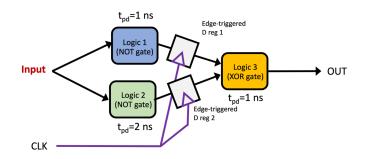

### Combinational Glitches!

- Combinational glitches arise when outputs transition through unintended outputs in response to transitioning inputs

- Caused by differences in overall **OR** internal delays of logic

| a_in | b_out |

|------|-------|

| 0    | 1     |

| 1    | 1     |

System should always have 1 as output, but during transitions from  $0 \rightarrow 1$  or  $1 \rightarrow 0$ , b\_out will glitch to 0.

## Glitches Will Happen

- Inherent when you have complex and DEEP combinational logic!

- Perform calculations on irrelevant information

- Waste energy

- Very hard to debug

- Extremely difficult to design with reliably at scale

- Too many related time constants

- Too many invalid values

- Our only hope is to encode our data in glitchminimizing ways and limit the range that combinational glitches can propagate (next up)

### Glitches can be hard to find

- Let's say t<sub>pd</sub> = 1ns (conservative)

- Human is the consumer

- You push the button...

- System stabilizes before the photons emitted from the LEDs have even reached your eye

- Human eye can only detect up to ~0.01s

phenomena...lol 6 or 7 orders of magnitude difference

- Basically we can't appreciate the glitches...but they can be there.

### So How to Fix this?

- Every combinational circuit has delays regarding how slowly (or quickly) its outputs change in response to inputs, and this varies based on design/complexity

- t<sub>cd</sub> minimum time input takes to start to change output

- t<sub>pd</sub> maximum time input takes to finish changing output

SV

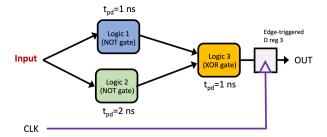

#### Previous page:

```

logic inputt, outputt;

logic o1, o2, o3;

//assume modules are combinational:

not_gate_a nga(.val_in(inputt), .val_out(o1));

not_gate_b ngb(.val_in(inputt)), .val_out(o2));

xor_gate xg (.vala_in(o1), .valb_in(o2), val_out(o3));

assign outputt = o3;

```

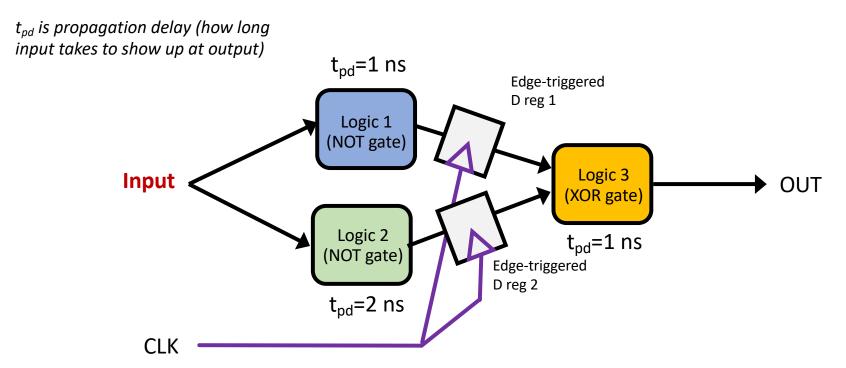

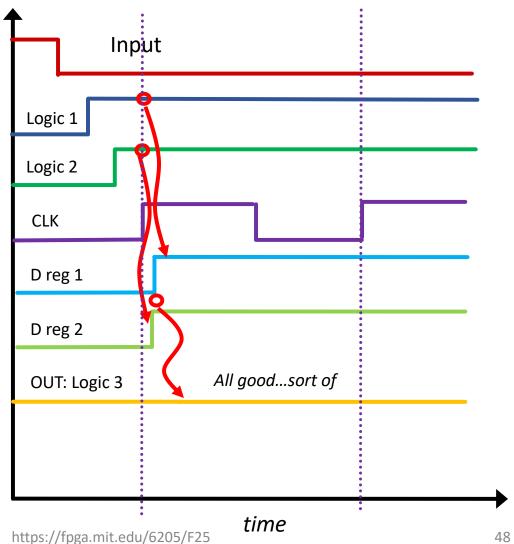

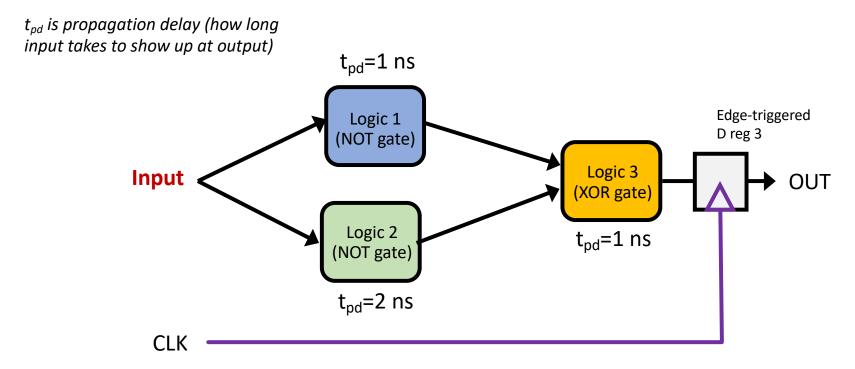

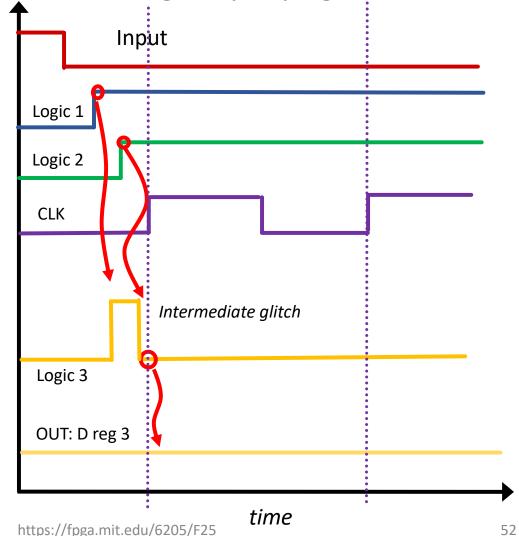

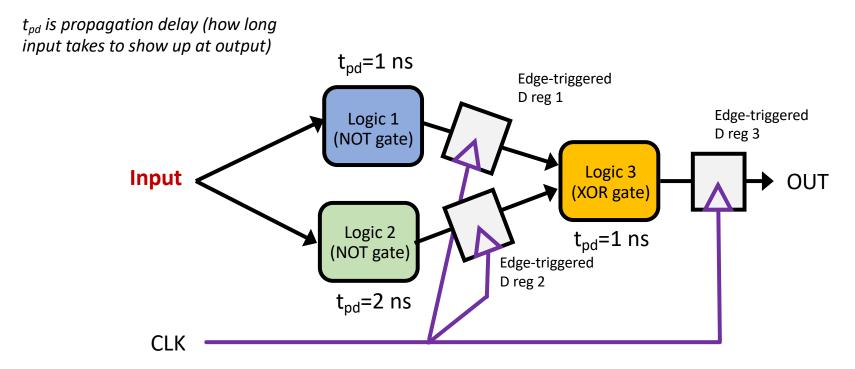

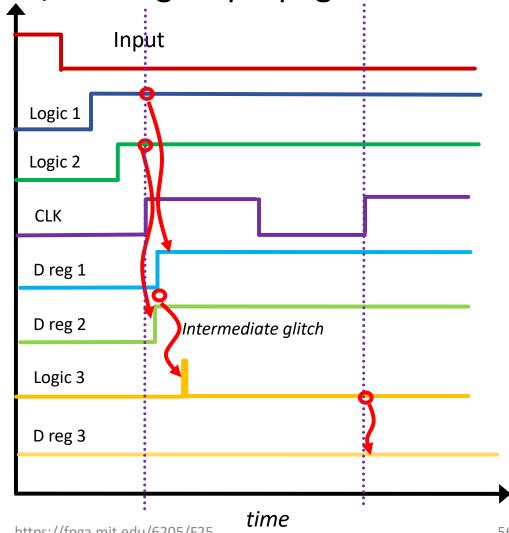

### This is How We Fix This

Registers let us isolate/limit signal propagation and synchronize stages

CLK is a synchronization signal

## Solution 1

Balance output

#### Previous page:

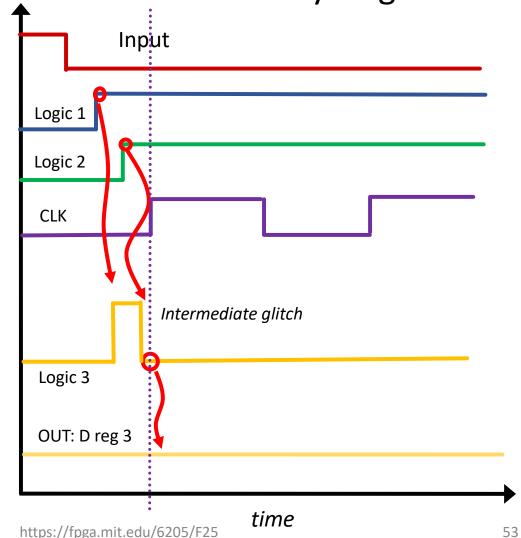

*Intermediate glitches* are minimized and suppressed in output

9/16/25

## Combinational Logic At Output

• There still could be slight differences in register to

**XOR** routing

#### Previous page:

Intermediate glitches are minimized and suppressed in output

9/16/25

https://fpga.mit.edu/6205/F25

SV

#### Previous page:

```

logic inputt, outputt;

logic o1, o2, o3;

logic o1r, o2r;

not_gate_a nga(.val_in(inputt), .val_out(o1));

not_gate_b ngb(.val_in(inputt)), .val_out(o2));

always_ff@(posedge clk_in)begin

o1r <= o1;

o2r <= o2;

end

xor_gate xg (.vala_in(o1r), .valb_in(o2r), val_out(o3));

assign outputt = o3;</pre>

```

### This is How We Fix This

Registers let us isolate/limit signal propagation and synchronize stages

CLK is a synchronization signal

## Remember about Delays in Logic

Registers let us isolate/limit signal propagation and

synchronize stages

#### Previous page:

Intermediate glitches are minimized and suppressed in output

9/16/25

### Intermediate Glitches

Even though that glitch is now internal, the fact that it happens means the XOR is now cycling for

no reason...

#### Previous page:

May not be happy with having large internal logic needlessly flipping bits for no reason

SV

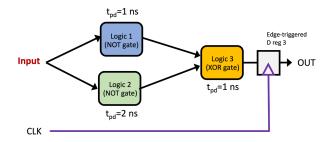

#### Previous page:

```

logic inputt, outputt;

logic o1, o2, o3;

not_gate_a nga(.val_in(inputt), .val_out(o1));

not_gate_b ngb(.val_in(inputt)), .val_out(o2));

xor_gate xg (.vala_in(o1), .valb_in(o2), val_out(o3));

always_ff@(posedge clk_in)begin

outputt <= o3;

end</pre>

```

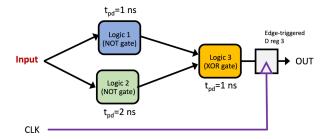

### Add more

Registers let us isolate/limit signal propagation and synchronize stages

CLK is a synchronization signal

## Remember about Delays in Logic

Registers let us isolate/limit signal propagation and

synchronize stages

#### Previous page:

*Intermediate glitches* are minimized and suppressed in output

9/16/25

https://fpga.mit.edu/6205/F25

SV

#### Previous page:

```

logic inputt, outputt;

logic o1, o2, o3;

logic o1r, o2r;

not_gate_a nga(.val_in(inputt), .val_out(o1));

not_gate_b ngb(.val_in(inputt)), .val_out(o2));

always_ff@(posedge clk_in)begin

o1r <= o1;

o2r <= o2;

output <= o3;

end

xor_gate xg (.vala_in(o1r), .valb_in(o2r), val_out(o3));</pre>

```

## Tradeoff for all this "protection"?

• No free lunch!

Use More resources

Have More latency

## Design Complex Logic In Stages!

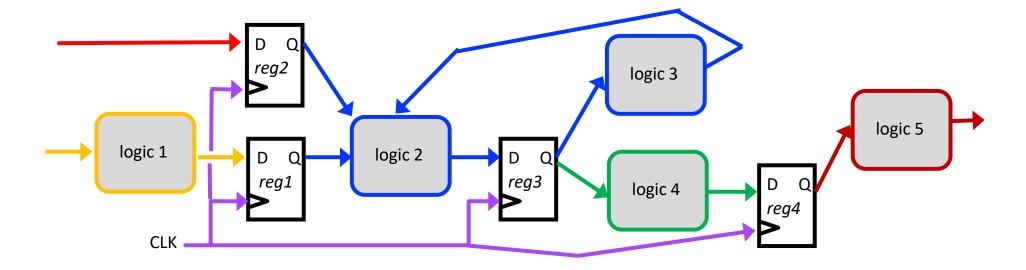

- D flip-flops regulate signal propagation!

- Design complex logic systems in stages

- Worry only about affects of delays (t<sub>pd</sub> and t<sub>cd</sub>) and glitches within a given stage, rather than how they all interplay!

### Is that All there is To It?

• No. No there's not

Let's return to how Latches and Flip Flops actually work

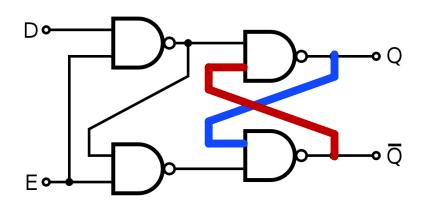

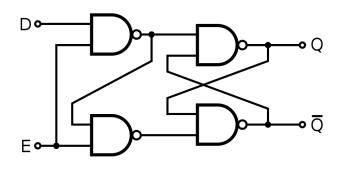

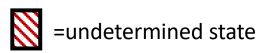

### The D Latch

- Made of gates (which are made of transistors, which are made of sand(currently))

- Something different though...what is it?

"latch" means it holds whatever value was already present...basically: "Previous Q"

| Е | D | Q     | $\overline{\mathbb{Q}}$ |

|---|---|-------|-------------------------|

| 0 | 0 | latch | latch                   |

| 0 | 1 | latch | latch                   |

| 1 | 0 | 0     | 1                       |

| 1 | 1 | 1     | 0                       |

E = "Enable" D = "Data"

Q = not sure, but it is the output 61

## The D Latch Provides Memory!

- 1. Set E=1

- 2. Set your D value

- 3. Set E=0

- 4. Whatever D was is stored at Q forever until E is 1 again!

- 5. Can we do better/different?

| Е | D | Q     | Q     |

|---|---|-------|-------|

| 0 | 0 | latch | latch |

| 0 | 1 | latch | latch |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

E = "Enable" D = "Data"

Q = not sure, but it is the output

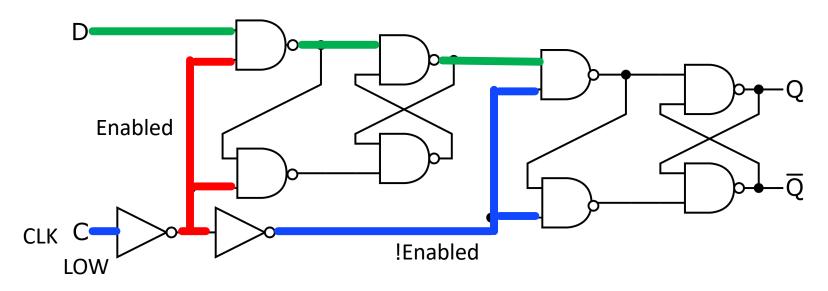

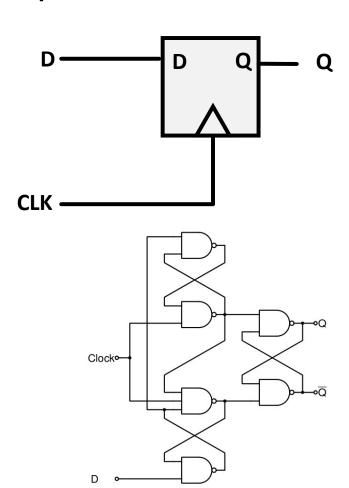

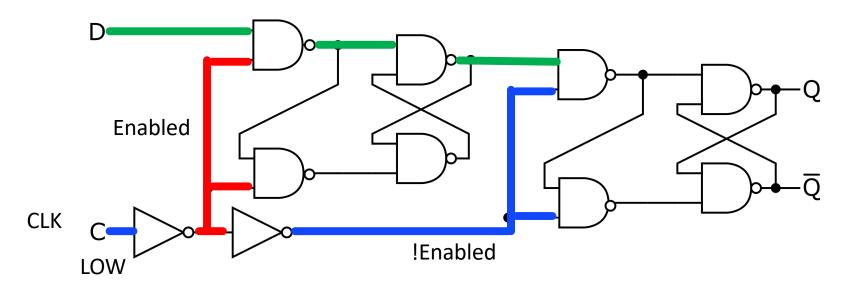

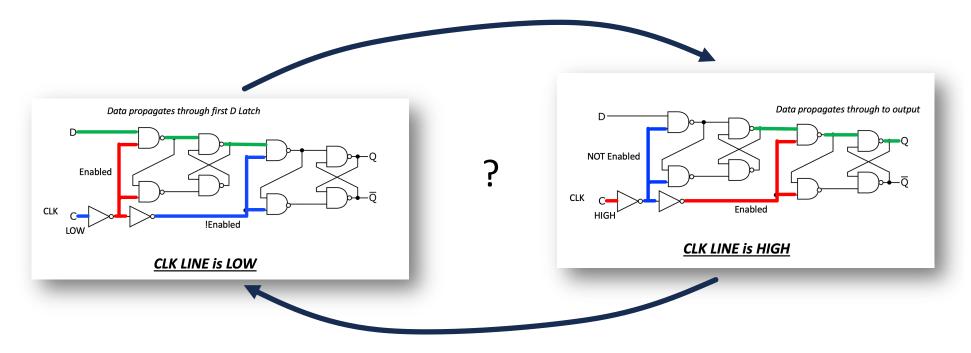

## The D Flip-Flop (Reg)

Two D-Latches in Series driven with opposite enable signals

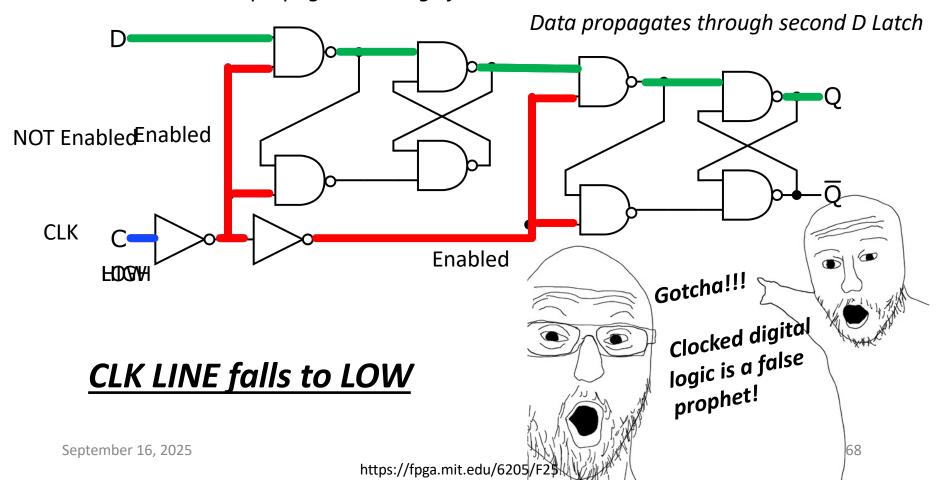

#### Data propagates through first D Latch

### **CLK LINE is LOW**

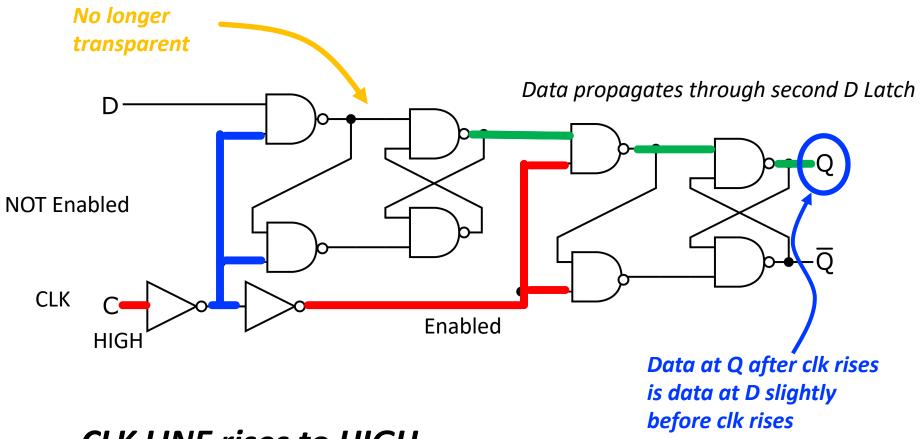

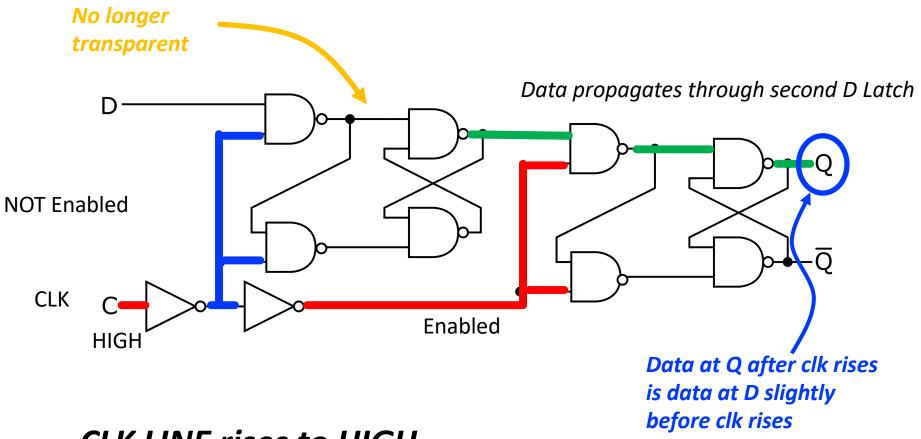

# The D Flip-Flop (Reg)

Two D-Latches in Series driven with opposite enable signals

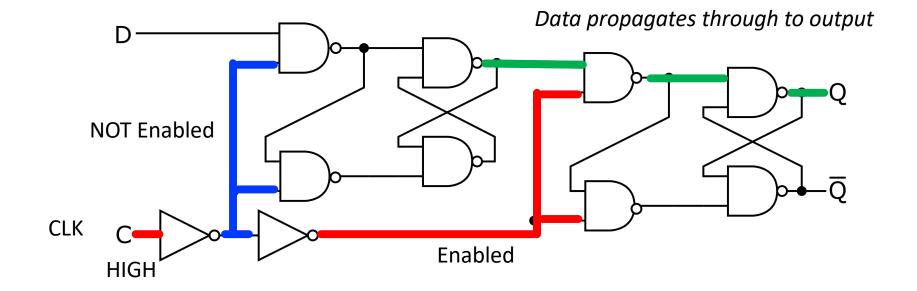

**CLK LINE rises to HIGH**

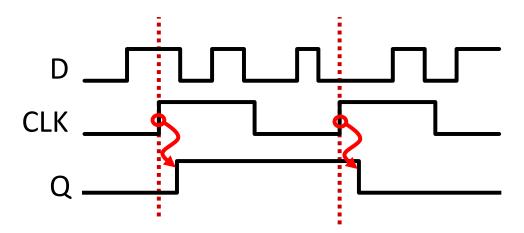

## The Result: the D Flip-Flop

The edge-triggered D register:

on the rising edge of CLK, the

value of D is saved in the

register and then appears

shortly afterward on Q.

Example: 74LS74 internals When you simplify some common/redundant logic between the two stages, you get to about ~25 transistors

## What about...?

What about on the falling edge?

• What about it?

# The D Flip-Flop (Reg)

Two D-Latches in Series driven with opposite enable signals

**CLK LINE rises to HIGH**

## The D Flip-Flop (Reg)

Two D-Latches in Series driven with opposite enable signals

Data propagates through first D Latch

## In Reality

- The cartoon gates are not real. They are models

- Electricity doesn't really flow like magical juice

- The gates don't really act like valves to electricity, but moreso valves to information...and even then they're not valves...they're amplifiers

- Even if there is some momentary transparency, it doesn't really matter since it would be for a very short time (much faster than any outside thing can take advantage of it).

- So you have:

# The D Flip-Flop (Reg)

#### Data propagates through first D Latch

### **CLK LINE is LOW**

# The D Flip-Flop (Reg)

### **CLK LINE is HIGH**

## And it cycles back and forth

- The exact behavior during the transition is a little vague...

- And it does need to be considered

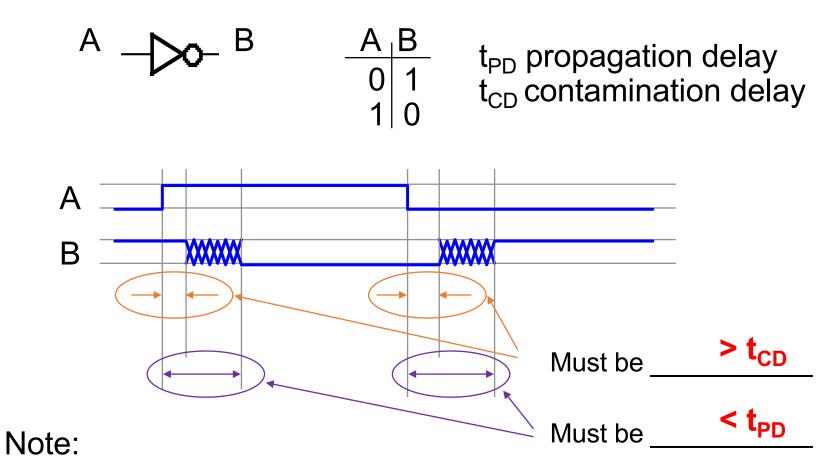

# Things to Keep in Mind: Delay

Flip-flops are circuits at the end of the day...they have contamination and propagation delays

Just like regular combinational circuits!!!

Replace "Stars" with "Flip-flops" and "Us" "Combinational Logic" for joke to operate

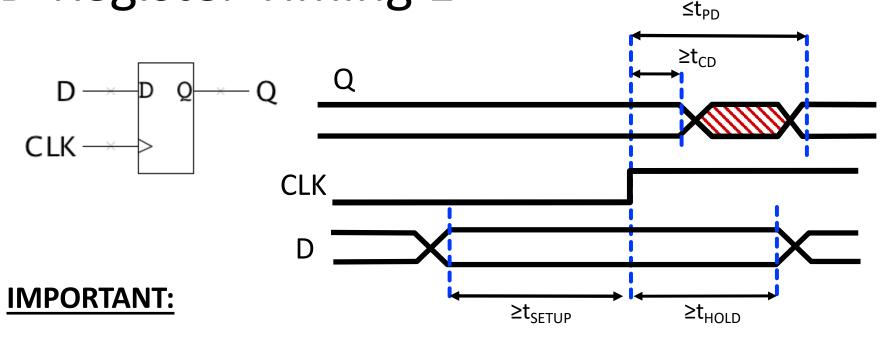

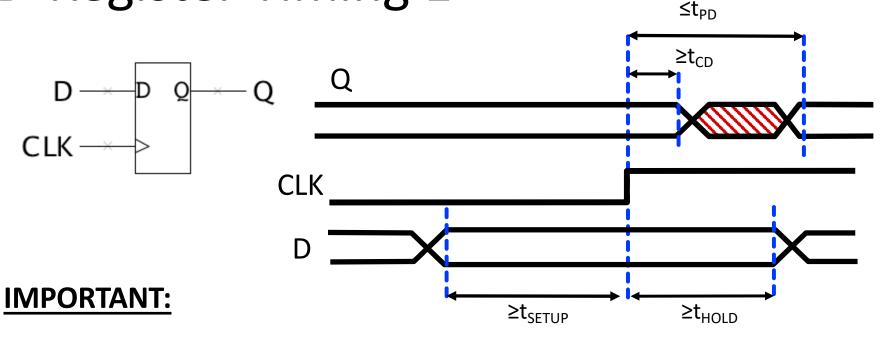

# D-Register Timing 1

$\mathbf{t_{PDr}}$ : maximum propagation delay, @posedge CLK D  $\rightarrow$ Q

Maximum time it takes for Q to change after rising edge of CLK

$\mathbf{t}_{CDr}$ : minimum contamination delay, @posedge CLK D  $\to$ Q

Minimum time it takes for Q to start to change after rising edge of CLK

#### Vulnerability

- During the transition period Flip-flops are vulnerable during so we need to help out by treating the device in certain ways!

- Digital circuits are high-gain amplifiers

- There is also feedback present

- Messing with the flip-flop's inputs during a transition period can be catastrophic\*

- So we must give the flops their space when they are most vulnerable!!!

\*metastability...talked about in future class.

# D-Register Timing 1

$\mathbf{t}_{PDr}$ : maximum propagation delay, @posedge CLK D  $\rightarrow$ Q

Maximum time it takes for Q to change after rising edge of CLK

$\mathbf{t}_{CDr}$ : minimum contamination delay, @posedge CLK D  $\to$ Q

Minimum time it takes for Q to start to change after rising edge of CLK

**t**<sub>SETUP</sub>: setup time

How long D (input) must be stable **before** the rising edge of CLK

$t_{HOLD}$ : hold time

How long D (input) must be stable after the rising edge of CLK

New timing attributes for registers

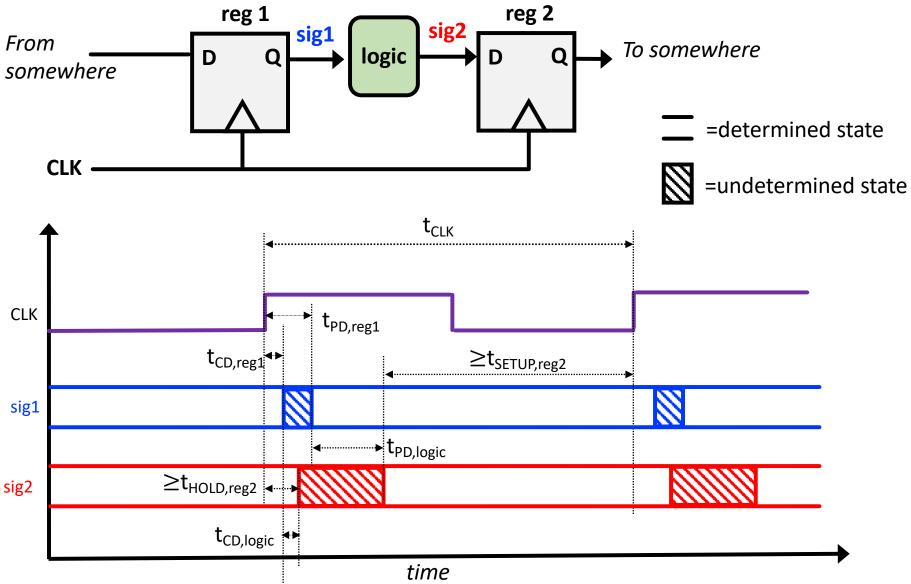

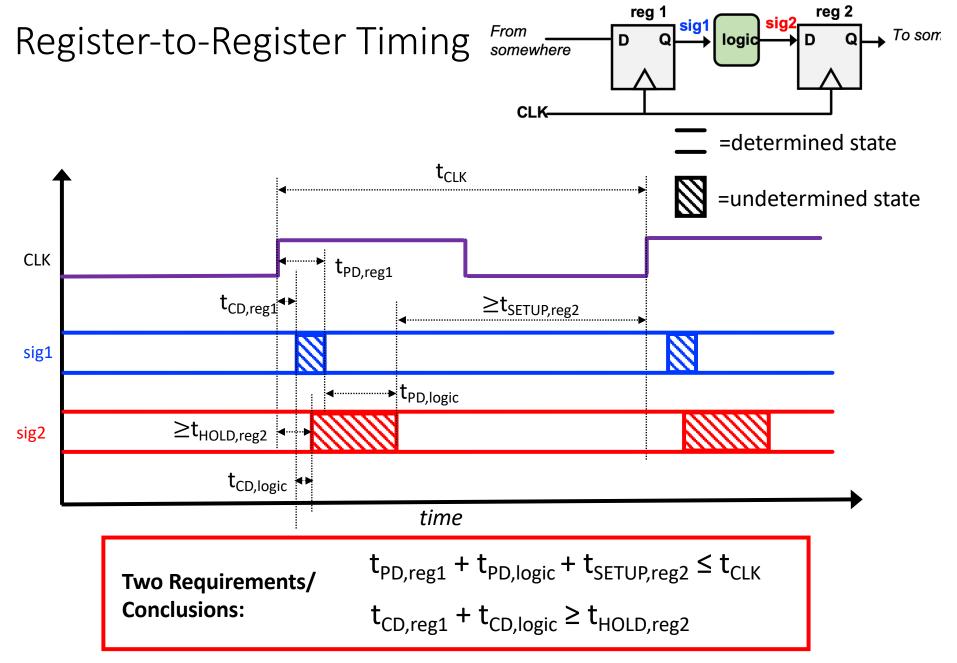

### Register-to-Register Timing

# D Register Timing Conclusions

$t_{\text{PD,reg}}$  ,  $t_{\text{SETUP,reg}}$  ,  $t_{\text{CD,reg}}$  ,  $t_{\text{HOLD,reg}}$  , and  $t^*_{\text{CD,logic}}$  are all roughly fixed/ unchangeable

$$t_{PD,reg1} + t_{PD,logic} + t_{SETUP,reg2} \le t_{CLK}$$

We may/will encounter this in 6.205!

If we try to make our combinational logic **tooooo complex** and we won't satisfying timing. How do we fix?

Two options:

Slow down clock:

$\uparrow t_{CLK}$

Shorten combinational logic:

↓ t<sub>PD,logic</sub>

$$t_{CD,reg1} + t_{CD,logic} \ge t_{HOLD,reg2}$$

6.205 Design Space:

If you violate this, you have to change your design. This is more an issue for the device engineers...on our FPGAs the contamination delays (min change times) are usually longer than HOLD times, so it is hard for <u>us</u> to run into this problem in 6.205 (though it is a very real problem for people laying out circuits)

### Design Complex Logic In Stages!

- Design complex logic systems in stages

- Worry only about effects of delays (t<sub>pd</sub> and t<sub>clk</sub>) within a given stage, rather than how they all interplay!

# Single Clock Synchronous Discipline

- The timing requirements are already complicated enough with one clock. Avoid multiple clocks at all cost!

DO NOT clock flip flops on non-clock lines.

- Single Clock signal shared among all clocked devices (one clock domain)

- Only care about the value of combinational circuits just before rising edge of clock

- Clock period greater than every combinational delay

- Change saved state after noise-inducing logic changes have stopped!

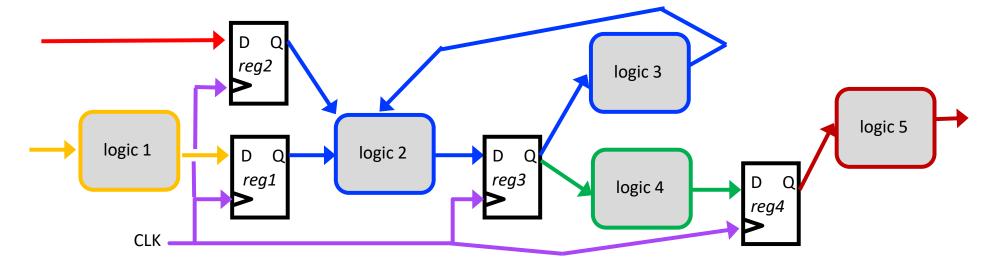

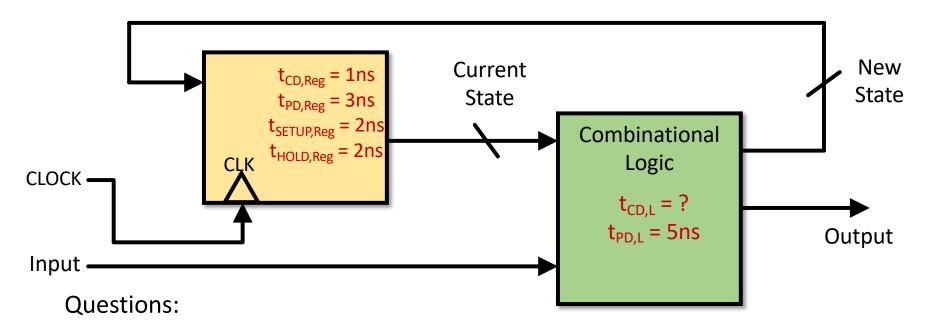

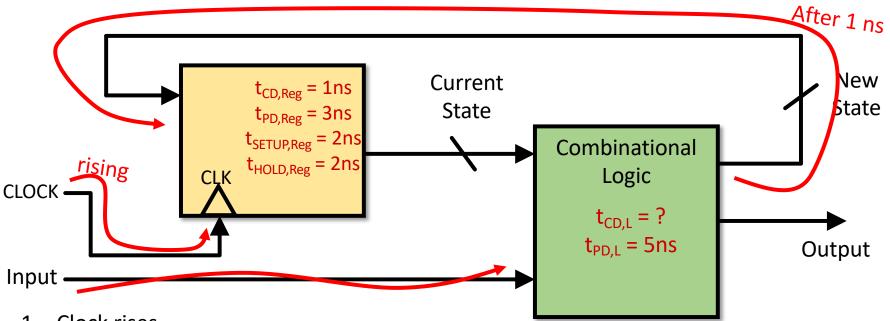

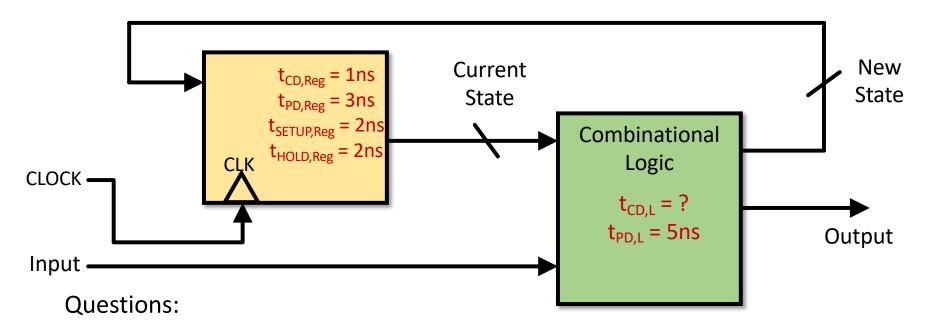

#### Sequential Circuit Timing

Assume input is also coming from a clocked system

- Minimum clock period?

- Constraints on t<sub>CD,L</sub>?

- Setup, Hold times for entire system? (Aka for the system input?)

This is a simple Finite State Machine (next lecture)

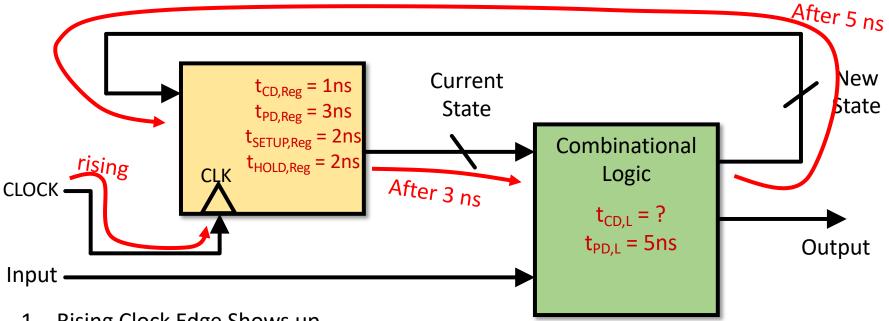

#### Minimum Clock Period?

Assume input is also coming from a clocked system

- Rising Clock Edge Shows up...

- 2. It is  $t_{PD,Reg} = 3$ ns until flop has finalized changing

- 3. It is then additional  $t_{PD,L}$  = 5ns until logic has finalized changing and starts sending data back to flop

- 4. That change must be done at least  $t_{SETUP,Reg} = 2ns$  before the next rising clock edge

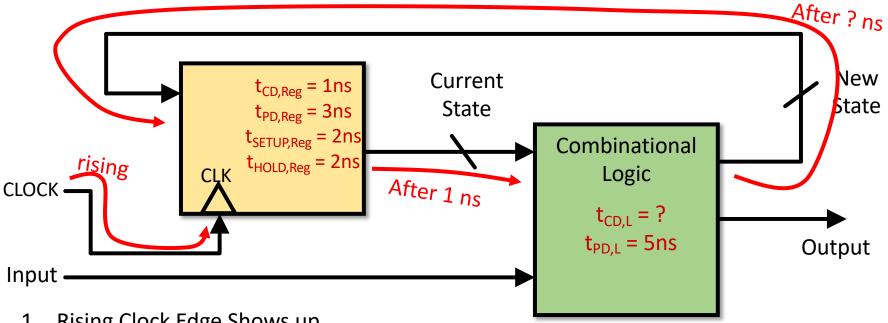

# t<sub>CD,L</sub> Constraints?

Assume input is also coming from a clocked system

- Rising Clock Edge Shows up...

- It is  $t_{CD,Reg} = 1$ ns until flop output starts changing

- It is then additional  $t_{CD,L}$  = ? Until feedback wire starts changing

- That change cannot be happening until at least  $t_{HOLD,Reg} = 2$ ns has passed from clock edge

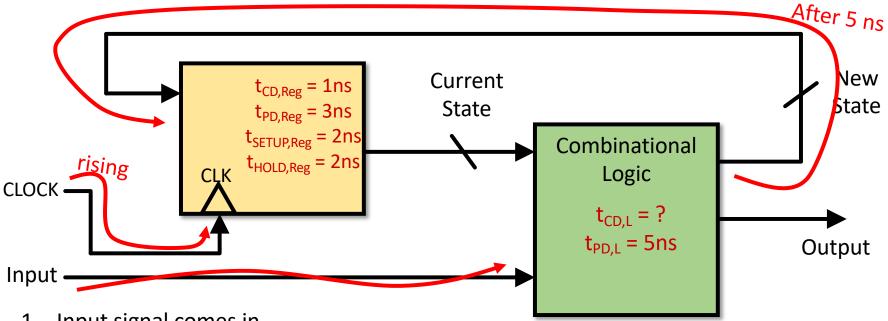

# Setup Time for Inputs of Whole System?

- 1. Input signal comes in

- 2. It is  $t_{PD,L}$  = 5ns until comb logic has processed it and it is fed back...

- 3. That change must be done at least  $t_{SETUP,Reg}$  = 2ns before the next rising clock edge

#### Hold Time for System Input?

- Clock rises

- Input signal comes in

- It is additional  $t_{CD,L}$  = 1ns until comb logic starts to feed back...

- That change must be done at least  $t_{HOLD,Reg} = 2ns$  after the prior rising clock edge

#### Sequential Circuit Timing

Assume input is also coming from a clocked system

- Minimum clock period?

- Constraints on t<sub>CD,L</sub>?

- Setup, Hold times for Inputs?

This is a simple Finite State Machine ... which we will cover formally on Thursday