6.205 (aka 6.111)

Introduction

Fall 2025

#### Course Overview

- Prerequisites: 6.191/6.004 (if no && not coreq-ing, email me please)

- **Units:** 1-5-6

- Lectures: Tuesday, Thursday 2:30-4:00 pm in 45-230

- **Labs:** No official time. The lab room is the left (southern) portion of building 38's 6th floor.(38-630) There are 17 dedicated computers for working on labs and assignments there, however, we also strongly encourage you to install the appropriate toolchains on your own machine when possible.

- Lab Kit: You will be provided a Real Digital Urbana FPGA board for this class which you must take care of and return. This will be used in all labs and will likely form the center of your final project. You must return this

- Piazza: https://piazza.com/mit/fall2025/6205

- Textbook: The internet

- TAs:

- Monica Chan (mochan)

- Yoland Gao (youran)

- Hasan Zeki Yildiz (hzyildiz)

- Kiran Vuksanaj (kiranv)

- Instructor:

- Joe Steinmeyer (jodalyst)

Mostly Correct Course of Course site including

#### Grades

- Your overall grade is based on the following breakdown:

- Assignments: 48%

- 7 weeks of exercises and labs before project time

- Final Project: 52%

- Last ~7/8 weeks of semester

- A large number of students do "A" level work and are, indeed, rewarded with a grade of "A". The corollary to this is that, since average performance levels are so high, punting any part of the subject can lead to a disappointing grade.

- Final Project: Details in coming weeks

## CI-M Possibility Reality

- We are a CI-M

- We do a lot of writing and presenting with our final project. You should be prepared for that.

- Please see syllabus on the course site for details of what is expected.

#### Lab Kit

- Using a Urbana Board by RealDigital\*

- Additional parts for some labs (pick up as needed)

- Must return at end of semester

\*newer company

# Collaboration and Academic Integrity

- Assignments must be done independently but students may seek help from other students and of course staff.

- That does not mean copying people's stuff.

- Work submitted must be your own

- You should not be using generative AI to do your assignments. If it is caught, it will be referred to COD and there will be grade impacts.

- Violations/copying work will be dealt with seriously.

Don't put us in that position. Nobody (us or you will be happy)

## Grade/Lateness Mechanics

- Assignments are come out on Thursdays after class and are due the following Wednesday night.

- Every day late, they lose 20% (doesn't accrue on Sat/Sun)

#### Office Hours

- Office Hours calendar on the main website page, will be updated weekly by staff

- Office hours in south-side of 38-630, the 6.205 lab

- In person:

- The help queue is for in-person work only

- Lab machines in 38-630 will be open for your use if needed, though everything can be done on laptops.

- These machines may not be up with accounts until the weekend.

- Checkoffs must be done in person, not remotely.

- Post on Piazza for remote help (gets quick responses generally)

## Pause...

• Questions...?

#### 6.205's Goal

- We focus on digital design in this class and apply it to FPGAs

- We will want to do lots of simulations, but the end goal is always to have working implementations on hardware!

- The best bugs and thinkos show up when actually trying to get a system working in real life.

#### WTFPGA?

- A giant Array of very primitive logic blocks (aka "Gates", memory, and other specialized hardware that are each individually Programmable.

- The giant array of logic exists in a huge sea of Programmable interconnects

- The device can be reprogrammed repeatedly even once in a device, hence it can be programmed "in the Field".

- You have full control over all the modules and their interconnects. They can run at the same time; not bound by the fixed structure and limitations of a computer

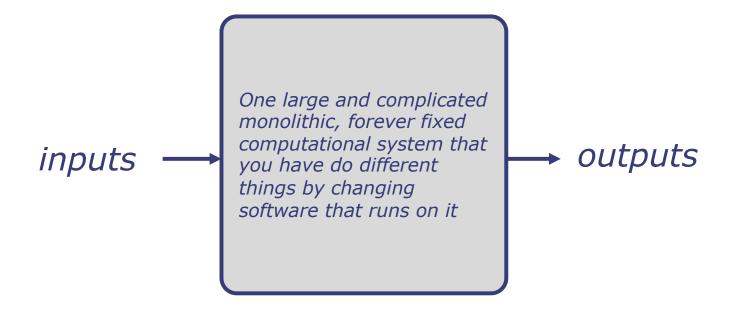

## A Regular Computer

- Write Code

- You Program a piece of hardware with that code

- That hardware runs the code

#### An FPGA

- Many small programmable blocks

- Write code for each and program them

Write "code" that specifies how they work together

and program them

Run it all

inputs

Many small, relatively simple computational elements you individually program and individually connect together as you see fit!

## Our cheapo\* FPGA in 6.205

- Has roughly 33,000 programmable blocks

- 150 18kb memory units

- 5 clock management tiles

- 120 dedicated multipliers

- Vast array of input, output devices

- ...and all of these can be interconnected as we see fit to build complex systems.

<sup>\*</sup>even cheap FPGAs have resources orders of magnitude more than computation systems from previous decades

#### Where are FPGAs used?

- Anywhere that speed/latency and efficiency are important:

- Hardware accelerators

- Stream processors

- Communications systems

- Where the "generalness" of a computer isn't needed or is harmful:

- Improvements in:

- Speed

- Cost

- Power consumption

- When lots of simpler tasks to be done in parallel

- In prototyping: After you've simulated a new design but before you spend tens of millions and wait eighteen months to make a chip you will prototype it on an FPGA

## Where are FPGAs **NOT** used?

- Not used in a lot of ML applications (exceptions where very-low latency inference is needed). GPUs largely dominate that space because of economies and software infrastructure (e.g. CUDA)

- Exception is they are used to support a lot of ML/AI stuff (moving data, etc...)

- Anywhere where a dedicated processor is advantageous...like in a general computer

- Where economies of scale allow dedicated chips to be financially viable

#### The State of Hardware

- Since Moore's Law has died out, we can't just wait for continual gains from shrinking the same old designs.

- There has been renewed push to:

- Find new computational architectures

- Build new custom chips in areas neglected

- Have much more of a hybrid computational environment

- Hardware and digital design is in a very exciting position right now

- FPGAs can be a good entry point into the field.

## Digital Logic

- Subfield of electronics

- Voltages in the circuit are classified as either "1" or "0"

- each "family" of digital logic has its own specifications as to what constitutes a 1 or a 0

- Digital circuits are designed to:

- interpret input information as 1's and 0's

- generate output information as 1's and 0's

- Digital electronics are the reason for the "digital" revolution:

- Robust, scalable, inexpensive, etc...

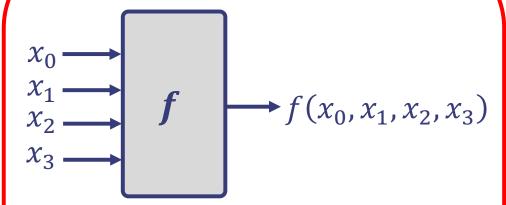

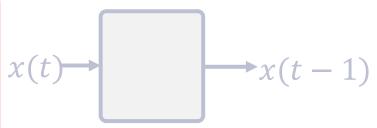

## Two Broad Types of Digital Logic

#### **Functions:**

#### **Stateless**

Current Output is based ONLY on current Inputs

<a href="Mailto:NOT">NOT</a> a function of time

#### **Storage:**

#### **Stateful**

Current Output is based past Input

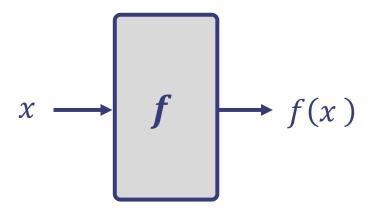

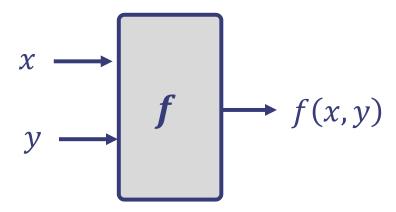

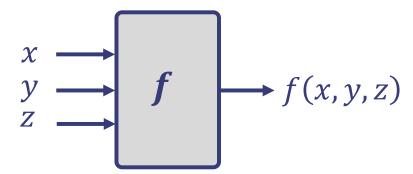

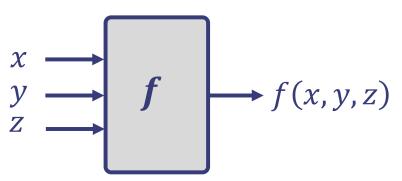

## Digital Functions

- These work just like  $f(x_0, x_1, x_2, x_3)$  from "regular" math, however...

- - as opposed to Real Numbers R

- Or complex Numbers ©

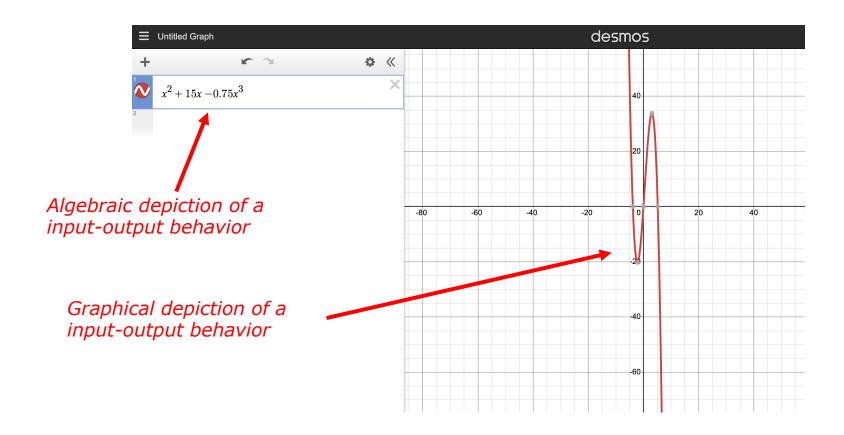

- How do we "display" a function that exists in R?

- For example, if I wanted to show you some f(x) in  $\mathbb{R}$ ? How would we do it?

# We Plot it or Write it Out with a set of math algebra

## Digital Functions

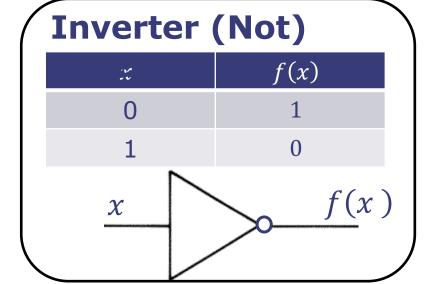

- Digital Functions can also be written using algebraic expressions, just ones limited to the Boolean realm.

- Digital functions can also be graphically depicted, just usually not with graphs...instead we'll use tables.

## Boolean algebra

- variables can only be 0 or 1\*

- Commonly used operations aren't the same as in the real domain:

- $\bar{x}$  means "Not x'' or the opposite

- | means logical "or" (sometimes written as +)

- & or adjacency means "and" (sometimes written as ·)

- So the algebraic expression of a certain digital function could be:

$$f(x, y, z) = \bar{x}\bar{y}\bar{z} |\bar{x}\bar{y}z| x\bar{y}\bar{z} |x\bar{y}z| xyz$$

\*exceptions that we'll learn about

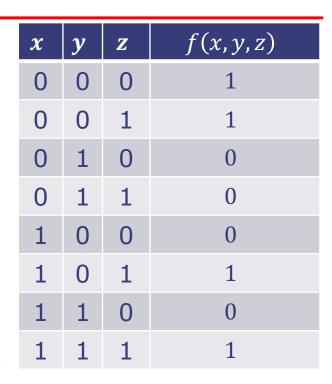

## **Digital Functions**

The "space" of the inputs is often relatively small compared to other domains and is therefore <u>not</u> <u>best</u> conveyed using plots

Instead you will often write these using "Truth

Tables"

Express your function algebraically like this:

$$f(x, y, z) = \bar{x}\bar{y}\bar{z} |\bar{x}\bar{y}z| x\bar{y}\bar{z} |x\bar{y}z| xyz$$

Or "graphically" like this:

| x | y | Z | f(x, y, z) |

|---|---|---|------------|

| 0 | 0 | 0 | 1          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | 0 | 0          |

| 0 | 1 | 1 | 0          |

| 1 | 0 | 0 | 0          |

| 1 | 0 | 1 | 1          |

| 1 | 1 | 0 | 0          |

| 1 | 1 | 1 | 1          |

## **Digital Functions**

- As we'll see, for a low-count variable inputs, there are infinite possible functions in the Real domain

R but only a handful of possible in the Boolean domain

- For small input functions, the possibilities are so few we give them names even in the digital space.

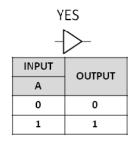

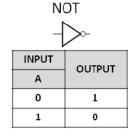

## The Simplest Digital Function Class

One Bit Input:

How many possible 1-bit functions exist?

### 1-bit functions (input is a single value):

- How many possible 1-bit functions exist?

- Two (actually 4)...

# Buffer (Yes) gate: x f(x) 0 0 1 x f(x)

| Always ( | On gate: |

|----------|----------|

| x        | f(x)     |

| 0        | 1        |

| 1        | 1        |

|          |          |

| • | Always Off gate: |      |  |

|---|------------------|------|--|

|   | $\boldsymbol{x}$ | f(x) |  |

|   | 0                | 0    |  |

|   | 1                | 0    |  |

|   |                  |      |  |

September 4, 2025

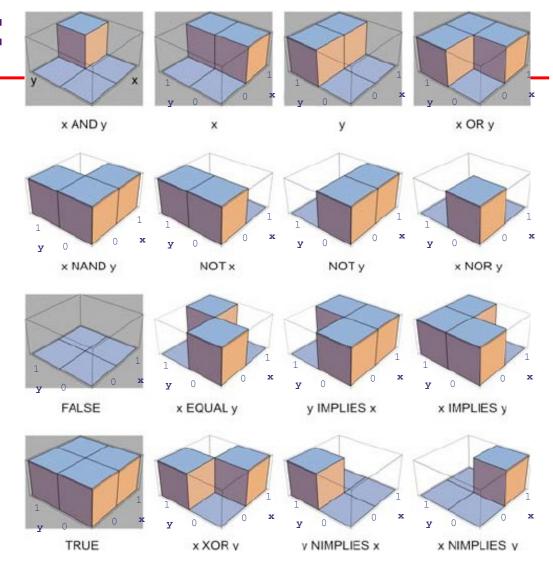

## What About Two bits input?

Two Bit Input:

How many possible 2-bit functions exist?

#### 2-bit functions:

| f(x,y) |   |        |  |  |

|--------|---|--------|--|--|

| x      | y | f(x,y) |  |  |

| 0      | 0 | f(0,0) |  |  |

| 0      | 1 | f(0,1) |  |  |

| 1      | 0 | f(1,0) |  |  |

| 1      | 1 | f(1,1) |  |  |

$2^4 = 16$  possible functions exist

Stated another way: there are 16 unique 1-0 combinations for: f(0,0), f(0,1), f(1,0), and f(1,1)

Mayo, Avi & Setty, Yaki & Shavit, Seagull & Zaslaver, Alon & Alon, Uri. (2006).

Plasticity of the cis-Regulatory Input Function of a Gene. PLoS biology. 4. e45. 10.1371/journal.pbio.0040045.

September 4, 2025

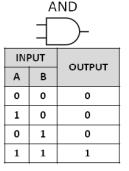

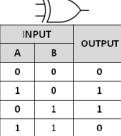

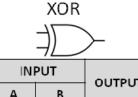

## Simple Truth Tables

- For a single-input system, there are four possible mappings (two nonnegligible)

- For a two input system, you have 4 input combinations and 16 possible truth tables

- There is a lot of complexity that these give us

| 1   |     |        |  |  |

|-----|-----|--------|--|--|

| INI | PUT | OUTPUT |  |  |

| Α   | В   | OUIFUI |  |  |

| 0   | 0   | 0      |  |  |

| 1   | 0   | 1      |  |  |

| 0   | 1   | 1      |  |  |

| 1   | 1   | 1      |  |  |

| $\exists L$ |   |        |  |  |

|-------------|---|--------|--|--|

| INPUT       |   | OUTPUT |  |  |

| Α           | В | 001701 |  |  |

| 0           | 0 | 0      |  |  |

| 1           | 0 | 1      |  |  |

| 0           | 1 | 1      |  |  |

| 1           | 1 | 0      |  |  |

XOR

| INPUT |   | OUTPUT |  |

|-------|---|--------|--|

| Α     | В | OUIPUI |  |

| 0     | 0 | 1      |  |

| 1     | 0 | 1      |  |

| 0     | 1 | 1      |  |

| 1     | 1 | 0      |  |

|       |   |        |  |

| NOR      |

|----------|

| <b>→</b> |

|          |

| INPUT |   | OUTPUT  |

|-------|---|---------|

| Α     | В | 0011101 |

| 0     | 0 | 1       |

| 1     | 0 | 0       |

| 0     | 1 | 0       |

| 1     | 1 | 0       |

| XNC | )R            |

|-----|---------------|

|     | <b>&gt;</b> - |

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OOIFOI |

| 0     | 0 | 1      |

| 1     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 1 | 1      |

Abels and Khisamutdinov, 2015, https://www.researchgate.net/publication/291418819 Nucleic Acid Computing and its Potential to Transform Silicon-Based Technology

## Logical Reduction

- All high level operations we may want can be reduced down to combinations of these simpler logical operations

- We just need to start to see how.

- Don't just think of the "AND" gate as "AND" in the quasi-grammar sense of the term. A lot of things we'd want to do when writing high-level logic/programs rely on it, even if we don't name it that explicitly.

- Same with "OR" or "XOR"

## Consider just one of these truth tables "XOR"

- If 0 and 1 are numbers, XOR performs base 2 addition:

- **■** 0+0=0

- **■** 0+1=1

- **■** 1+0=1

- 1+1=0 (carry 1)

- Or, if 0 means positive and 1 means negative, XOR performs sign determination of multiplication:

- $0 \times 0 = 0$  (positive×positive = positive)

- $0 \times 1 = 1$  (positive×negative = negative)

- $1 \times 0 = 1$  (negative×positive = negative)

- $1 \times 1 = 0$  (negative×negative = positive)

## Still thinking about ways of using XOR

XOR expresses the if/else check:

```

if(A==1):

output = !B

else:

output = B

```

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | 001701 |

| 0     | 0 | 0      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 1 | 0      |

- XOR it does the check: A!=B

- XOR does many others

- All high-level algorithmic needs find their basic implementation in these fundamental functions of AND, XOR, NAND, etc...

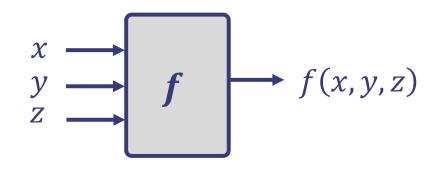

#### 3-bit functions:

$$f(x, y, z)$$

$2^8 = 256$  possible

patterns for  $f$

Space of a function is based off its input width:

$$2^{2^n} = 2^{2^3} = 2^8 = 256$$

| x | y | Z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | f(0,0,0) |

| 0 | 0 | 1 | f(0,0,1) |

| 0 | 1 | 0 | f(0,1,0) |

| 0 | 1 | 1 | f(0,1,1) |

| 1 | 0 | 0 | f(1,0,0) |

| 1 | 0 | 1 | f(1,0,1) |

| 1 | 1 | 0 | f(1,1,0) |

| 1 | 1 | 1 | f(1,1,1) |

## More Complex Logic Functions

- 3 input Truth table:

- A,B,C can be a three bit number:

| Α | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

A,B two-bit number, C some condition:

Etc...

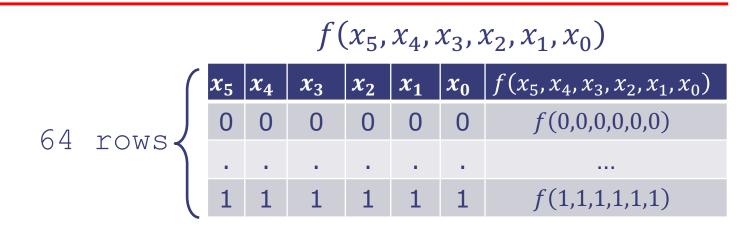

## Things Scale Quickly

As you add more and more bits to your function's input, the number of possible functions you can express grows astronomically...

Number of n bit functions that exist:  $2^{2^n}$

#### **6-bit functions:** $f(x_5, x_4, x_3, x_2, x_1, x_0)$

# Possible functions you can express with six bit input is:

$$2^{2^6} = 2^{64} = 1.84 \times 10^{19}$$

Our FPGA has 33,000 individually programmable 6-input logic functions, meaning we have astronomically large possibilities to build.

#### Now...This...is Sort of Backwards

- A modern digital engineer usually doesn't start with a set of truth tables and then assign meaning to them. (what we just did)...like having a hammer looking for nails.

- We usually want to go in the <u>other direction</u>:

- Describe some sort of logical behavior that we want (if this, then that, etc...)

- Figure out the most efficient underlying digital function that will express all of that for us and use it!

- We don't want to justify logic that we already have

- We want to synthesize logic to suit a purpose,

## Creating Truth Tables Manually

- If you can boil your function down to a truth table, it can be used to "program" the small logic functions in an FPGA!

- For simple things this isn't too hard

#### Sum of Products

One way to specify a Boolean function can be in an algebraic expression

$$f(x, y, z) = \bar{x}\bar{y}\bar{z} |\bar{x}\bar{y}z| x\bar{y}\bar{z} |x\bar{y}z| xyz$$

- Function is High when:

- x is low and y is low and z is low OR

- x is low and y is low and z is high OR

- etc...

- Called a "Sum of Products"

Called that because OR is sometimes drawn as + in Boolean algebra, and & is often drawn as multiply

Also sometimes Normal Form, Junctive the

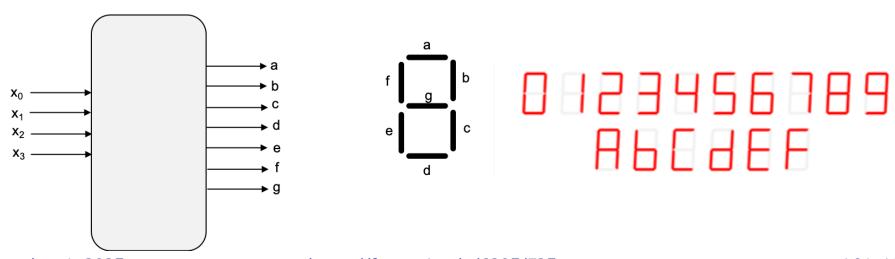

#### One of Week 01's Assignments

- In Week 01 you'll design a 7-segment decoder:

- Four bit digital value in encoding numbers 0 to 15 in binary

- Seven values out which drive 7-segment LED to

- Approach like seven separate sum of products.

- Specify the sum-of-product for the "a" segment...then the "b" segment, etc...

September 4, 2025

https://fpga.mit.edu/6205/F25

#### Sum of Products Does Not Scale

- Sometimes, sum of products are the easiest way to just express a digital behavior.

- But other times...we want to be able to say:

- "If x is < 258 make an output go high, but only if button B is not pushed and also do this other thing, but only if Buttons C1 through C18 are in a 0x2AAAA pattern..."</p>

- You can reduce this logic down to algebraic expressions and truth tables, but it takes work

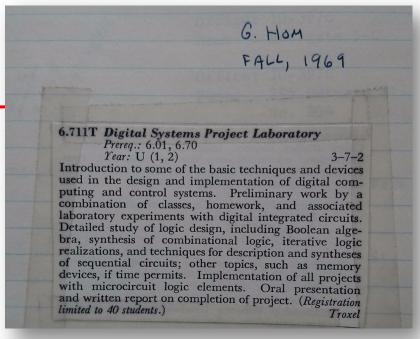

# Historically...

That work of doing all the algebra and optimizing your circuit is what you would do in digital design including in this class.

•  $6.711 \rightarrow 6.111 \rightarrow 6.205$

#### Sum of Products Does Not Scale

- Sometimes, sum of products are the easiest way to just express a digital behavior.

- But other times...we want to be able to say:

- "If x is < 258 make an output go high, but only if button B is not pushed and also do this other thing, but only if Buttons C1 through C18 are in a 0x2AAAA pattern..."</p>

- You can reduce this logic down to algebraic expressions and truth tables, but it takes work

- Now we use higher level constructs and this is really where Hardware Description Languages come in.

# SystemVerilog

A Hardware Description Language interprets high-level algorithmic expressions into low-level digital logic

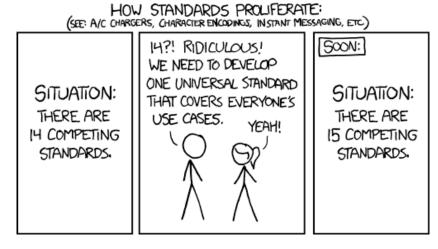

#### Verilog...VHDL...Chisel...SystemVerilog... SystemC...Bluespec...Minispec...Verik...Veryl... UVM...Amaranth...Lucid....forever and ever amen.

- We use Verilog and SystemVerilog since it really is an industry standard.

- Yeah... Verilog sucks in lots of ways, but I think it is a really good language to know and have some fluency in

- Lots of alternatives, but I'll leave that to you to discover in other situations/classes

#### Verilog: A Hardware Description Language (HDL)

- Verilog is can/be two things:

- A language used to describe hardware (synthesizable)

- A language used for simulation of hardware (simulatable)

- The bulk of your work in 6.205 will be be in designing Verilog to synthesize onto a device

- We'll then use Python for simulating this year (using a library called cocotb) so we won't use Verilog to simulate much.

# Variables in Verilog

- In Verilog:

- logic is one type of variable

- How a logic gets used determines what it represents

```

//variables:

logic a; //create one

logic b; //create another

logic c,d,e; //create several at same time

```

#### Variables in Verilog

- In Verilog we have flexibility to specify the size of variables:

- By default things are one bit, but you can specify sizes like shown below (sizing specified left to right):

```

//variables:

logic a; //create one bit variable

logic [3:0] b; //create four bit variable

logic [11:0] c,d,e; //create several 12 bit variables

```

- Why not just use standard types (32 bit int for example)?

- You can, but unless needed, why waste the resources?

- If you need four bits, just use four bits

## Values in Verilog

- Good practice to always specify values in the following form: S'Txxxx\_xxxx where

- S is the size of the number (in bits)

- ' is the single quote marker

- T is the numerical base you're specifying the value in

- b for binary (0,1)

- d for decimal (0,1,2,3,4,5,6,7,8,9)

- h for hex (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F)

- xxxx\_xxxx are your values

- The \_ is ignored in evaluation

- use \_ to make more readable

- Don't need to use \_ but is really nice

## Values in Verilog

#### Some examples:

#### Values of Bits

- Each bit can take on four values:

- 1: Logical 1

- 0: Logical 0

- X: Undefined

- Z: High Impedance

# Order of Operations in Verilog

- Be careful!

- The order is not always what you expect!

- Use parentheses for safety!

| Verilog Operator | Name                      | Functional Group |

|------------------|---------------------------|------------------|

| []               | bit-select or part-select |                  |

| ()               | parenthesis               |                  |

| !                | logical negation          | logical          |

| ~                | negation                  | bit-wise         |

| &                | reduction AND             | reduction        |

| I                | reduction OR              | reduction        |

| ~&               | reduction NAND            | reduction        |

| ~l               | reduction NOR             | reduction        |

| ^                | reduction XOR             | reduction        |

| ~^ or ^~         | reduction XNOR            | reduction        |

| +                | unary (sign) plus         | arithmetic       |

| -                | unary (sign) minus        | arithmetic       |

| {}               | concatenation             | concatenation    |

| {{ }}            | replication               | replication      |

| *                | multiply                  | arithmetic       |

| /                | divide                    | arithmetic       |

| %                | modulus                   | arithmetic       |

| +                | binary plus               | arithmetic       |

| -                | binary minus              | arithmetic       |

| <<               | shift left                | shift            |

| >>               | shift right               | shift            |

| >                | greater than              | relational       |

| >=               | greater than or equal to  |                  |

| <                | less than                 | relational       |

| <=               | less than or equal to     | relational       |

| ==               | logical equality          | equality         |

| !=               | logical inequality        | equality         |

| ===              | case equality             | equality         |

| !==              | case inequality           | equality         |

| &                | bit-wise AND              | bit-wise         |

| ۸                | bit-wise XOR              | bit-wise         |

| ^~ or ~^         | bit-wise XNOR             | bit-wise         |

| I                | bit-wise OR               | bit-wise         |

| &&               | logical AND               | logical          |

| II               | logical OR                | logical          |

| ?:               | conditional               | conditional      |

https://class.ece.uw.edu/cadta/verilog/operators.html

# Creating Pure Digital Functions

- Two ways:

- Using assign statements

- Using always\_comb blocks

Let's say I wanted c = b | | a aka "c = b OR a"

```

//create combinational...

//element with assign:

logic a, b, c;

assign c = a || b;

```

```

//create combinational element...

// with always_comb block:

logic a, b, c;

always_comb begin

c = a || b;

end

```

Will result in a piece of combinational logic that carries out this Boolean function:

| INPUT |   | OUTPUT |  |

|-------|---|--------|--|

| Α     | В | 001701 |  |

| 0     | 0 | 0      |  |

| 1     | 0 | 1      |  |

| 0     | 1 | 1      |  |

| 1     | 1 | 1      |  |

# What about "Higher Level" Constructs?

• If/Else Statements?

- For Example:

- Have three one-bit inputs (x,y,z) and a one-bit output.

- If any two or more inputs are 1, the output is 1

- (aka a "majority function")

```

logic x,y,z,output_1;

//one way ("Sum of products"):

assign output_1 = (!x && y && z)|| (x && !y && z) || (x && y && !z) || (x & y && z);

```

And Verilog is like C in terms of formatting...use indents to improve readability!!!

```

logic x,y,z,output_1;

//another way (alternative sum of products approach):

//('b is base header for binary, so 'b011 means 011 in binary)

assign output_1 = (\{x,y,z\}=='b011)||

(\{x,y,z\}=='b101)||

(\{x,y,z\}=='b110)||

(\{x,y,z\}=='b111);

```

So readable!

```

logic x,y,z,output_1;

//another way (chained ternary operator)

assign output_1 = {x,y,z}>=5?1:{x,y,z}==3?:1:0;

//numbers not specified with base header default to base 10!

```

OK...I mean this is maybe a bit better...

This is code where comments would help everyone involved

```

logic x,y,z,output_1;

// same logic as previous ternary chain

// done with always_comb block

always_comb begin

if ({x,y,z}>=5))begin

output_1 = 1'b1;//specify bit

end else if ({x,y,z}==3'b101) begin

output_1 = 1'b1;

end else begin

output_1=0;

end

end

```

```

logic x,y,z,output_1;

//ternary chain previous except done with always_comb block (different)

// this way default sets output_1 to 0 and changes to only on certain conditions

always_comb begin

output_1=0;

if ({x,y,z}>=5))begin

output_1 = 1'b1;//specify bit

end else if ({x,y,z}==3'b101) begin

output_1 = 1'b1;

end

end

// Be very careful with this right now...the way this works can easily lead to confusion

// about things and how to understand System/Verilog

```

# Majority Function Solution(s) all together for review

```

logic x,y,z,output 1;

//one way ("Sum of products"):

assign output_1 = (!x \&\& y \&\& z)|| (x \&\& !y \&\& z)|| (x \&\& y \&\& !z)|| (x \& y \&\& z);

//another way: ('b is base header for binary, so 'b011 means 011 in binary)

assign output 1 = (\{x,y,z\} == b011) | (\{x,y,z\} == b101) | (\{x,y,z\} == b110) | (\{x,y,z\} == b111);

//another way (chained ternary operator)

assign output 1 = \{x,y,z\} > =5?1:\{x,y,z\} = =3?:1:0;

//numbers not specified with base header default to base 10!

//ternary chain above except done with alway comb block

always comb begin

if (\{x,y,z\}>=5)) begin

output 1 = 1'b1://specifv bit

end else if (\{x,y,z\}==3'b101) begin

output 1 = 1'b1;

end else begin

output 1=0;

end

end

//ternary chain above except done with always comb block (different)

always comb begin

output 1=0;

if (\{x,y,z\}>=5)) begin

output 1 = 1'b1;//specify bit

end else if (\{x,y,z\}==3'b101) begin

output 1 = 1'b1;

end

end

```

#### The result of EACH of these lines?

The logic expressed by this truth table:

| x | y | Z | output_1 |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 0        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

<sup>\*</sup> Which can be built using ¼ of 1/33000<sup>th</sup> of our FPGA

There's often more than one way to write a thing in Verilog

#### Now...life hits us

- Theoretical Idea of a digital function is divorced from concept of time, but...

- Everything takes time to occur because of capacitance, non-idealities, the speed of light, etc...:

BIG QUESTION. If you set x,y,z, how long until you see the correct result at the output?

# Delays

- Two big numbers for a Digital Function:

- t<sub>cd</sub>: Contamination Delay: The <u>minimum</u> time it takes from an input change on a function to affect the output of function

- $t_{pd}$ : Propagation Delay: The <u>maximum</u> time it takes from an input change on a function to affect the output of function

- Therefore, when a new input is presented to a digital (combinational function), it will take  $\frac{between}{t_{cd}}$  and  $t_{pd}$  for it to calculate!

- Can also think of these as best/worst case response times

- During  $t_{pd}$  the input must be held stable

# How Many Calculations per second?

We'll often want to feed in one set of inputs and then another and then another and then another, harvesting the outputs as they appear.

- If a module has:

- $t_{cd} = 1$ ns

- $t_{pd} = 5$ ns

- How many calculations can we get per second?

#### Modules

Use modules to compartmentalize/reuse your code:

Then you can make an instance!

#### Modules

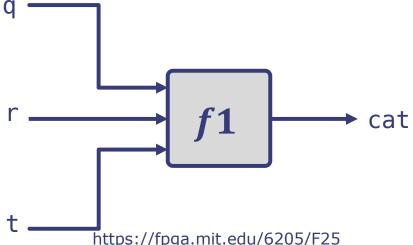

- Use modules to compartmentalize/reuse your code.

- Then you can make an instance:

```

logic q,r,t,cat;

//declare instance of that module:

f1 my_f1(.x(q), .y(r), .z(t), .output_1(cat));

```

Which will build a circuit like this:

September 4, 2025 https://fpga.mit.edu/6205/F25 L01-67

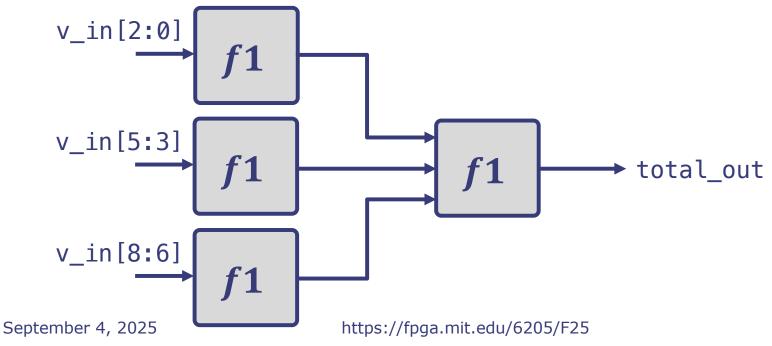

#### And you can build from here

• What if you wanted a majority function of majority functions?

## Majority of Majority

L01-69

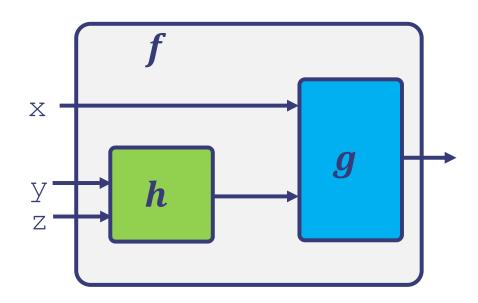

#### As we start to Attach things...

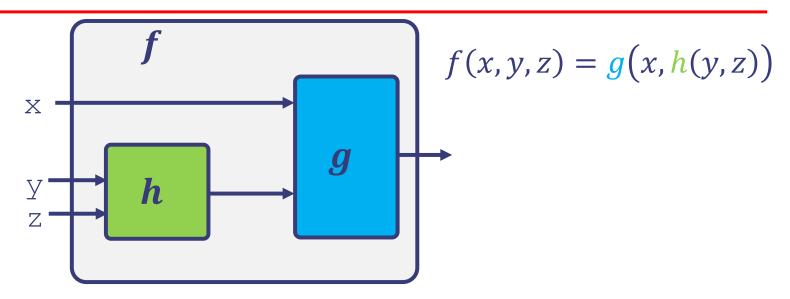

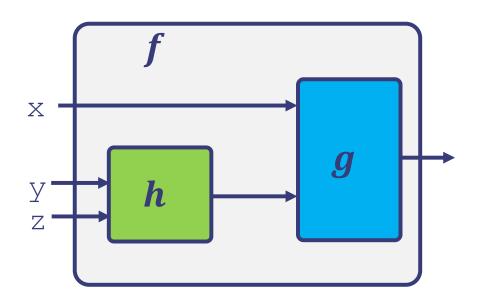

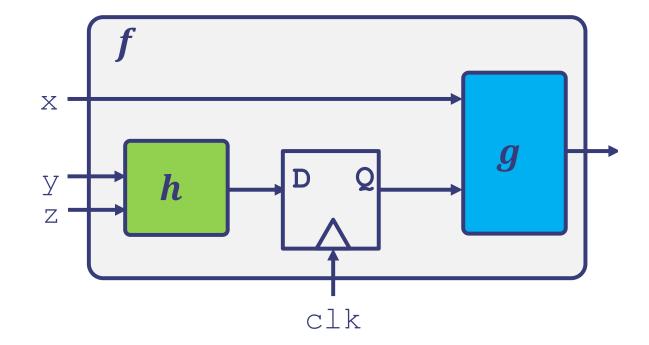

• Functions Driving Functions... f(x, y, z) = g(x, h(y, z))

Any potential problems?

## Delays

- Two big numbers for a Digital Function:

- $t_{cd}$ : Contamination Delay: The <u>minimum</u> time it takes from an input change on a function to appear at output of function

- $t_{pd}$ : Propagation Delay: The <u>maximum</u> time it takes from an input change on a function to appear at output of function

- Therefore, when a new input is presented to a digital (combinational function), it will take  $\frac{between}{t_{cd}}$  and  $t_{pd}$  for it to calculate!

- Can also think of these as best/worst case response times

- During t<sub>pd</sub> the input <u>must</u> be held stable

#### As we start to Attach things...

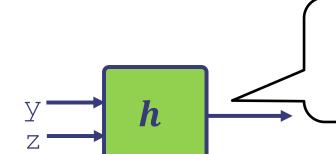

- Function g cannot start calculating its final answer until h has determined its own final answer.

- If h needs  $t_{pdh}$  to calculate and g needs  $t_{pdg}$  that means...

#### System as a Whole?

- The  $t_{pd}$  of the whole system has gone up!

- So the throughput of the whole system has gone down.

- But this is only half the problem.

- The module h is meant to calculate, but we're requiring it to hold its result for the benefit of g.

- That is a waste of its potential

#### How to Fix?

"I need creative freedom to calculate results. Do not *waste my time* by making me hold values for other functions. I'm an artist."

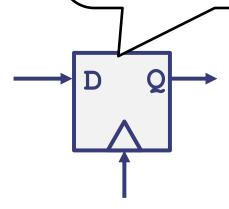

We fix with flip flops

"I am an edge-triggered D flip flip. I will hold your prior result while you calculate the next one. This will help you and lead to a better society overall.

# Fixing function *f*

Make clk a periodic signal

Every so often grab a result from h and hold it

input of g.

Frees up h to calculate at the same time that g is calculating (albeit on different sets of data)

\*Preview/review/spoilerz: this is not a perfect solution...it introduces other issues (we'll spend next few weeks talking about them)

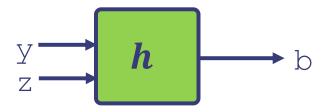

# Originally We had:

• Pure combinational version of the h function:

```

module h (input wire [7:0] y, input wire [7:0] z, output logic b);

always_comb begin

b = y>z;

end

endmodule

```

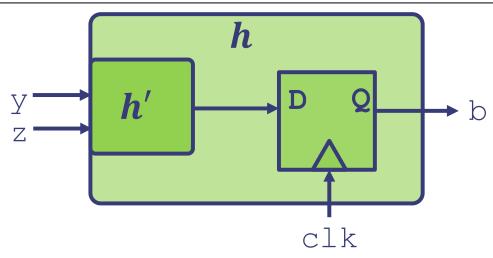

#### Incorporate a Flip Flop in it.

Same logic but put a flip flop on output

```

module h (input wire clk, input wire [7:0] y, input wire [7:0] z, output logic b);

logic b_i;

always_comb begin

b_i = y>z;

end

always_ff @(posedge clk) begin

b <= bi;

end

endmodule</pre>

```

September 4, 2025

https://fpga.mit.edu/6205/F25

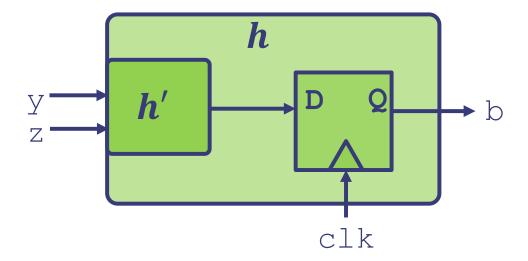

#### Incorporate a Flip Flop in it.

Or said more succinctly...

```

module h (input wire clk, input wire [7:0] y, input wire [7:0] z, output logic b);

always_ff @(posedge clk) begin

b <= y>z;

end

endmodule

```

# One Last Thought for Day 1

- This is glimpse of the digital design situation.

- It is a constant battle against time.

- Worrying about how long a calculation will take

- Making sure no part of your design is wasting time

Meeting timing in your designs will become a key piece of who you are as a person.

#### What's Next

- Get Lab Kit (you can get in office hours starting after 4:15 pm -6:15pm today...or at any office hours with a TA...see calendar...so that's Kiran, Yoland, Monica, or Hasan or Joe)

- Week 1 assignments are out now (on course website). Due next Wednesday September 10 at night at 11:59pm