# 6.205

#### Finite State Machines

### Administrivia

- Week 2 due last night.

- Week 3 out after class today

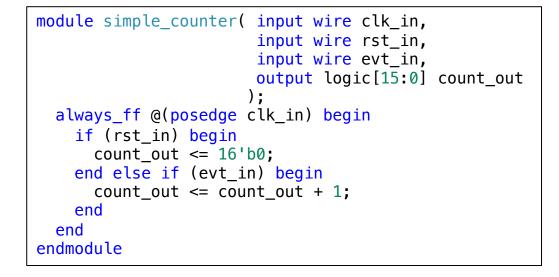

### Cool/Not Cool Bug

• What's wrong with this

```

simple_counter msc(

.clk_in(clk_in),

.rst_in(counter_reset),

.evt_in(clk_in),

.count_out(count));

```

### Clocks Stay with Clocks!

• And Signals stay with signals. None of this stuff:

always\_ff @(posedge some\_button\_thing)begin

x <= 5+x;

//other code

end</pre>

This will not play nice with other circuits that are clocked off an actual clock!

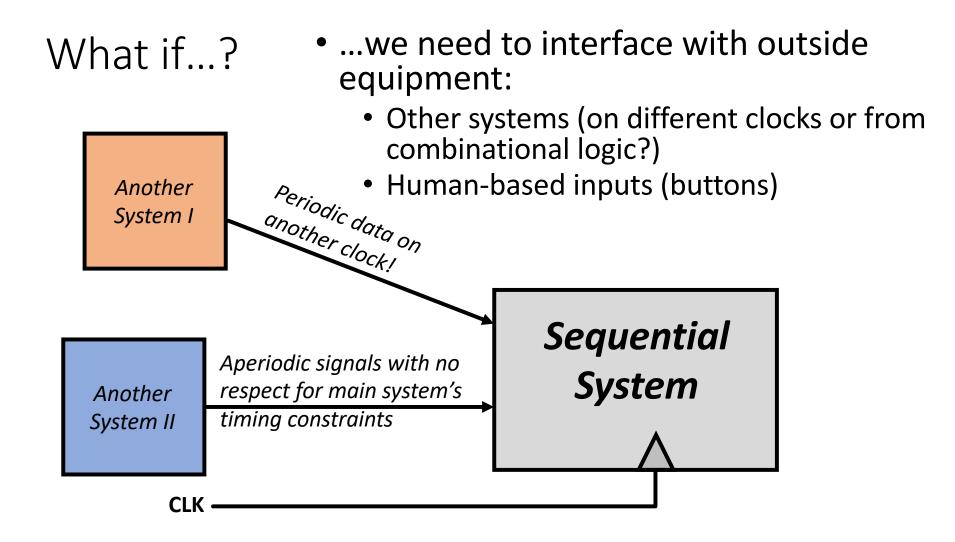

# Interfacing to Sequential Logic

...Or what are the problems with working with Sequential Logic?....

### Huh?

- In Week 3:

- You'll be using these occasionally...

- They build this

```

module synchronizer #(parameter SYNC_DEPTH = 2)

( input wire clk_in,

input wire rst in,

input wire us_in, //unsync_in

output logic s out); //sync out

logic [SYNC_DEPTH-1:0] sync;

always_ff @(posedge clk_in)begin

if (rst in)begin

sync <= {(SYNC_DEPTH){us_in}};</pre>

end else begin

sync[SYNC_DEPTH-1] <= us_in;</pre>

for (int i=1; i<SYNC_DEPTH; i= i+1)begin</pre>

sync[i-1] <= sync[i];</pre>

end

end

end

assign s_out = sync[0];

endmodule

```

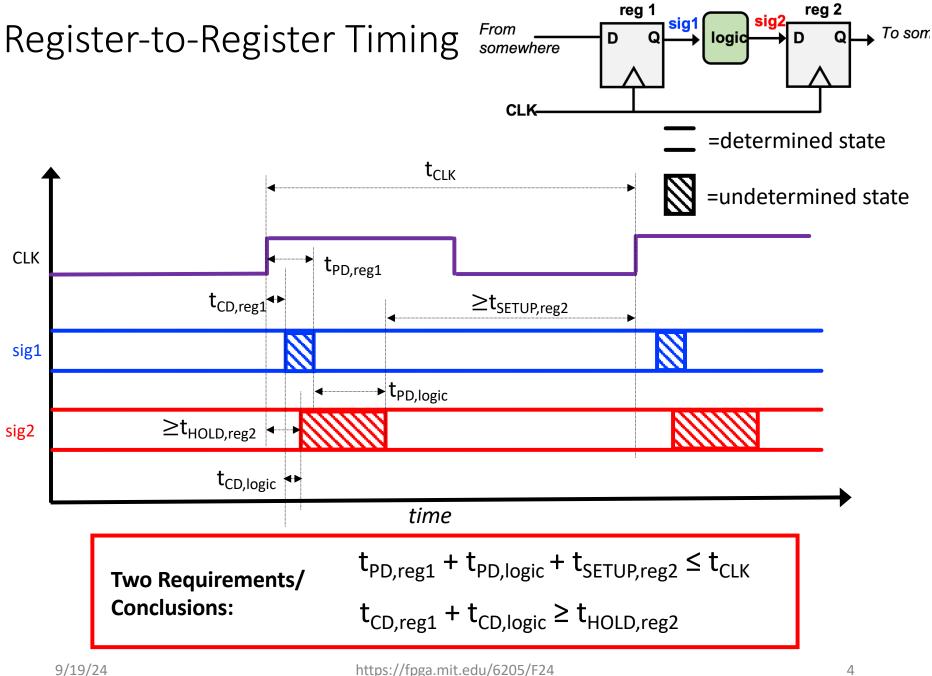

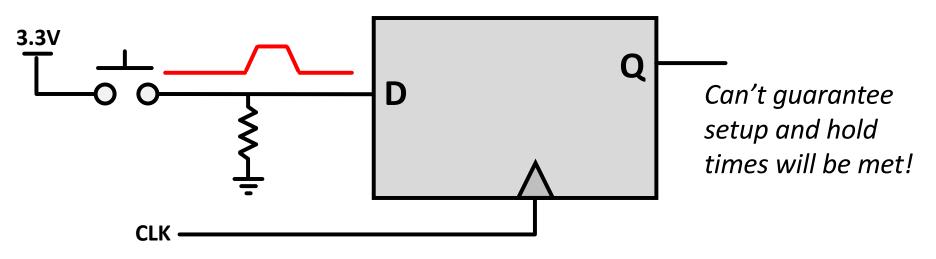

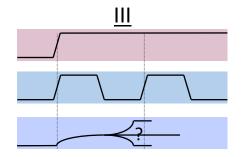

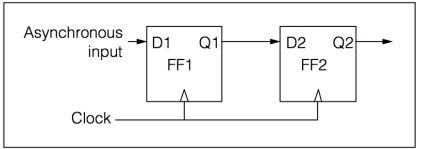

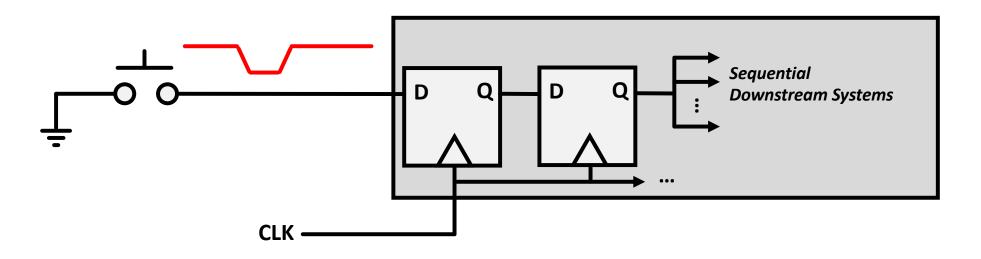

#### Can't guarantee setup and hold times will be met!

Example: Asynchronous Inputs in Sequential Systems

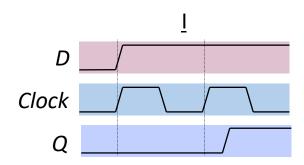

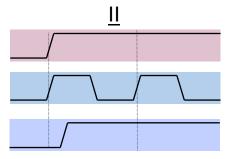

When an asynchronous signal causes a setup/hold violation...

Transition is missed on first clock cycle, but caught on next clock cycle.

Transition is caught on first clock cycle.

Output is metastable for an indeterminate amount of time.

#### **Q: Which cases are problematic?**

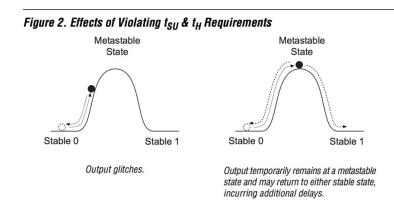

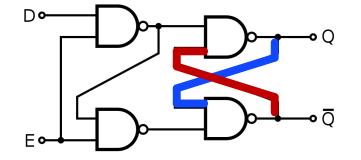

### Metastability

- D-registers have issues with all that feedback and stuff going on. Can go metastable

- Metastability is where the system hovers between Logic High and Logic Low in an unpredictable way

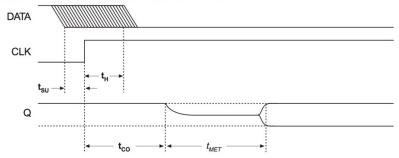

Metastability in Altera (∂) Devices Altera Application Note 42 (1999)

$t_{co}$  = "min time from clock to output" ....think of it as  $t_{pd}$  here (not exactly the same,

9/19/24

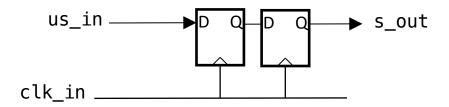

# Handling Metastability

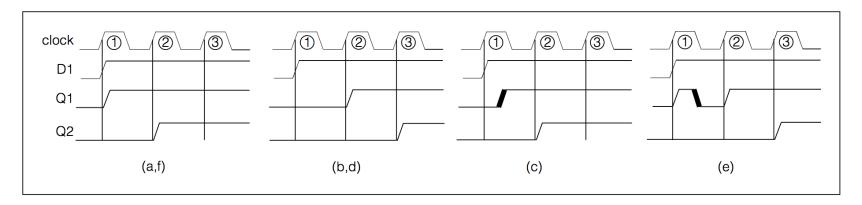

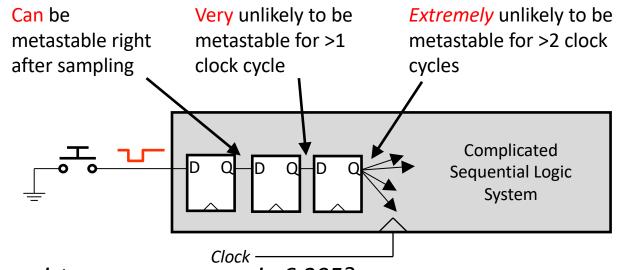

- Can't globally prevent metastability, but can isolate it!

- Stringing several registers together can isolate any freakouts!

Figure 8. Two-flip-flop synchronization circuit.

"Metastability and Synchronizers: A Tutorial" Ran Ginosar, Technion Israel Institute of Technology

### Handling Metastability

- Completely preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- Solution to metastability: allow time for signals to stabilize

How many registers are necessary in 6.205?

- Depends on many design parameters (clock speed, device speeds, ...)

- In 6.205, a pair of synchronization registers is sufficient

- And for simple designs...with low t<sub>pd</sub> you may not even need anything 9/19/24 https://fpga.mit.edu/6205/F24

#### Handling Metastability

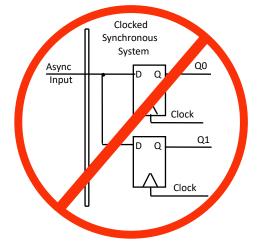

- Don't break off an asynchronous input until it has gone through some registers

- Basically: Ensure that external signals feed <u>exactly one</u> flip-flop chain before branching

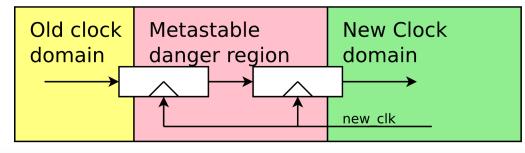

## Related: Clock Domain Crossing

- For example:

- Data gets sent in at 25 MHz from one device (running on its own clock)

- Your system runs at 50 MHz

- 1 //xfer\_pipe can be >2 bits wide (2 is usually fine...3 better)

- 2 always\_ff @(posedge new\_clock)

- 3 { new\_val, xfer\_pipe } <= { xfer\_pipe, i\_val };</pre>

- This only works when original clock domain frequency is less than or equal to new clock domain frequency

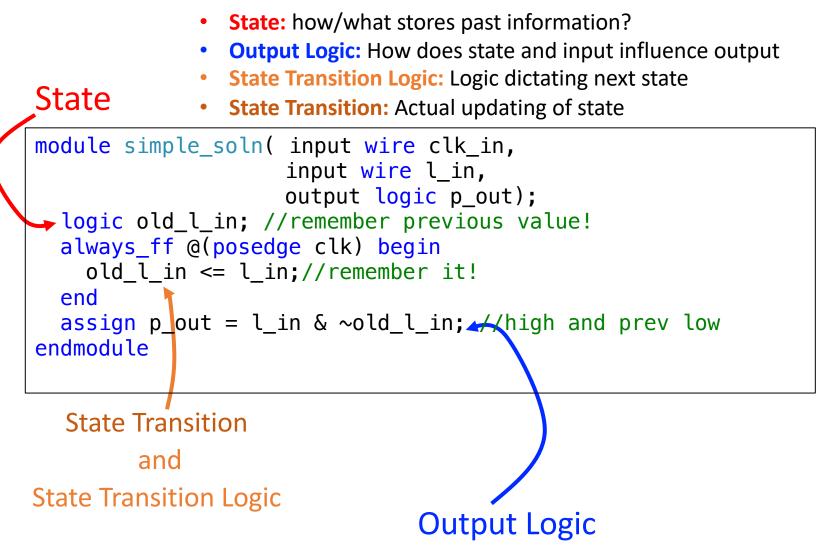

# State Machines

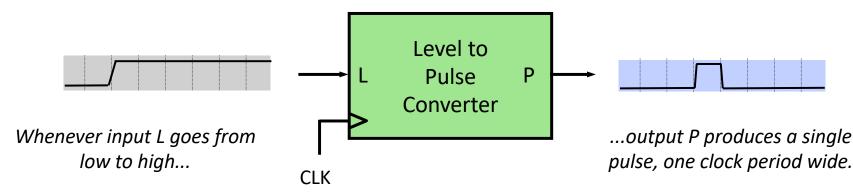

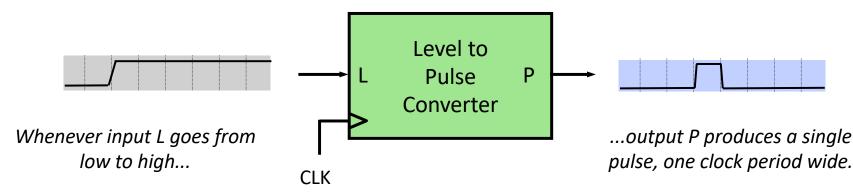

#### Design Example: Level-to-Pulse

- A level-to-pulse converter produces a singlecycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for modules

### Level-to-Pulse

- One simple solution (~from Lab 02)

- One bit positive discrete time positive

• Let's try to formalize this a bit more

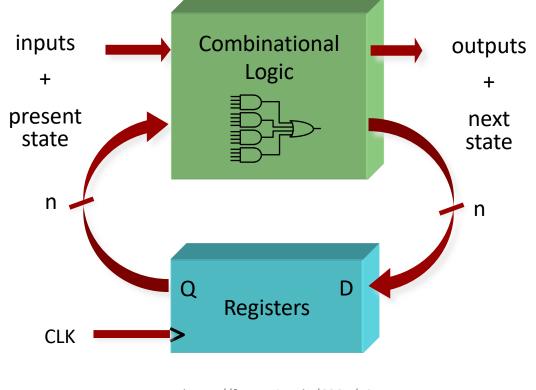

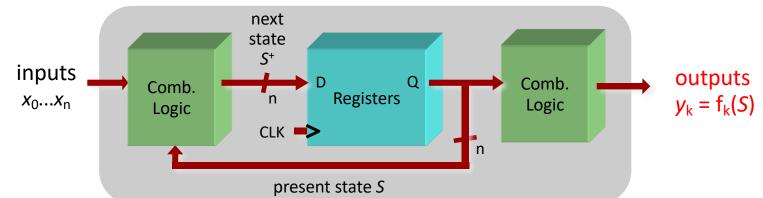

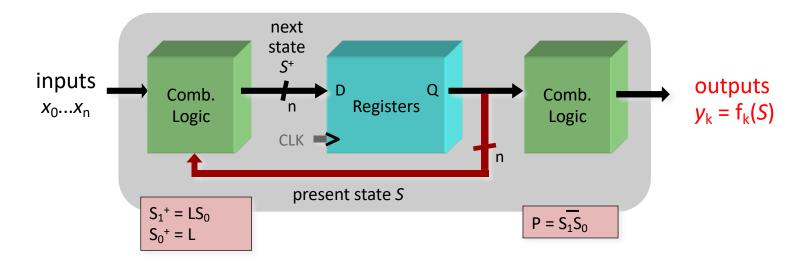

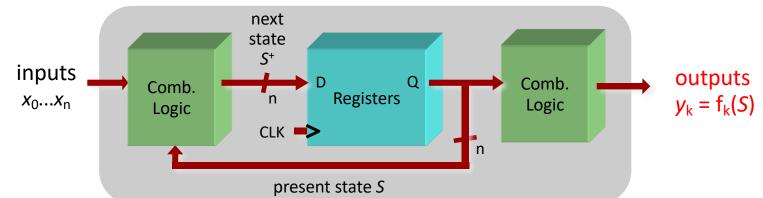

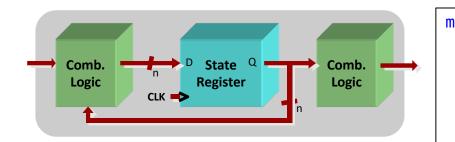

#### Finite State Machines

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state

### Level-to-Pulse

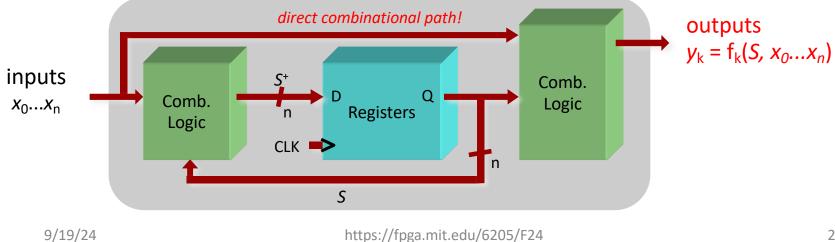

#### Let's Formalize it: Two Types of FSMs

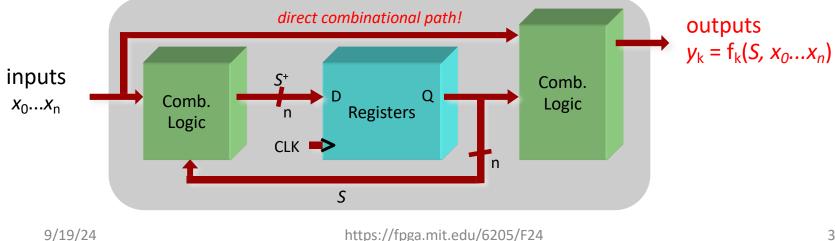

**Moore** and **Mealy** FSMs : different output generation

#### •Mealy FSM:

#### Moore

- Edward F. Moore

- 1925-2003

- Virginia Tech

- Worked with Claude Shannon

- Not same Moore as Moore's Law...that was Gordon Moore from Intel

## Mealy

- George H. Mealy

- 1927-2010

- Harvard, Bell Labs

#### Design Example: Level-to-Pulse

- A level-to-pulse converter produces a singlecycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for modules

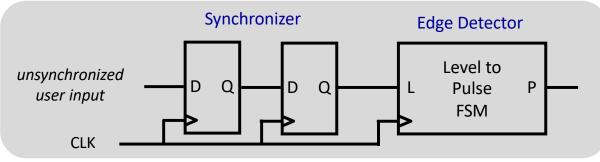

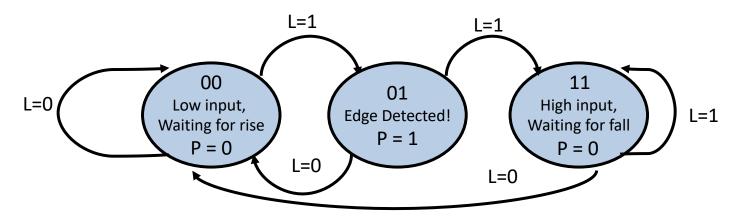

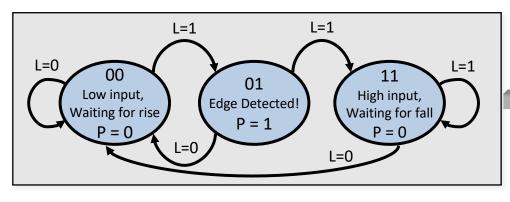

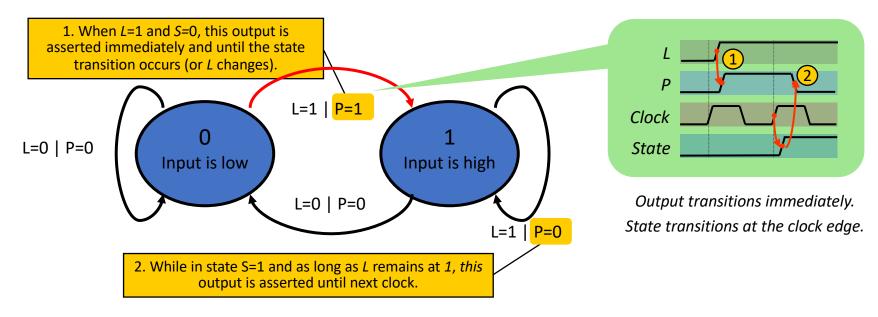

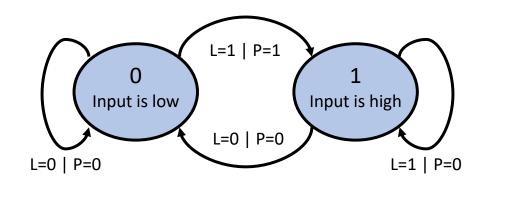

#### Step 1: State Transition Diagram

• Block diagram of desired system:

• State transition diagram is a useful FSM representation and design aid:

https://fpga.mit.edu/6205/F24

#### Valid State Transition Diagrams

- Arcs leaving a state are mutually exclusive, i.e., for any combination input values there's at most one applicable arc

- Arcs leaving a state are collectively exhaustive, i.e., for any combination of input values there's at least one applicable arc\*\*

- So for each state: for any combination of input values there's <u>exactly one</u> applicable arc (no ambiguity)

- Often a starting state is specified

- Each state specifies values for all outputs (in the case of Moore)

#### Choosing State Representation

Choice #1: binary encoding

For N states, use  $ceil(log_2N)$  bits to encode the state with each state represented by a unique combination of the bits. Tradeoffs: most efficient use of state registers, but requires more complicated combinational logic to detect when in a particular state.

Choice #2: "one-hot" encoding

For N states, use N bits to encode the state where the bit corresponding to the current state is 1, all the others 0. Tradeoffs: more state registers, but often much less combinational logic since state decoding is trivial.

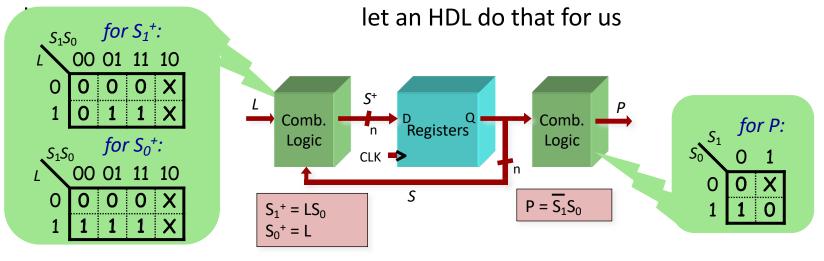

#### Step 2: Logic Derivation

Transition diagram is readily converted to a state transition table (just a truth table)

| Curi<br>Sta | rent<br>ate           | In | Next<br>State                      |                                    | Out |

|-------------|-----------------------|----|------------------------------------|------------------------------------|-----|

| <b>S</b> 1  | <b>S</b> <sub>0</sub> | L  | <i>S</i> <sub>1</sub> <sup>+</sup> | <b>S</b> <sub>0</sub> <sup>+</sup> | Р   |

| 0           | 0                     | 0  | 0                                  | 0                                  | 0   |

| 0           | 0                     | 1  | 0                                  | 1                                  | 0   |

| 0           | 1                     | 0  | 0                                  | 0                                  | 1   |

| 0           | 1                     | 1  | 1                                  | 1                                  | 1   |

| 1           | 1                     | 0  | 0                                  | 0                                  | 0   |

| 1           | 1                     | 1  | 1                                  | 1                                  | 0   |

• Combinational logic *could* be derived using Karnaugh maps by hand,

9/19/24

https://fpga.mit.edu/6205/F24

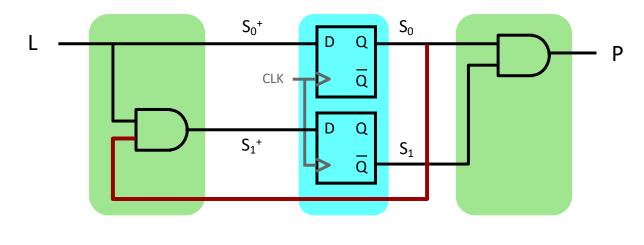

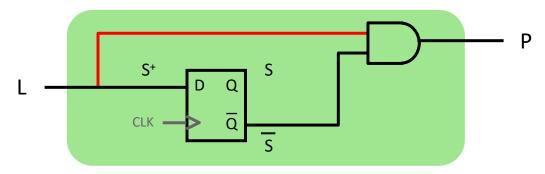

#### Moore Level-to-Pulse Converter

Moore FSM circuit implementation of level-to-pulse converter:

# Moore Level-to-Pulse Converter (SystemVerilog)

An example of a very explicit

Moore FSM

implementation

of the level-to pulse converter:

```

module moore fsm( input wire clk in,

input wire l in,

output logic p out);

localparam LOW WAITING = 2'b0; //define your states as...

localparam EDGE DETECTED = 2'b01; //parameters for easy...

localparam HIGH WAITING = 2'b10; //reading!

logic [1:0] state; //contain state!

logic [1:0] next state; //hold next state!

//Output Logic:

always comb begin

case(state)

LOW WAITING: p out = 1'b0; //output based only on...

EDGE_DETECTED: p_out = 1'b1; //current state! This is...

HIGH WAITING: p out = 1'b0; //a characteristic of Moore FSM

default: p out = 1'b0;

endcase

end

//State Transition Logic (Combinational):

always comb begin

case(state) //Also consider explicit if/elses

LOW WAITING: next state = l in?EDGE DETECTED:LOW WAITING;

EDGE DETECTED: next state = l in?HIGH WAITING:LOW WAITING;

HIGH_WAITING: next_state = l_in?HIGH_WAITING:LOW_WAITING;

default: next state = LOW WAITING;

endcase

end

//State Transition

always ff @(posedge clk in) begin

//consider adding a reset here as well!

state <= next state; //state becomes calculated next state</pre>

end

endmodule

```

### Moore Level-to-Pulse Converter (SystemVerilog)

- Merging State

Transition Logic and

State Transition into

one block

- Some people like this more (me)

```

module moore fsm( input wire clk in,

input wire l in,

output logic p out);

localparam LOW_WAITING = 2'b0;

localparam EDGE DETECTED = 2'b01;

localparam HIGH WAITING = 2'b10:

logic [1:0] state;

//Output Logic:

always_comb begin

case(state)

LOW_WAITING: p_out = 1'b0;

EDGE DETECTED: p out = 1'b1;

HIGH WAITING: p out = 1'b0;

default: p out = 1'b0; //default

endcase

end

//State Transition and Logic:

always ff @(posedge clk in) begin

//consider adding a reset here as well!

case(state)

LOW WAITING: state <= l in?EDGE DETECTED:LOW WAITING;

EDGE DETECTED: state <= l in?HIGH WAITING:LOW WAITING;</pre>

HIGH WAITING: state <= l in?HIGH WAITING:LOW WAITING;</pre>

default: state <= LOW WAITING;</pre>

endcase

end

endmodule

```

#### Design of a Mealy Level-to-Pulse

Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations

#### Mealy Level-to-Pulse Converter

| Pres.<br>State | In | Next<br>State | Out |

|----------------|----|---------------|-----|

| S              | L  | S⁺            | Р   |

| 0              | 0  | 0             | 0   |

| 0              | 1  | 1             | 1   |

| 1              | 1  | 1             | 0   |

| 1              | 0  | 0             | 0   |

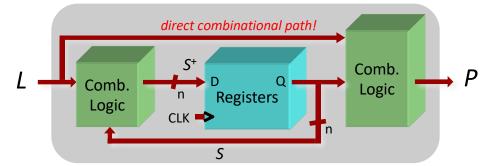

Mealy FSM circuit implementation of level-to-pulse converter:

- FSM's state simply remembers the previous value of L

- Circuit benefits from the Mealy FSM's implicit single-cycle assertion of outputs during state transitions

## Mealy Level-to-Pulse Converter (SystemVerilog)

An example of a very explicit

Mealy FSM

implementation

of the level-to pulse converter:

```

module mealy fsm( input wire clk in,

input wire l in,

output logic p out);

localparam LOW WAITING = 1'b0; //define states but notice...

localparam HIGH WAITING = 1'b1; //fewer needed...Mealy usually...

//though not always, is like that

logic state; //state (smaller than before...only two states to rep)

logic next state;

//Output Logic:

always comb begin

case(state) //outputs are based on state AND inputs!

LOW WAITING: p out = l in?1'b1:1'b0;

HIGH WAITING: p \text{ out} = 1'b0;

default: p_out = 1'b0; //default

endcase

end

//State Transition Logic:

always_comb begin

case(state)

LOW_WAITING: next_state = l_in?HIGH_WAITING:LOW_WAITING;

HIGH_WAITING: next_state = l_in?HIGH_WAITING:LOW_WAITING;

default: next state = LOW WAITING;

endcase

end

//State Transition

always_ff @(posedge clk_in) begin

//consider adding a reset here as well (same goes for any...

//clocked logic block)

state <= next state;</pre>

end

endmodule

```

### Mealy Level-to-Pulse Converter (SystemVerilog)

• Merging **State**

Transition Logic and State Transition into one block

```

module mealy fsm( input wire clk in,

input wire l in,

output logic p out);

localparam LOW WAITING = 1'b0;

localparam HIGH WAITING = 1'b1;

logic state:

//Output Logic:

always_comb begin

case(state)

LOW WAITING: p out = l in?1'b1:1'b0;

HIGH_WAITING: p_out = \overline{1}'b0;

default: p out = 1'b0; //default

endcase

end

//State Transition and Transition Logic!

always_ff @(posedge clk_in) begin

//consider adding a reset here as well!

case(state)

LOW WAITING: state <= l in?HIGH WAITING:LOW WAITING;

HIGH WAITING: state <= l in?HIGH WAITING:LOW WAITING;</pre>

default: state <= LOW WAITING;</pre>

endcase

end

endmodule

```

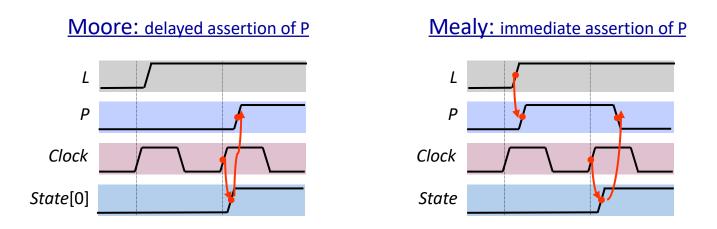

### Moore/Mealy Trade-Offs

- How are they different?

- Moore: outputs = f( state ) only

- Mealy outputs = f( state and input )

- Mealy outputs generally occur <u>one cycle earlier</u> than a Moore:

- Compared to a Moore FSM, a Mealy FSM *might*...

- Be more difficult to conceptualize and design (both at circuit level and in HDL)

- Have fewer states

- Be expressed using fewer lines of Verilog

### Moore/Mealy Trade-Offs

- Moore:

- Usually more states

- Each state has a particular output

- Mealy:

- Fewer states, outputs are specified on edges of diagram

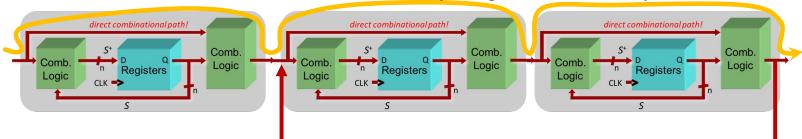

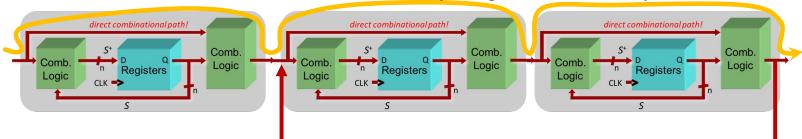

- Potential Dangers:

Really-long combinatorial paths!

Possible cyclic logic paths Combinatorial logic driving itself asynchronously through really hard-to-debug pathways!

#### Let's Formalize it: Two Types of FSMs

**Moore** and **Mealy** FSMs : different output generation

#### •Mealy FSM:

### Moore/Mealy Trade-Offs

- Moore:

- Usually more states

- Each state has a particular output

- Mealy:

- Fewer states, outputs are specified on edges of diagram

- Potential Dangers:

Really-long combinatorial paths!

Possible cyclic logic paths Combinatorial logic driving itself asynchronously through really hard-to-debug pathways!

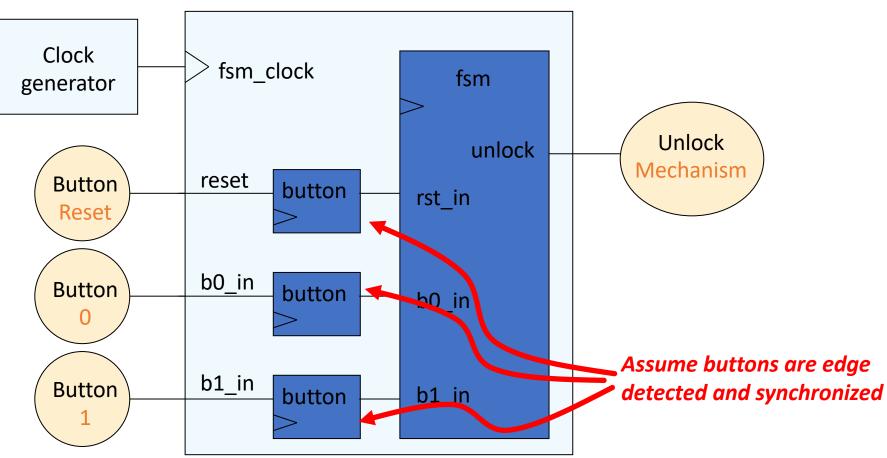

# FSM Examples

Time-Dependent

### FSM Example

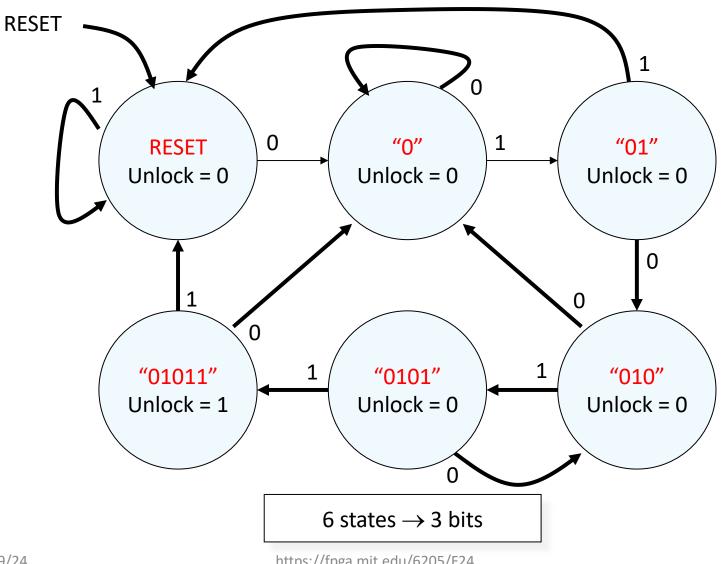

#### GOAL:

- Build an electronic combination lock with a reset button, two number buttons (0 and 1), and an unlock output signal. The combination will **always be 01011**.

- We will encode the lock into the state.

- Use a sliding window of the last five entries

RESET

$$\longrightarrow$$

$(0^{\prime\prime}) \longrightarrow$   $(1^{\prime\prime}) \longrightarrow$   $(1^{\prime\prime$

#### STEPS:

- 1. Design lock FSM (block diagram, state transitions)

- 2. Write SystemVerilog module(s) for FSM

# Step 1A: Block Diagram

lock

Step 1B: State transition diagram

9/19/24

#### Step 2: Write Verilog

# Step 2B: state transition diagram

```

localparam S RESET = 0; parameter S 0 = 1; // state assignments

localparam S_01 = 2; parameter S 010 = 3;

localparam S 0101 = 4; parameter S 01011 = 5;

logic [2:0] state, next state; //(both 3 bits wide)

always comb begin // implement state transition diagram

if (rst in) next state = S RESET;

else begin

case (state)

S RESET: next state = b0 in ? S 0 : b1 in ? S RESET : state;

S 0: next state = b0 in ? S 0 : b1 in ? S 01 : state;

S 01: next state = b0 in ? S 010 : b1 in ? S RESET : state;

S 010: next state = b0 in ? S 0 : b1 in ? S 0101 : state;

S 0101: next state = b0 in ? S 010 : b1 in ? S 01011 : state;

S 01011: next state = b0 in ? S 0 : b1 in ? S RESET : state;

default: next state = S RESET; // handle unused states

endcase

end

end

```

#### Step 2C: generate output

// it's a Moore machine! Output only depends on current state

assign unlock\_out = (state == S\_01011); // assign output: Moore machine

#### Step 2: final Verilog implementation

```

module lock(input wire clk in,rst in,b0 in,b1 in,

output logic unlock out);

localparam S RESET = 0; parameter S 0 = 1; // state assignments

localparam S 01 = 2; parameter S 010 = 3;

localparam S 0101 = 4; parameter S 01011 = 5;

logic [2:0] state. next state: //(both 3 bits wide)

always comb begin // implement state transition diagram

if (rst in) next state = S RESET;

else begin

case (state)

S_RESET: next_state = b0_in ? S_0 : b1_in ? S_RESET : state;

S 0: next state = b0 in ? S 0 : b1 in ? S 01 : state;

S 01: next state = b\bar{0} in ? S 010 : b\bar{1} in ? S RESET : state;

S 010: next state = b0 in ? S 0 : b1 in ? S 0101 : state;

S 0101: next state = b0 in ? S 010 : b1 in ? S 01011 : state;

S 01011: next state = b0 in ? S 0 : b1 in ? S RESET : state;

default: next state = S RESET; // handle unused states

endcase

end

end

always_ff @(posedge clk) state <= next_state;</pre>

assign unlock out = (state == S 01011); // assign output: Moore machine

endmodule

```

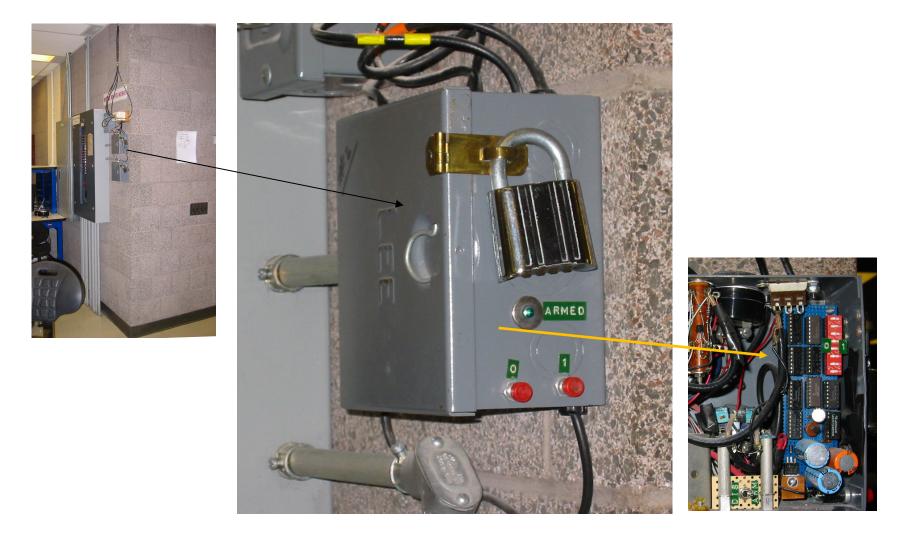

#### Real FSM Security System

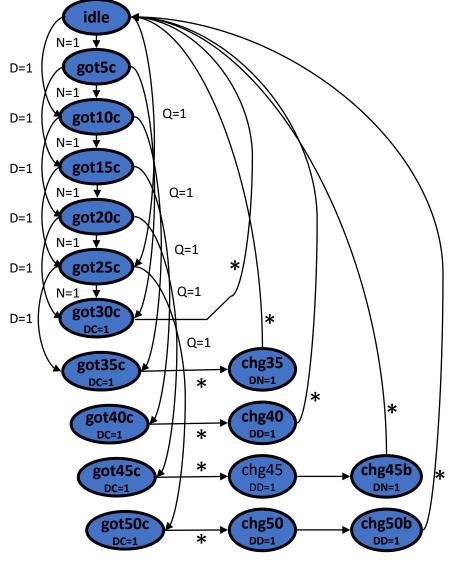

# The 6.111 Vending Machine (example from circa 2000...slightly updated)

- Lab assistants demand a new soda machine for the 6.111 lab. You design the FSM controller.

- All selections are \$0.30.

- The machine makes change. (Dimes and nickels only.)

- Inputs: limit 1 per clock

- Q quarter inserted

- D dime inserted

- N nickel inserted

- Outputs: limit 1 per clock

- DC dispense can

- DD dispense dime

- DN dispense nickel

#### What States are in the System?

• A starting (idle) state:

• A state for each possible amount of money captured:

• What's the maximum amount of money captured before purchase? 25 cents (just shy of a purchase) + one quarter (largest coin)

... got35c got40c got45c got50c

• States to dispense change (one per coin dispensed):

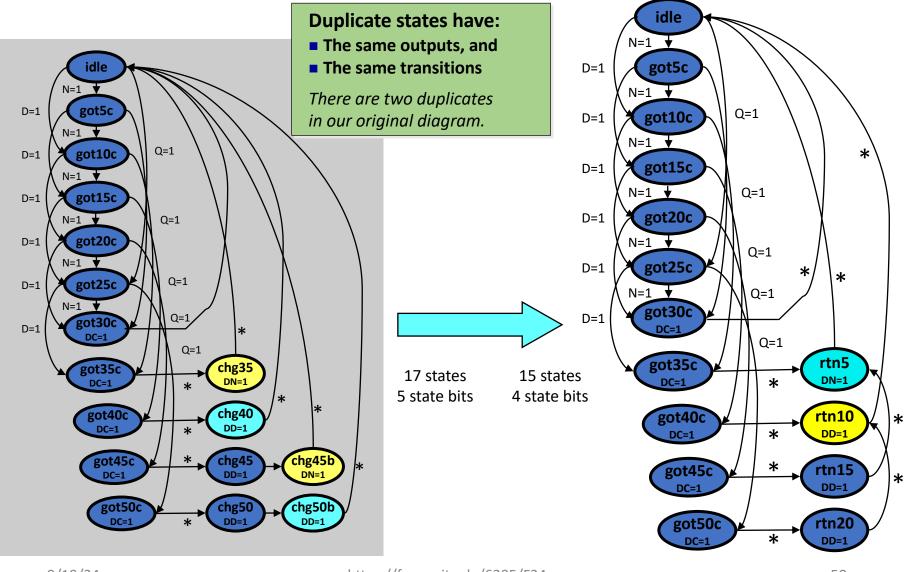

#### A Moore Vender

*Here's a first cut at the state transition diagram.*

#### State Reduction

9/19/24

https://fpga.mit.edu/6205/F24

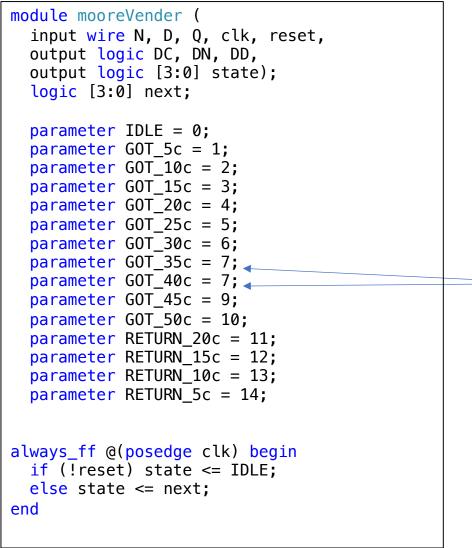

#### Verilog for the Moore Vender

States defined with parameter keyword

State register (sequential always block)

```

So

triggered

on posedge

clock

```

- Next-state cloc

combinational logic

(comb. always block with case)

- Output combinational logic block (comb. always block or assign statements)

State register defined with sequential always block (always\_ff)

```

module mooreVender (

input wire N, D, Q, clk, reset,

output logic DC, DN, DD,

output logic [3:0] state);

logic [3:0] next;

parameter IDLE = 0;

parameter GOT 5c = 1;

parameter GOT 10c = 2;

parameter GOT 15c = 3:

parameter GOT 20c = 4;

parameter GOT 25c = 5:

parameter GOT 30c = 6;

parameter GOT 35c = 7;

parameter GOT 40c = 7;

parameter GOT 45c = 9;

parameter GOT 50c = 10;

parameter RETURN 20c = 11;

parameter RETURN 15c = 12;

parameter RETURN 10c = 13;

parameter RETURN 5c = 14;

always ff @(posedge clk) begin

if (!reset) state <= IDLE:</pre>

else state <= next;</pre>

end

```

9/19/24

## Enums in SystemVerilog

Same value...uh oh

## Enums in SystemVerilog

```

module mooreVender (

input wire N, D, Q, clk, reset,

output logic DC, DN, DD,

output logic [3:0] state_out);

enum {IDLE,GOT_5c,GOT_10c,GOT_15c,GOT_20c,

GOT_25c,GOT_35c,GOT_40c,GOT_45c,

GOT_50c,RETURN_20c,RETURN_15c,

RETURN_10c,RETURN_5c } state, next;

assign state_out = state;

always_ff @(posedge clk or negedge reset)begin

if (!reset) state <= IDLE;

else state <= next;

end</pre>

```

- State and next\_State are now restricted to only be one of a set of values

- Vivado figures out the most efficient encoding

- Ensures you don't make duplicates or do other stupid mistakes

typedef enum {IDLE,GOT\_5c,GOT\_10c,GOT\_15c,GOT\_20c, GOT\_25c,GOT\_35c,GOT\_40c,GOT\_45c, GOT\_50c,RETURN\_20c,RETURN\_15c, RETURN\_10c,RETURN\_5c } coin\_state;

coin\_state state, next; //instances here

#### Next-state logic within a combinational always block

```

always comb (state or N or D or Q) begin

case (state)

IDLE: if (0) next = GOT 25c;

else if (D) next = GOT 10c:

else if (N) next = GOT 5c;

else next = IDLE;

GOT 5c: if (0) next = GOT 30c;

else if (D) next = GOT 15c:

else if (N) next = GOT 10c:

else next = GOT 5c;

GOT 10c: if (0) next = GOT 35c;

else if (D) next = GOT 20c;

else if (N) next = GOT_15c;

else next = GOT 10c;

GOT 15c: if (0) next = GOT 40c:

else if (D) next = GOT_25c;

else if (N) next = GOT 20c;

else next = GOT 15c:

GOT 20c: if (Q) next = GOT 45c;

else if (D) next = GOT 30c;

else if (N) next = GOT 25c;

else next = GOT 20c;

GOT 25c: if (Q) next = GOT 50c;

else if (D) next = GOT_35c;

else if (N) next = GOT 30c;

else next = GOT 25c:

GOT 30c: next = IDLE;

GOT 35c: next = RETURN 5c;

GOT 40c: next = RETURN 10c;

GOT 45c: next = RETURN 15c;

GOT 50c: next = RETURN 20c:

RETURN 20c: next = RETURN 10c;

RETURN_15c: next = RETURN_5c;

RETURN 10c: next = IDLE;

RETURN 5c: next = IDLE:

default: next = IDLE;

endcase

end

```

### Verilog for the Moore Vender

#### **Combinational** output assignment

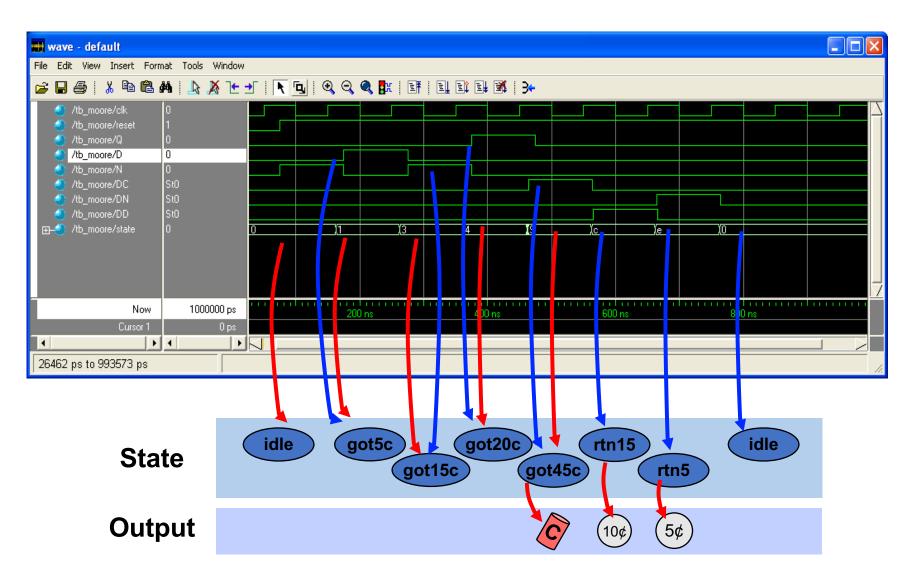

#### Simulation of Moore Vender

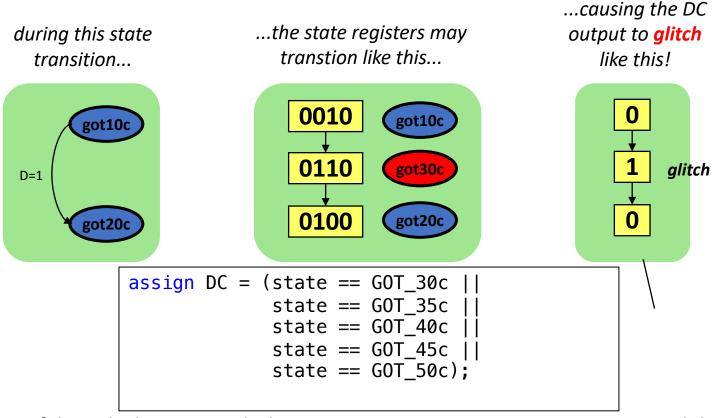

#### FSM Output Glitching

- FSM state bits may not transition at precisely the same time

- Combinational logic for outputs may contain hazards/glitches

- Result: your FSM outputs may glitch!

If the soda dispenser is glitch-sensitive, your customers can get a 20-cent soda!

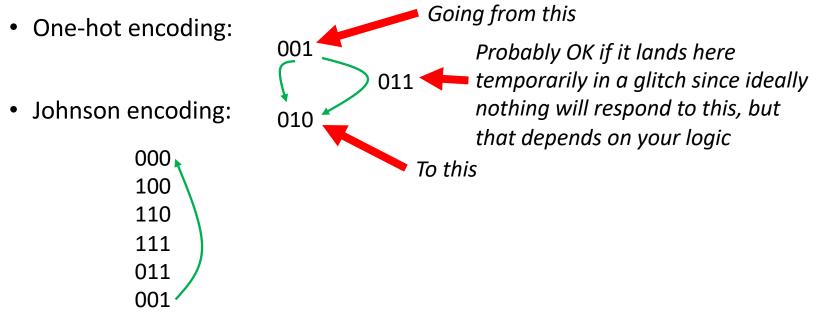

# One way to fix Glitches:

- Don't have to have state 3 (3'b011) go into state 4 (3'b100). Use different state naming/use different numbers!!! A rose by any other name would smell as sweet

- Perhaps a Gray code (??):

- Count up like: 000, 001, 011, 010, 110, 111, 101, 100, ...

- Have the really important/glitch-sensitive states only require transitions of one bit

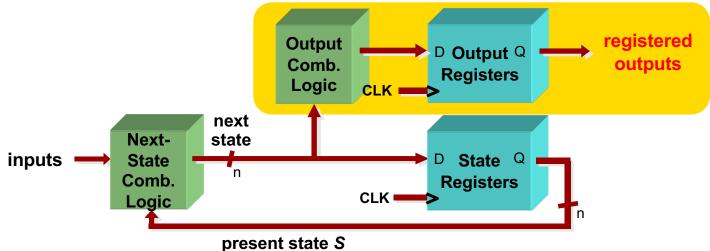

#### Another Solution: Registered FSM Outputs are Glitch-Free

- Move output generation into the sequential always block

- Calculate outputs based on <u>next</u> state

- Delays outputs by one clock cycle. Problematic in some application.

```

always_ff @(posedge clk) begin

if (!reset) state <= IDLE;

else if (clk) state <= next;

DC <= (next == GOT_30c || next == GOT_35c ||

next == GOT_40c || next == GOT_45c ||

next == GOT_50c);

DN <= (next == RETURN_5c);

DD <= (next == RETURN_20c || next == RETURN_15c ||

next == RETURN_10c);

end

```

Note this is inside an edged always with non-blocking assigns! This will synthesize to registered outputs!

# Encoding with Enums?

Generally in SystemVerilog, an enum, unless specified will be 0, 1, 2, 3, etc...

> enum {IDLE,GOT\_5c,GOT\_10c,GOT\_15c,GOT\_20c, GOT\_25c,GOT\_35c,GOT\_40c,GOT\_45c, GOT\_50c,RETURN\_20c,RETURN\_15c, RETURN\_10c,RETURN\_5c } state, next;

- When synthesizing, Vivado may decide on a different encoding, however!

- May or may not be what you want! Or you want a particular encoding

state\_enc\_T state, next;

# Encoding in Enums?

• If want one-hot do:

(\* fsm\_encoding ="one\_hot" \*) state\_enc\_T state, next;

Can also do specify sequential, johnson, gray encoding, etc... or you can specify your own if you have a good idea: Division (an example of an algorithm that takes an unknown amount of time)

```

def divider (dividend, divisor):

count = 0

if divisor==0:

return -1

while dividend>=divisor:

dividend -= divisor

count += 1

return (count, dividend)

```

Super efficient divider \s

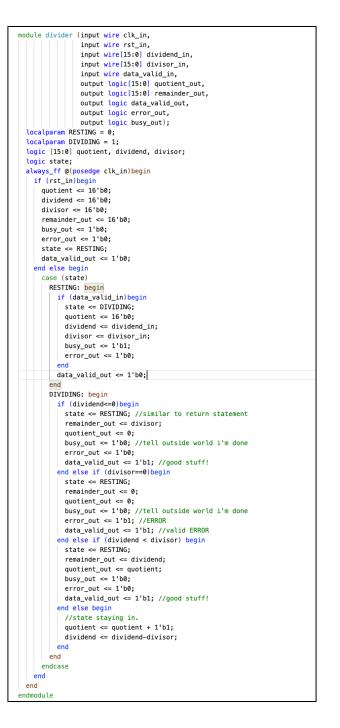

## A Divider

- This is a Verilog FSM example of the algorithm on the previous page which will run an unknown number of times given a set of inputs

- This is how the functionality of a while loop could be developed in your modules

• Will not handle negative, or 0 or other things...

Code on the site's lecture page